LDPC—RCM—OFDM通信系统平台设计与实现

摘 要 随着无线通信技术发展,通信系统硬件平台不仅要求具有极强的处理能力以满足实时快速的算法实现要求,同时也需支持多种无线环境的应用。因此,如何快速而灵活的实现实际无线通信系统具有重要的意义。本文提出一种基于FPGA为核心的无线通信硬件平台,该平台能够方便完成数字基带信号处理、通信信号处理算法的硬件实现以及DA/AD控制和射频模块配置等工作。我们还设计了高速的DA/AD子板,用以连接FPGA和宽带射频子板,从而实现快速无线通信系统的搭建。最后,通过软硬件模块化设计和调试,完成了基于LDPC-RCM-OFDM通信系统验证。结果表明该硬件平台具有较强的信号处理能力和快速而灵活的通信系统实现能力。

【关键词】速率兼容调制 正交频分复用技术 硬件平台

1 引言

正交频分复用技术(OFDM)作为当前和未来移动通信的关键技术之一,已广泛应用于现代数字通信系统中。OFDM具有允许各子载波分别使用不同调制模式的优越性、较高的频带利用率、较强的抗衰落和符号间干扰能力。基于速率兼容调制(RCM)自适应传输技术能够有效提高频率效率,且能在较宽的信道范围内获得光滑的速率调整[1]。因此,将OFDM与基于RCM的自适应调制相结合具有良好的应用前景。同时,实际无线时变信道往往会遭遇突发干扰和深衰落,从而导致很高的误码率,为建立起高速可靠的通信链路,还需利用信道编码以克服信道的噪声、衰落和突发干扰。而低密度奇偶校验码(LDPC)被证明有着优异的纠错性能,并且LDPC码在性能分析、解码运算复杂度、构造方法以及硬件实现上具有诸多优势[2]。

因此,基于LDPC-RCM-OFDM的通信系统将能够充分利用各自优势,在有效提高频谱效率的同时具有较强抗突发干扰和衰落的能力。为对该系统性能进行快速验证,本文设计了一种LDPC-RCM-OFDM硬件验证平台,该平台以ML605 FPGA开发板为核心,完成数字基带信号处理、RCM解调和LDPC解码,实现对高速AD\DA子板的控制,并采用通用软件无线电[3](USRP)的宽带射频子板WBX构建实际无线通信链路。由于采用高性能的FPGA和模块化的硬件结构,本实验平台具有较强的信号处理能力和快速灵活搭建实际无线通信系统特点。该硬件平台还可以为其他无线通信系统提供基于软件无线电方式的快速实现和验证。

2 硬件平台设计

2.1 系统总体概述

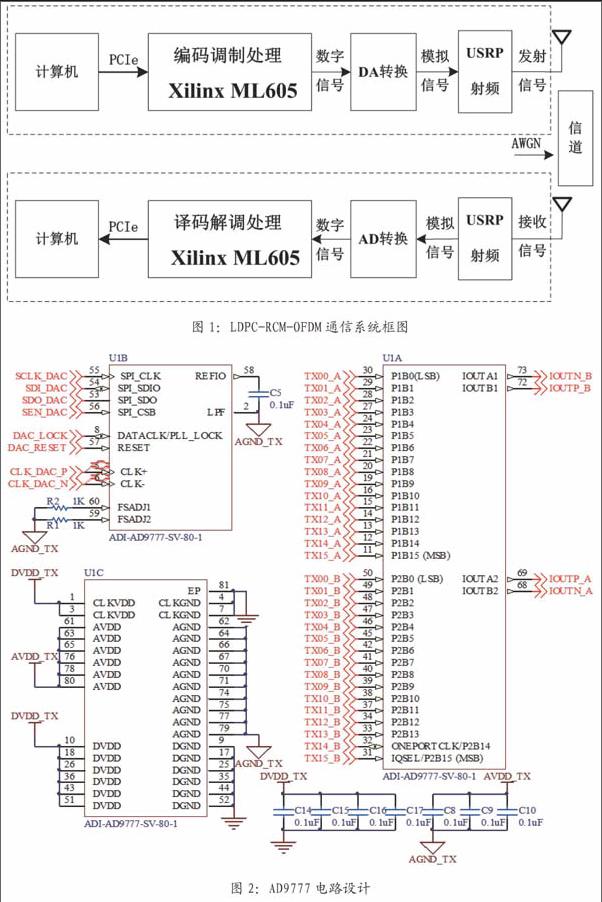

本文提出的LDPC-RCM-OFDM通信系统验证平台框图如图1所示,该平台主要包含基带处理模块、DA/AD转换模块、射频模块三部分。其中Xilinx公司的ML605 FPGA开发平台主要进行基带处理和通信信号算法实现;射频前端模块完成无线信号的收发;高速DA/AD子板将FPGA和宽带射频子板连接以快速搭建完整的实际无线通信系统;计算机完成数据产生、接收、误码检测和内存分配,PC机通过PCIe接口与FPGA板进行通信。

2.2 基带处理模块

硬件平台以ML605FPGA开发板为核心,该平台具有高性能的逻辑和数字信号处理能力、可外扩2GB容量DDR3 SODIMM存储器、支持X8通道PCIe总线接口、可外挂程序和数据固化功能的32MB FLASH、千兆以太网接口、支持FMC连接器扩展接口。FPGA芯片为XC6VSX240T,富含丰富硬件乘法资源、逻辑资源和高速串行接口和总线,非常适合进行高性能的无线通信产品开发。

FPGA主要完成数字基带信号处理、通信信号处理算法的硬件实现。发送信息经分组、编码、交织、映射调制、串/并转换、IFFT、插入循环前缀CP,最后经DA数模转换后通过射频板发射。接收信号的数据处理为发射过程的逆过程,将接收到的信息解调译码,得到基带信号,这里不再详细论述。

2.3 DA/AD处理模块

发送端需要对数字基带信号进行DA转换,得到I/Q两路模拟信号,然后通过射频前段上变频和滤波处理并发射。DA输出控制采用AD公司生产的16bit/160M数模转换器AD9777,其在通信、数字调制、3G、宽带无线等领域得到了广泛的应用,芯片主要包括I/Q通道数据接口模块、数字调制模块、锁相环时钟模块、内插滤波器模块和SPI数据控制接口。图2为AD9777电路详细设计方案。

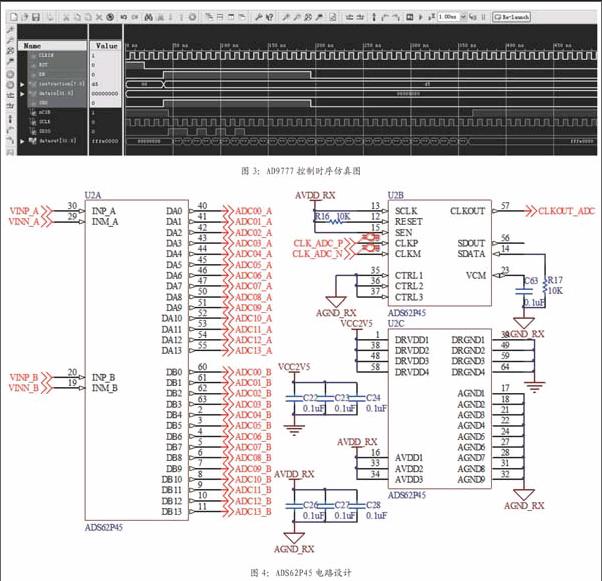

FPGA通過SPI接口对AD9777控制寄存器进行配置,片选CSB拉低以后开始通信,在时钟SCLK的上升沿,芯片通过SDIO写入数据到SPI控制器,SCLK的下降沿,芯片通过SDIO读取寄存器数据,CSB上升沿结束通信并将数据写入相应的寄存器实现芯片功能的配置。输入数据在参考时钟CLK+/-的上升沿写入数据端口P1和P2,实现模拟电压输出。我们通过Verilog HDL语言完成AD9777的控制逻辑设计,并通过仿真以验证程序是否满足AD9777控制时序,仿真结果如图3所示。

从图3的可以看出,仿真结果完全满足SPI的控制时序。随后我们还在FPGA上进行硬件测试,硬件测试结果表明,完全可以实现对AD9777的准确控制。

接收端通过射频前段下变频和滤波处理后,需要对接收到的模拟信号进行AD转换,得到数字信号,再进行基带处理和解调解码。本设计中ADC芯片选用TI公司的14bit/125M模数转换器ADS62P45,其主要应用于无线通信、软件无线电、Wimax等领域。该芯片控制电路简单,仅需通过检测SCLK、SEN、CTRL[1:3]引脚电压确定ADC工作模式,如外部/内部参考、DDR LVDS/CMOS输出、数据格式以及掉电模式等。

参考芯片手册,本文采用并行模式、CMOS电平、二进制补码输出,该模式下,SCLK和SEN引脚接AVDD,SDATA引脚下拉,RESET引脚则上拉,输入差分时钟CLKP/M,ADC芯片即可实现模拟信号数字化。ADS62P45详细设计电路如图4所示。

2.4 射频模块

射频前端模块主要实现模拟低频信号上变频到适合传输的射频信号,或者把从空间接收到的射频信号下变频到数字中频信号。为了避免了射频单元的设计,系统借用了USRP里的射频子板WBX,该子板只需通过FPGA将配置参数写入射频模块,实现射频模块的工作方式、衰减系数和中心频率等参数控制,就能快速构建实际无线通信链路。其中WBX射频板卡频率范围:50MHz~2.2GHz,包括公共安全、广播电视、未来陆地移动通信、低功耗unlicensed设备、WSN、手机,以及五个业余无线电波段。由于采用宽带WBX射频板,使得本硬件平台能够满足多种通信系统。通过FPGA配置,可以快速灵活的构建不同实际通信系统。

3 结论

本文设计的基于Xilinx公司的ML605 FPGA为核心的无线通信硬件验证平台实物如图5所示。硬件和软件调试结果表明,该通信实验平台不仅能够满足LDPC-RCM-OFDM通信系统验证要求,还可以通过FPGA编程控制射频和AD\DA,快速而灵活的搭建其他高速无线通信系统。

参考文献

[1]Wengui Rao,Fang Lu,Shaoping Chen,Yan Dong,Shu Wang,Low-Complexity Rate Compatible Modulation via Variable Weight Sets,IEEE Global Communications Conference (Globecom 2014),Austin,USA,pp.3633-3638,Dec.2014.

[2]Liangbin Li,Ramesh Annavajjala,Toshiaki Koike-Akino,and Philip Orlik,Robust Receiver Algorithms to Mitigate Partial-Band and Partial-Time Interference in LDPC-coded OFDM Systems,Military Communications Conference (MILCOM 2012),pp:1-6,2012.

[3]北京海曼無限信息技术有限公司.USRP系列产品白皮书[Z].北京海曼无限信息技术有限公司,2009.

作者简介

周阳忠(1989-),男,土家族,湖北省利川市人。硕士研究生。研究方向为无线通信。

荣宇航(1995-),男,湖北省仙桃市人。本科生。研究方向为无线通信。

作者单位

中南民族大学电子信息工程学院 湖北省武汉市 430074