一种基于延时线的全数字脉冲式超宽带发射机

李 靖,颜廷元,洪志良,黄煜梅

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

随着全球“个性化治疗”研究热潮的到来,无线体域网(Wireless Body Area Network, WBAN)系统得以迅速发展.目前可应用于WBAN环境的无线技术主要有蓝牙、Zigbee与超宽带技术.虽然蓝牙与Zigbee技术已经得到很大程度的应用,但这2种无线技术无法在较低功耗下实现几百Mbps甚至几Gbps的数据吞吐量.而脉冲式超宽带(Impulse Radio-Ultra Wide Band, IR-UWB)技术利用非常宽的信道带宽,理论上可实现极高的数据吞吐量;同时,得益于连串离散短脉冲信号的特点,IR-UWB较易实现低功耗设计.文献[1]设计了一款UWB收发机,在2m的距离内可实现1Gbps的数据传输率,同时收发机总体功耗维持在0.5W以下.

美国联邦通讯委员会(Federal Communications Commission, FCC)于2002年批准3.1~10.6GHz的广阔频段作为民用,同时规定在此频率范围内信号的功率谱密度(Power Spectral Density, PSD)小于-41.3dBm/MHz.超宽带信号指绝对带宽(带宽指-10dB带宽,下同)大于500MHz或相对带宽大于20%的信号.IR-UWB系统一般采用二进制启闭键控(On Off Key, OOK)与脉冲位置调制(Pulse Position Modulation, PPM)调制方式实现非相关收发机,或二进制相移键控(Binary Phase Shift Key, BPSK)实现相关收发机.目前实现短时脉冲主要有2种结构: 基于振荡器与基于延时线(Delay Line)的脉冲发射机[2].基于振荡器的超宽带收发机结构[1,3]可利用更高的频段(5~10GHz),同时此种结构可实现跳频以得到更高的频谱利用率;而基于延时线的结构在低频段(3.1~5GHz)具有更大的优势,因其可实现全数字的发射机结构,可以得到更低的功耗[4].

本文采用基于延时线的结构设计了一款全数字的脉冲式超宽带发射机,片外可实现OOK/PPM调制,以满足超宽带无线技术的不同应用需求.

1 脉冲式发射机系统结构

本文设计的脉冲式超宽带发射机(transmitter, TX)的系统结构如图1(见第266页)所示.发射机由延时线、边沿合成器(Edge Combiner)及输出驱动电路(Driver)组成.同时,芯片(Chip)中集成了简单的串行通信接口(Serial Communication Interface, SCI)模块,对发射机输出信号的中心频率及PSD进行配置.另外,设计中在芯片输出与天线(Antenna)间加入带通滤波(Bandpass Filter)网络对输出信号进行滤波,最终得到满足FCC输出功率谱密度要求的脉冲信号.

图1 本文设计的脉冲式超宽带发射机结构Fig.1 Architecture of the proposed IR-UWB TX in the paper

脉冲式发射机在每个周期的输出信号时域波形可表示为:

(1)

式中:Env(t)为脉冲信号的包络;ωC为载波信号中心频率;φC0为输出信号初始相位;Tpulse为脉冲信号的持续时间;TPR为脉冲重复周期.超宽带信号的Tpulse为几纳秒到数百皮秒,而TPR依据数据率及调制方式而定,Tpulse/TPR一般为远小于1的一个值,若此值为0.1,则发射机在90%的时间是没有信号输出.为此,图1所示的发射机中所有模块均采用数字结构,可预先通过SCI模块对系统进行配置,在配置完成以后,芯片只在触发器(Trigger)输入变化时进行状态的改变,Trigger信号上升沿到来后,芯片输出一个所设定的短时脉冲信号,之后系统状态保持不变.由于系统为全数字结构,在系统状态保持不变时,不存在静态功耗(漏电功耗除外),从而降低了系统平均功耗.

从式(1)可以看出,短时脉冲信号由2个正弦信号相乘得到: 一为包络信号Env(t),包络信号可以具有多种形式,例如一阶高斯脉冲;一为具有固定振荡频率的载波信号sin(ωCt+φC0).包络信号与载波信号相乘,将包络信号的频谱搬移到更高的频率,以使信号可在自由空间传输.设计的信号可以归为高斯类脉冲信号,其与传统高斯脉冲信号的区别为,将信号频谱进行频率搬移的方法由对低阶高斯脉冲信号的求导改为对低阶高斯脉冲信号进行直接混频.发射机中采用延时线、边沿合成器及输出驱动电路合成具有特定频率的载波,并通过调节边沿合成器及输出驱动在时间上接入电路的数量得到不同的脉冲信号包络间接实现混频操作.

2 脉冲式发射机电路设计

2.1 延时线及延时单元设计

图2为脉冲式发射机中采用的延时线结构,由12级延时单元电路串联组成.每级延时单元将输入信号进行延时操作后得到2路输出信号,同时延时链的末端输出信号作为下一级延时单元的输入信号.每

图2 延时线电路结构Fig.2 Delay line circuit structure

级延时单元的输出信号经过缓冲器后得到12×2路具有不同延时的多相位信号,并且每路信号与其前后信号间的时差为固定值ΔT(例如图2中PN[1]要比PP[1]延迟ΔT到来,比PP[2]提前ΔT到来).

图3 延时单元电路Fig.3 Circuit of delay cell

延时单元由两级串联的反相器及二进制编码控制的电容阵列组成,如图3所示.反相器的延时ΔT可表示为:

ΔT≈0.69×RN/P×Cload,

(2)

其中:RN/P为反相器中N沟道金属氧化物半导体(N-channel Metal Oxide Semiconductor, NMOS)/P沟道金属氧化物半导体(P-channel Metal Oxide Semiconductor, PMOS)的等效导通电阻;Cload为反相器输出的等效负载电容.此延时的大小决定了输出脉冲信号的中心频率,如式(3)所示:

(3)

反相器中场效应管的尺寸不变,通过改变负载电容的数量,实现对反相器延时的调节.采用自SCI得到的6位二进制编码的控制信号,同时控制反相器链中反相器的负载电容阵列,每一级延时单元得到相同的延时.同时,在反相器的电源通路中串联使能场效应管,在输出不同的脉冲信号时,通过控制使能信号EN、EP,将多余的延时单元关掉以节省功耗.

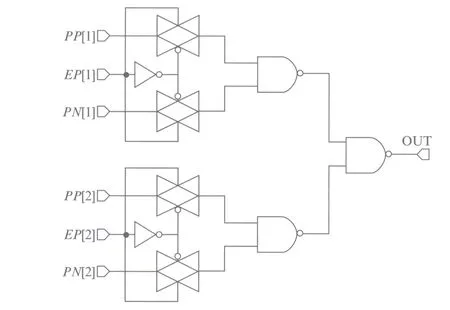

2.2 边沿合成器设计

此模块将延时线输出的12×2相位信号进行逻辑运算,得到与输出信号具有相同中心频率的方波脉冲信号,同时实现对输出脉冲信号PSD的调节.边沿合成器由若干个逻辑单元组成,逻辑单元的结构如图4所示.逻辑单元的真值表达式如下:

EN[1]*(PP[1]*PN[1])+EN[2]*(PP[2]*PN[2]).

(4)

逻辑单元的输入PP[1]/PN[1]、PP[2]/PN[2]按顺序与某两级延时单元的4路输出延时信号PP[n]/PN[n]、PP[n+1]/PN[n+1]连接.级联的延时单元将相互间隔ΔT的上升/下降沿传输到逻辑单元的4路输入,当PP[1]为上升沿时,根据控制信号EP[1]/EP[2]在输出端产生若干(0、1或2个)方波信号,当EP[1]/EP[2]同时为高电平时,其时域波形如图5所示.

图4 边沿合成器逻辑单元Fig.4 Logic cell of edge combiner

图5 逻辑单元的输入与输出Fig.5 Input and output of logic cell

为解决逻辑单元输出信号的上升与下降沿不对称而导致方波脉冲信号的占空比不为50%的问题,逻辑单元中使用的与非门采用了一种全对称的结构.典型双输入互补逻辑与非门结构如图6(a)(见第268页),2个输入分别与下拉网络中级联的NMOS管的栅极相连,其中NMOS晶体管MN2的源端与衬底并不相连,晶体管存在的体效应导致晶体管的阈值电压及等效导通电阻与另一NMOS晶体管MN1不同,与非门的2个逻辑输入并非完全对称.全对称的与非门采用2组串联的NMOS管作为下拉网络,分别将具有体效应与不存在体效应的2个NMOS作为同一个输入的下拉晶体管,如图6(b)所示,此结构与非门的2个输入具有完全对称的特性.

图6 (a) 典型与非门,(b) 全对称与非门Fig.6 (a) Typical NAND gate, (b) full symmetric NAND gate

边沿合成器包含6×63个逻辑单元.逻辑单元分为6组,每组逻辑单元中的2路控制使能信号(EP[1]与EP[2])分别采用6位二进制编码的数字逻辑控制,同时6组逻辑单元的4路不同相位输入分别与延时线输出的12×2路多延时信号连接.边沿合成器引出了12路(每路控制信号包含6位二进制编码的控制信号)控制信号由芯片中的SCI接管,通过SCI的预先配置信息调节边沿合成器的6×63路输出信号.

2.3 输出驱动电路设计

虽然FCC要求在3.1~10.6GHz频率范围内的PSD应小于-41.3dBm/MHz,此为一个比较小的值,一般不需要单独的功率放大器[5].但是由于芯片内部连线及输出Pad存在一定的寄生电容,所以发射机常内部集成一个片上输出驱动模块.图7为本次设计中采用的输出驱动电路结构,由6×63个NMOS管组成.边沿合成器的6×63路输出信号驱动NMOS晶体管的栅端,同时所有晶体管的漏端连接在一起与芯片输出端口相连.在输出等效电路中,NMOS管可以等效为一个具有导通电阻的开关,等效的导通电阻大小与NMOS管的导通个数成反比.若输出驱动电路驱动具有固定特征阻抗的天线时,在天线上得到的信号幅度随电路中NMOS管的等效导通电阻的减小而升高.通过SCI配置边沿合成器中6×63路在不同时间输出的方波个数不同,调节某一时间点做开关动作的输出晶体管的个数以得到不同的信号幅度及包络,达到调节无线信号PSD的目的.

图7 发射机中的输出驱动电路Fig.7 Output driver used in TX

同时,系统结构中所示的带通滤波器由芯片输出Pad与印刷电路板(Printed Circuit Board, PCB)间的键合线寄生电感及PCB上串联的分立电容(Cout)组成.此种结构可以利用键合线寄生电感,减小芯片面积及PCB系统上的分立元件数量,从而降低成本.不能精确的估算的键合线寄生电感值会导致输出带通滤波网络的频带偏移,但超宽带信号具有非常高的带宽,对输出中心频率的精确度要求不高,所以采用键合线电感的设计是可行的.

3 芯片实现及测试结果

此次设计的脉冲式超宽带发射机采用SMIC的0.13μm RF CMOS工艺实现,芯片面积为1118μm×873μm,图8为发射机芯片照片.发射机芯片布局采用信号流主导的布局方案,信号自上而下、自左而右在芯片中传输.

图9为脉冲发射机的输入Trigger信号与射频输出信号之间的关系.可以看出,发射机的Trigger信号每到来一个上升沿信号,会在射频输出端口得到一个短时脉冲信号输出.此次设计的发射机芯片内并未集成数据调制功能,测试时使用任意信号发生器产生不同频率的方波信号作为发射机的作为发射机的输入触发信号.

图8 发射机芯片照片Fig.8 Photo of TX chip

图9 发射机的触发输入与射频输出信号Fig.9 Trigger input and RF output of TX

芯片输出的短时脉冲数目可通过SCI配置以调节脉冲信号的PSD,使之满足FCC对超宽带信号的要求.图10为3种脉冲信号的时域波形.从图10中的3种脉冲输出信号的时域波形可以看出,发射机输出脉冲信号的峰值最大为220mV,同时可实现具有不同包络及持续时间的脉冲信号,自左向右脉冲信号的持续时间分别约为1.5,2.3,3.0ns.

图10 3种不同配置的输出脉冲信号Fig.10 Three output pulse signals in set up

3种脉冲信号在不同的脉冲重复频率(Pulse Recurrence Frequency, PRF)下的频域特性如图11(见第270页)所示,信号的带宽与其持续时间成反比关系,由左向右的3种信号的-10dB带宽分别约为1.5,1.2,0.9GHz.

图11 3种输出脉冲信号的PSDFig.11 Three different pulse signals of the PSD

若以相同的PRF传输3种不同的脉冲信号,在相同的时间内会得到的不同的总能量,同时3种信号具有不同的带宽,所以必然具有不同的峰值功率谱密度.当使用图10中的3种脉冲信号传输数据时,在信号功率谱满足FCC的频谱要求的情况下,3种脉冲信号可实现的最大PRF分别为40,25,15Mb/s.

若要实现更高的PRF,同时脉冲信号对FCC规定的频谱罩不产生冲突,必须降低信号的峰值.图12为具有同样持续时间的脉冲信号在2种峰值及不同PRF下的时域及频域波形.左侧信号的峰值为221mV左右,在符合频谱罩时最大的PRF为15Mb/s左右,而右侧峰值信号为96mV时,最大PRF为30Mb/s.

图12 调节脉冲信号的峰值以实现更高的PRFFig.12 Adjusting amplitude of pulse signal to achieve higher PRF

另外,通过调节延时线的延时大小,可实现不同中心频率的脉冲信号,如图13所示.发射机的脉冲信号输出所具有的中心频率最高可达到4.4GHz,最低中心频率为3.2GHz.

表1总结了本文设计的脉冲式发射机与其他相似工作的性能参数对比.发射机电源为1.2V时,输出信号的最大峰值为220mV,若脉冲信号的带宽为0.9GHz、PRF为15Mb/s,此时芯片功耗为0.9mW,即每个脉冲需要消耗60pJ的能量.脉冲信号的带宽可在0.9~1.5GHz间调节,信号的中心频率范围为3.2~4.4GHz.设计的发射机具有与国际先进水平相当的-10dB信号带宽,信号中心频率可满足3.1~5GHz的低频段信道要求.另外,脉冲最大幅度要比文献[4-5]低;为测试芯片加入的测试模块的电源并未与核心电路分离,同时未优化边沿合成器中逻辑电路晶体管的大小,工作在较高频率的逻辑单元导致较高的动态功耗,每个脉冲需消耗的能量为三者中最高,仍需进一步优化.

图13 脉冲信号的中心频率变化范围Fig.13 Center frequency range of pulse signals

设计工艺脉冲峰值/mV-10dB带宽/GHz中心频率/GHz功耗/(pJ·pulse-1)调制方式RFIC2013[4]90nm740105~18631~600200OOK/PPMISSCC2014[3]65nm40008(FHOff)2(FHOn)75~925276OOK本文130nm22009~1532~440600OOK/PPM

4 结 语

本文设计了一款基于开环延时线结构、可应用于WBAN的脉冲式超宽带发射机.发射机芯片为全数字结构,采用中芯国际0.13μm RF CMOS工艺实现.测试结果表明,该发射机在输入触发信号的上升沿到来时,可在输出端产生最大峰值约为220mV的短时脉冲信号,脉冲信号的功率谱密度可根据实际需要调节信号的持续时间及包络信息,-10dB带宽可在0.9~1.5GHz内调节,同时脉冲的中心频率变化范围为3.2~4.4GHz.在PRF为15Mb/s、信号带宽为0.9GHz、脉冲峰值为220mV时,芯片功耗为0.9mW.

[1] KO J, GHARPUREY R. A pulsed UWB transceiver in 65nm CMOS with four-element beamforming for 1Gbps meter-range WPAN applications [J].IEEEJournalofSolid-StateCircuits, 2016,51(5): 1177-1187.

[2] CHANDRAKASAN A P, LEE F S, WENTZLOFF D D,etal. Low-power impulse UWB architectures and circuits [J].ProceedingsoftheIEEE, 2009,97(2): 332-352.

[3] GENG S, LIU D, LI Y,etal. A 13.3mW 500Mb/s IR-UWB Transceiver with link margin enhancement technique for meter-range communications [C]∥IEEE International Solid-State Circuits Conference Digest of Technical Papers. San Francisco, CA: IEEE Press, 2014: 160-161.

[4] EBRAZCL A, MOHSENI P. An all-digital IR-UWB transmitter with a waveform-synthesis pulse generator in 90nm CMOS for high-density brain monitoring [C]∥IEEE Radio Frequency Integrated Circuits Symposium. Seattle, WA: IEEE Press, 2013: 13-16.

[5] RHEE W, XU L, ZHOU B,etal. Low power, non invasive UWB systems for WBAN and biomedical applications [C]∥2010 International Conference on Information and Communication Technology Convergence. Jeju, Korea: IEEE Press, 2010: 35-40.