基于FPGA和以太网数据采集系统的设计与实现分析

彭会斌

(海军驻连云港七一六研究所军事代表室,江苏连云港,222061)

基于FPGA和以太网数据采集系统的设计与实现分析

彭会斌

(海军驻连云港七一六研究所军事代表室,江苏连云港,222061)

现阶段,气体传感器发展速度极快,对近红外可调谐二极管激光吸收光谱技术的研究也更加深入。而气体传感器也被广泛地应用在实践运用过程中,比较常见的就是车载与机载环境,一定程度上提高了空间分辨率,能够对数据进行连续且实时采集与分析。

FPGA;以太网;数据采集系统;设计;实现

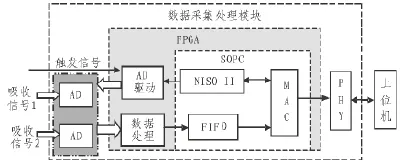

1 数据采集系统整体设计研究

基于FPGA与以太网数据采集系统整体设计可以由图1表示。根据图1内容可以发现,当吸收峰出现前会给出触发信号。而数据采集系统的触发信号上升沿出现的情况下,将两路AD启动,进而采集两路的模拟信号,在完成转换以后,会进入到FPGA,并针对数据信息予以及时处理和计算。随后会进入到FIFO缓冲当中,而在对固定点数数据进行采集的过程中,FPGA就会停止对数据的接收,而随之会等待下次触发信号出现。如果FIFO缓冲数据处于半满的状态,需要将数据取出并加入UDP协议。最后,通过MAC这一途径,对PHY予以合理运行,以保证数据信息及时传送至上位机。若置触发信号仍然有效,则应当关闭计数的功能,以保证连续且实时地采集两路的信号。

图1 数据采集处理系统

其中,FPGA是系统核心,而在设计过程中所使用的FPGA型号为。该FPGA具备了10kbit的逻辑单元、外部存储器的接口电路、存储器与乘法器等等类型的FPGA能够降低功耗,节省成本,使其自身性能得以全面提升,最终促进了FPGA应用的领域。另外,AD器件所选择的型号为ADS8326。与此同时,以太网收发器选用型号是,具有明显的集成性。

2 AD驱动和数据处理模块分析

在AD驱动实际运行的过程中,一旦CS信号有下降沿的情况,那么必须要保证DCLOCK是低电平。与此同时,应确保CS下降沿和DCLOCK上升沿之间的距离不低于20纳秒。当在CS信号出现下降沿的时候,会经由五个DCLOCK 采样以后,在第七个DCLOCK时出现上升沿,而AD驱动则会由最高位串行输出数据,在完成相应转换以后,再次通过若干DCLOCKPower Down,随后即可实现下一转换。在系统内部,已经嵌入32位处理器,进而能够将原有的两路的串行信号有效地转变为,形成一路并行信号。在这种情况下,能够进一步推动数据传输的处理。基于此,需要针对转换以后的并行信号数据进行计数,以确保触发控制更加准确。但是,由于32位并行信号要进入到FIFO缓冲当中,所以,一定要为FIFO提供必要的时钟信号与使能信号。该系统主要对VerilogHDL硬件语言进行了运用,对AD驱动与处理模块进行了编写。

3 SOPC模块设计分析

针对SOPC开发环境而言,可以有效地加入处理器与IP核,包括用户逻辑等等。基于此,通过对Avalon总线的运用,能够有效连接模块,进而根据地址进行访问,适当地添加中断。其中,处理器十分灵活且IP核十分丰富,使得系统设计得以有效简化,节省了大部分成本,使实际开发的时间得以有效缩短。其中,该模块当中的硬件主要有处理器与存储器,另外还包括了MAC模块与通用IO等等。

其中,Nios Ⅱ处理器的内核所使用的是RISC的处理器,有32位,具备了共享性的指令集结构,最重要的是已经根据FPGA展开了全面优化。另外,处理器主要的作用就是处理数据以及网络协议。

MAC,也被称为介质访问控制层,主要的任务就是对物理层物理介质进行有效控制及链接。其中,MAC模块对于Triple−Speed EthernetIP核进行了有效地调动,而在实现发动与接收的过程中所采用的就是接口。在这种情况下,用户只要利用这一接口,就可以读写并操作MAC内部所接收和发送FIFO。而MAC是通外部PHY进行连接的,与此同时,此模块能够提供MDIOMDC 接口,有效地管理PHY。

4 数据采集系统的软件设计分析

基于NiosⅡIDE这一集成开发环境,能够通过C语言,优化设计NiosⅡ处理器这一软件。其中,各模块需要初始化,而此时上位机会将已经采集完成的控制信号发送出来,随后,系统开启信号采集模式。与此同时,数据处理模块会把经过处理以后的32位数据传送至异步FIFO当中。一旦其处于半满状态,就会立即中断,并且取出数据内容,加入到UDP协议当中。最后,将Scatter−Gather DMA启动,以保证及时把数据内容传送至MAC当中。

而UDP协议无法开展反馈测试,所以,其可靠性并不明显,仍然要有其他措施发挥辅助作用,确保传输更加可靠。然而,因为UDP不会创建与撤销连接,也不会确认报文等,所以,能够全面增强数据传输本身的高效性以及实时性。在该系统设计过程中,以太网传输协议主要选用了UDPIP 协议。

5 数据采集系统的测试分析

在完成数据采集系统设计工作后,一定要通过实际测试对系统的可行性进行验证。该系统在以太网接口的作用下,能够把数据及时传输到上位机,而PC机则能够编写程序,实时存储并显示数据内容。

其中,连续实时采集模式主要是通过函数信号发生器形成10K正弦波,进而将其当作输入信号。充分利用采样定理,系统能够对正弦信号进行全面修复,且实际采集的图像和预期效果之间是一致的。

对于触发采集开启的功能而言,主要是对函数信号发生器进行合理地运用,有效地提供正弦与方波信号,将其当作测试信号。而这两种信号频率是相同的,且相位差固定。通过对Wireshark 网络抓包工具进行运用,深入分析数据包,测试的时间、数据帧等都同100赫兹触发频率是一致的,实验的结果和预期相同。

6 结束语

综上所述,通过对FPGA与以太网这两种技术的结合运用,对数据采集系统进行了有效地设计,不仅对采集系统触发采集问题进行了解决,同时,对通用以太网接口传输数据进行了合理地运用。通过系统的测试,表明该系统能够满足200赫兹双路触发采集的目的,所以,系统设计具有一定的合理性。

[1]任慧建,殷兴辉.基于FPGA的高速线阵CCD图像采集系统[J].电子测量技术,2014,37(11):33-36,51.

[2]王浩,李磊,杨洁等.基于以太网传输的高速32通道数据采集系统[J].核科学与工程,2015,35(4):780-784.

[3]汤奥.基于PCI-E接口数据采集系统FPGA设计与实现[D].华中科技大学,2011.

Design and implementation of data acquisition system based on FPGA and Ethernet

Peng Huibin

(Military representative office, Naval Research Institute, Lianyungang 716,Lianyungang Jiangsu,222061)

at the present stage, the development of gas sensor is very fast, and the research of near infrared tunable diode laser absorption spectroscopy is more in-depth. The gas sensor is also widely applied in the practical application process, the more common is the vehicle borne and airborne environment, to a certain extent to improve the spatial resolution, can be continuous and real-time collection and analysis of data.

FPGA; Ethernet; data acquisition system; design; implementation