TI C66X多核DSP的PCIe接口程序设计

白轶荣++李伟++刘宝东+丁建岽

摘 要: TI的C66X多核DSP拥有丰富的接口资源,单片集成了高速串行接口AIF2、SGMIL、PCIe和SRIO等,能够非常方便地进行高速数据传输和系统扩展,其中PCIe接口应用最广,它广泛地应用在信号处理、通信、医疗、自动化等领域。本文阐述了PCIe接口的Inbound和Outbound地址映射寄存器配置方法、PCIe的中断安装过程和EDMA的传输配置与实现过程。用该方法可快速完成多核DSP的PCIe接口配置与编程,方便PCIe接口的推广和应用。

关键词: 多核DSP; PCIe; EDMA; Inbound; Outbound

中圖分类号:TP315 文献标志码:A 文章编号:1006-8228(2017)02-16-04

0 引言

TI的C66X多核DSP拥有丰富的接口资源,单片集成了高速串行接口AIF2、SGMIL、PCIe和SRIO等,能够非常方便地进行高速数据传输和系统扩展,其中PCIe接口应用最广,它广泛地应用在信号处理、通信、医疗、自动化等领域。

本文主要研究多核DSP的PCIe接口程序设计,首先概述PCIe模块,其次阐述了PCIe接口的Inbound和Outbound地址映射寄存器配置方法、PCIe的中断安装过程和EDMA的传输配置与实现过程,最后对本文作出总结。

1 PCIe模块概述

TI C66系列DSP集成了二个通道PCIe模块。该模块主要具备以下特征:支持两种工作模式:RC和EP;支持Genl(2.5Gbps)和Gen2(5.0Gbps)两种链路速率;用户可以选择使能一个或两个通道,当使用双通道时,需配置为相同的链路速率;支持的最大输出净荷大小为128字节,最大输入净荷大小为256字节;支持动态的带宽切换等[1]。

PCIe设备需要使用PCIe地址经PCIe数据链发送数据包,地址翻译单元ATU(Address Translation Unit)将设备内部地址翻译为PCIe地址,反之亦然。PCIe地址可以是32-bit或64-bit。

2 PCIe地址翻译

对于输出处理,Outbound ATU把设备内部地址翻译成PCIe地址,然后含PCIe地址的数据包经PCIe链路被传输到其他设备。

对于输入处理,PCIe模块的基址寄存器BAR (Base Address Register)只接收特定PCIe地址的数据包,这些数据包进入Inbound ATU,经地址翻译后被送至相应的内存空间。C66X DSP的PCIe地址翻译原理图如图1所示[4]。

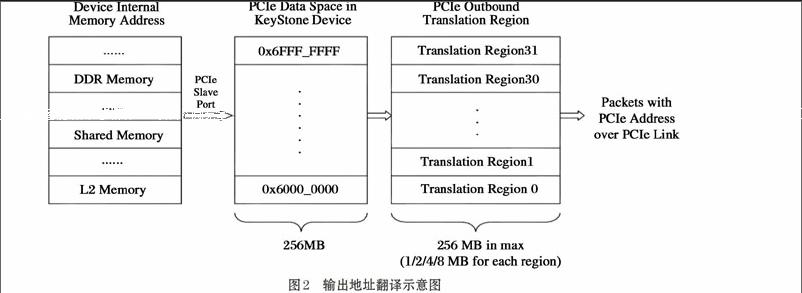

⑴ 输出地址翻译

TI C66设备中有特定的PCIe数据空间0x60000000-0x6FFFFFFF,专门用于收发PCIe数据。对于输出传输,通过Outbound ATU的配置使该空间与另一侧设备地址空间建立对应关系,再使用EDMA把设备内存数据搬移到PCIe数据空间,这样数据就可以通过PCIe链发送出去。

输出地址翻译主要通过以下寄存器的配置来实现。

OB_SIZE:设定32个等长的翻译区的大小,它们可以为1MB、2MB、4MB、8MB。

OB_OFFSET_INDEXn:代表PCIe地址的bit[31:20],具体哪些位有效需根据OB_SIZE来确定,bit[0]使能输出region。

OB_OFFSETn_HI:代表64位PCIe地址的bit[63:32],使用32-bit地址模式时该寄存器为0。

由于存在32个翻译区域,所以需要根据内部地址的5bits来决定使用哪个区域进行映射。PCIe输出地址翻译示意图如图2所示[4]。

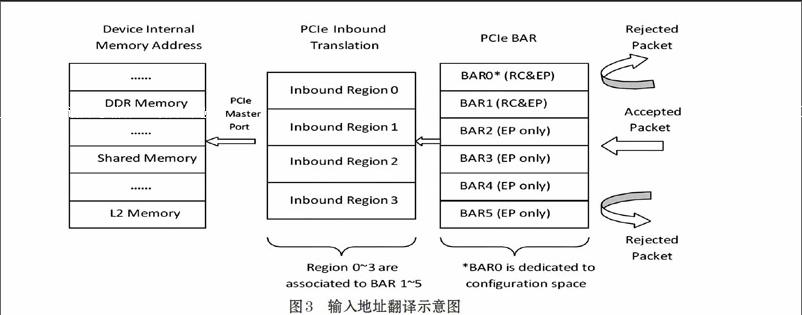

⑵ 输入地址翻译

Inbound ATU用于将外部设备输入的访问地址重定位到DSP片内地址。C66设备的PCIe模块有两个内部地址空间:Address Space 0和Space 1。前者用于本地应用寄存器和配置空间,占用连续的16KB,其中4KB用于配置空间;后者用于数据传输,容量大,可以不连续,为了将PCIe地址映射到该空间,需使用4个区域(region0-3)来协助完成。

PCIe输入地址翻译通过配置寄存器IB_BARn、IB_STARTn_HI、IB_STARTn_LO和IB_OFFSETn来实现,Inbound ATU将PCIe地址映射到内部地址的过程如下[5]。

① 分离偏移值:

Offset=PCIe address-(IB_STARTn_HI:IB_STARTn_LO)

② 计算内部地址:

Internal address=IB_OFFSETn+offset

PCIe输入地址翻译示意图如图3所示。

3 PCIe中断

PCIe中断控制器包括核级中断控制器和片级中断控制器CIC,中断的路由可概括为:系统中断先通过CIC映射到主机中断上,主机中断再由核级INTC的事件组合器、中断选择器等寄存器映射到CPU的12个可屏蔽的中断上。CPU的12个可屏蔽的中断也就是HWI可以为其指定ISR。在ISR中查询相关状态寄存器可以确定中断〔

OPT参数可以设置对应通道的优先级、同步方式、传输方式等。SRC/DST用于存放EDMA传输的源地址和目的地址。SRCBIDX/DSTBIDX指示传输帧中数据阵列array的间隔。LINK指明EDMA的参数链接地址。SRCCIDX/DSTCIDX指示传输块中帧间间隔。CCNT表示传输帧数。

传输参数的链接由Param的Link位进行控制,Link可以链接到256个参数中的任何一个或者自身,链接参数的最后一个参数为NULL参数。同时EDMA还支持通道链接Chain传输,允许由一个EDMA传输通道的完成触发另一个传输通道的开始,组成一个传输链。需注意参数链接和通道链接有着本质区别,参数链接是指将多组参数加载到某一EDMA通道,而链接传输不修改任何传输参数,其可以通过一个事件同步所有的通道传输。

OPT的设置有:TCINTEN(1,传输完成产生中断)、TCC(传输完成码为0,在IPR的最低位产生中断)、TCCMODE(0,正常传输完成)、STATIC(1,参数集是静态的不自动更新)、SYNCDIM(1,AB同步传输)、DAM/SAM(0,源和目的地址自动更新)。

启动EDMA传输的方式有多种,最常用的是Manual Trigger,我们通过写ESR中的某一位可以启动其对应的通道提交传输请求事件,这个事件经过优先级的过虑后,会发送到一个事件队列中,这里可以通过设置DMA Channel Queue n Number Registers (DMAQNUMn)寄存器将通道提交的传输请求事件派发到指定的事件队列中。

使用EDMA3进行读的过程如下(写的过程类似,区别在于源与目的地址不一样) [3]:

⑴ 配置Outbound,将主机的PCIe域地址映射到DSP的PCIe data space address(0x6000_0000~0x6FFF_FFFF);

⑵ 設置通道0使用事件队列0也就是使用TC0;

⑶ 使能IER;

⑷ 清除ICR;

⑸ 设置传输属性寄存器;

⑹ 将主机端具体的PCIe域地址,转换成DSP端的PCIe data spaceaddress(0x6000_0000~0x6FFF_FFFF)范围内的地址;

⑺ 设置PaRAM的其他域,包括ACNT、BCNT、SRC、DST、LIKE等;

⑻ 启动EDMA3传输。

5 结论

本文详细介绍了PCIe接口的Inbound和Outbound地址映射寄存器配置方法,以及PCIe的中断安装过程和EDMA的传输配置与实现过程。通过本文方法可快速完成基于多核DSP的PCIe接口配置与编程。由于TI公司的C66x系列DSP定位于各行各业的开发应用,因此本文方法可为通信领域、航空电子、实时检测、生物识别、医疗诊断、视频监控以及音频处理等系统的PCIe接口程序设计提供参考。

参考文献(References):

[1] 王齐.PCI Express体系结构导读[M].机械工业出版社,2010.

[2] 牛金海.TMS320C66x KeyStone架构多核DSP入门与实例

精解[M].上海交通大学出版社,2014.

[3] 潘晔,廖昌俊.TI-DSP多核技术及实时软件开发[M].电子工

业出版社,2015.

[4] TEXAS INSTRUMENTS. Keystone Architecture Peripher-

al Component Interconnect Express(PCIe) User Guider. Devices. http://www.Ti.com,Technical Report, December 2012.

[5] TEXASINSTRUMENTS.PCIeUse Case for Keystone

Devices.http://www.Ti.com,Technical Report,December 2012.

[6] TEXAS INSTRUMENTS. Enhanced Direct Memory

Access (EDMA3) Controller User Guide. http://www.Ti.com,Technical Report,December 2012.