基于IP核FIR滤波器的设计与FPGA实现

郭 勇, 杨 欢

(南京北方信息控制集团有限公司 产品研发中心,江苏 南京 211153)

基于IP核FIR滤波器的设计与FPGA实现

郭 勇, 杨 欢

(南京北方信息控制集团有限公司 产品研发中心,江苏 南京 211153)

介绍了一种基于Altera公司IP核进行FIR数字滤波器的参数设计及在FPGA中的快速实现方法。为了达到FIR滤波器的性能要求,介绍了Matlab和IP核中信道冲激响应的阶数和时域系数的设计方法。编程实现了时域卷积运算,并给出了冲激响应和输入数据比特量化的方法和结果。为验证FIR滤波器设计的正确性,分别给出了Matlab和ModelSim中FIR低通滤波器的仿真输入波形和滤波输出波形。仿真结果表明,设计的滤波器通带信号完整,阻带滤波性能良好,该方法具有较好地适用性。

FIR;IP核;FPGA;时域卷积;波形验证

0 引言

FIR滤波器具有严格的线性相位,且稳定性高,广泛用于信号检测和处理等领域。基于FPGA实现FIR滤波器的方法具有灵活、高效和动态可配置等特点。Altera公司的FIR滤波器的IP核功能强大,采用IP核的方法既可以保证性能,又能极大地缩短设计时间。目前的文献中,完整地介绍滤波器参数设计[1]、IP核设计方法[2]及滤波性能测试的文献不多[3],而且针对卷积运算的代码实现也没有提及[4]。本文着重介绍Matlab和IP核中FIR滤波器参数的设计方法和时域卷积运算的编程实现,并采用大容量仿真数据测试基于IP核FIR滤波器的滤波性能以及用Matlab设计滤波器的滤波性能。

1 FIR滤波器的数学原理及结构

FIR时域结构图如图1所示。

图1 FIR时域结构

FIR滤波器是线性时不变系统,该系统的特征是输出序列y(n)等于输入序列x(n)与单位冲激响应h(n)的线性卷积。由图1可知,y(n)等于当前时刻的输入x(n)与N-1个时刻的x(n)与N个抽头系数相乘再相加得到。FIR滤波器具有严格的线性相位特性,且h(n)满足对称性。

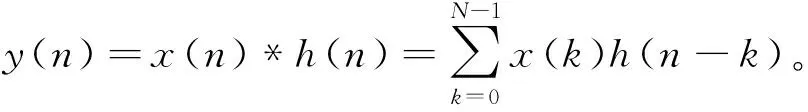

x(n)为输入序列,h(n)为FIR滤波器的单位冲激响应,y(n)为输出序列。x(n)与h(n)做卷积运算如下:

目前文献中没有提及对卷积运算的编程实现。本文给出上述公式的Matlab代码实现如下:

%信号x经过FIR滤波器,N1=37,为FIR滤波器的阶数,L为输入序列的长度

z1=zeros(1,N1); %z1为1行37列的移位寄存器

y1=zeros(1,L); %y1为滤波后的信号

h1=h1’; %对信道冲激响应进行转置

fori=1:L

z1(1) =x(i); %x为输入序列

%加汉明窗进行滤波

% 2个矩阵做乘积运算,计算每个点的卷积值

y1(i) =z1*h1;

z2=z1(1:N1-1);

z1(2:N1)=z2;

z1(1)=0;

end

y1; %滤波后的信号

2 FIR滤波器的参数设计方法

设计的FIR低通滤波器通带截止频率为1.2 MHz,采样频率10 MHz,要求采用窗函数法设计。经过仿真验证,选择汉明窗,阶数n=37,满足要求[5-6]。在Matlab中输入fdatool,启动滤波器设计套件。在参数设置界面中输入以下参数:方法采用窗函数法,选择的窗口类型为“Hamming”,Fs=10 MHz,Fc=1.2 MHz。其中n=36,表示生成的阶数n=37。生成的信道冲激响应h(n)为:

h(n)=[0.001 2,0.000 4,-0.001 0,-0.002 9,-0.003 9, -0.002 2,0.003 0,0.010 0,0.013 9,0.009 2,-0.0061, -0.026 8,-0.040 1,-0.031 3,0.008 9,0.076 7, 0.154 4,0.216 4,0.240 0,0.216 4,0.154 4,0.076 7, 0.008 9,-0.031 3,-0.040 1,-0.026 8,-0.006 1, 0.009 2,0.013 9,0.010 0,0.003 0,-0.002 2, -0.003 9,-0.002 9,-0.001 0,0.000 4,0.001 2] 。

为了验证FIR低通滤波器设计的正确性,设计输入信号为2个信号的叠加:一个是50kHz正弦波信号,一个是1.8MHz的正弦波信号,采样个数L=10 000。经过FIR滤波器后,因为FIR滤波器的通带截止频率fc=1.2 MHz,所以只有50kHz正弦波信号输出,而1.8MHz的正弦波信号被滤除,如图2所示,输出波形只有50kHz的正弦波信号,所以该FIR滤波器设计正确。

图2 滤波器输入输出波形对比

设计另一种情况,输入信号是50kHz的正弦波信号,叠加高斯白噪声。因为高斯白噪声在整个频谱范围内都存在,但通过FIR低通滤波器,可以滤除通带内的白噪声。波形如图3所示。

图3 叠加噪声的正弦波信号输入输出波形

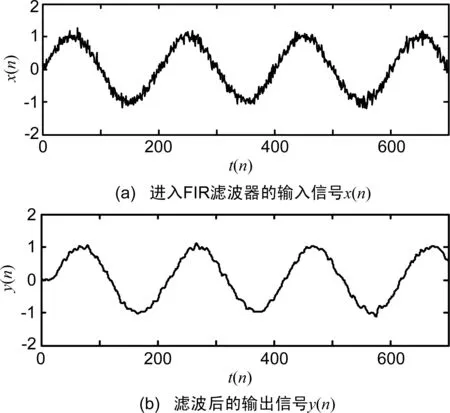

在FPGA中,参数为定点数,所以需要对滤波器参数h(n)和输入数据进行比特量化,该文设计量化为10bit。h(n)的10bit量化在IP核设置中实现,输入数据的比特量化在Matlab中编程实现,形成txt文件,便于ModelSimSE软件读取输入数据文件生成仿真测试结果[7-8]。

因为输入数据有负数,所以采用二进制补码形式表示。n=10,归一化输入数据,最大值量化为2n-1-1=511。10bit量化结果如图4所示。

图4 源数据10 bit量化对比

3 基于IP核FIR滤波器的设计方法

如前所述,FIR低通滤波器通带截止频率为1.2MHz,采样频率Fs=10 MHz,采用窗函数法设计,全并行模式。滤波器阶数为37阶,选择汉明窗。在IP核设置界面中,Filter Type栏选择Low Pass,在Coefficients栏选择37,在Window Type栏选择Hamming,在Sample Rate栏输入1.0E7,在Cutoff Freq.1栏输入1.2E6,因为采样频率10 MHz,该文设计FIR滤波器的全局时钟clk为10 MHz,所以时钟周期T=100 ns。生成的信道冲激响应h(n)的时域浮点值和比特量化值如图5所示[9-10]。在QuartusII生成的顶层文件如图6所示。其中的ask_sink_error[1..0]设为00,表示输入数据没有错误。

图5 IP核参数设置界面

图6 生成的FIR顶层模块

4 FIR滤波器的性能测试

FIR滤波器的性能测试采用文献[6]介绍的文件读写方法,采用Matlab和ModelSimSE联合仿真,便于处理大容量数据。FIR滤波器输入、输出及参数为有符号数,输出格式为二进制补码形式[11-12]。为直观显示FIR滤波器的滤波效果,在ModelSimSE中采用模拟输入和输出的方式。仿真输入、输出波形如图7所示。

输入数据是50kHz和1.8MHz两个正弦波信号的叠加信号,通过FIR低通滤波器,希望1.8MHz的信号被完全滤除,50kHz的正弦波信号完整地输出,由图7可知,50kHz的信号正确地输出,设计的FIR滤波器正确。

同时对比图2和图7可知,采用Matlab设计的FIR滤波器和基于IP核设计的滤波器输出的波形完全一致,也验证了FIR滤波器设计的正确性。

图7 基于IP核FIR滤波器的仿真输入输出波形

5 结束语

介绍了Matlab中使用FDATOOL工具设计滤波器的方法,给出了时域卷积运算的代码实现,同时介绍了冲激响应和数据的比特量化方法,并给出了Matlab中FIR滤波器的滤波波形图。本文完整地介绍了基于Altera公司FIRIP核的使用方法,并给出了完整地仿真输入、输出波形图,设计的滤波器完全符合要求。采用该方法可以很好地设计和验证项目要求的FIR滤波器。

[1] 刘东华.Altera系列FPGA芯片IP核详解[M].北京:电子工业出版社,2014:187-193.

[2]Siruiks.无线通信的Matlab和FPGA实现[M].北京:人民邮电出版社,2009.

[3] 范红旗,翟庆林.锐截止中频采样滤波器的设计与实现[J].电路与系统学报,2009,14(5):31-35.

[4] 曹振吉,何 敏.基于FPGA和Matlab的FIR数字滤波器[J].现代电子技术,2015,38(1):98-102.

[5] 喻庆华,司锡才,冯 策,等.基于IP核的FIR滤波器在新型FPGA的实现[J].弹箭与制导学报,2006,26(1):491-494.

[6] 郭 勇,陈艳玲.Viterbi-IP核纠错性能的验证[J].电讯技术,2012,52(10):1 640-1 643.

[7] 陈 镜,曹芳菊.基于IP核的滤波器复用模块的设计与实现[J].无线电工程,2010,40(4):26-30.

[8] 喻庆华,冯 策.基于IP核的FIR滤波器在数字正交变换中的应用[J].应用科技,2006,33(6):51-55.

[9] 范红旗,翟庆林,王 胜,等.基于IP核的锐截止中频采样滤波器优化设计[J].电子测量与仪器学报,2008,22(1):99-103.

[10] 许金生,周春雪.基于IPCore的FIR数字滤波器的FPGA实现[J].安徽工业大学学报,2007,24(3):309-313.

[11] 郭 勇,杨 欢.RS(63,45)编译码器的设计与FPGA实现[J].无线电通信技术,2011,37(2):54-58.

[12] 郭 勇,何 军.STM32单片机多串口通信仿真测试技术研究[J].无线电工程,2015,45(8):6-10.

郭 勇 男,(1978—),硕士,高级工程师。主要研究方向:调制解调、信道纠错编解码和无线通信中的信号处理等。

杨 欢 男,(1979—),硕士,高级工程师。主要研究方向:硬件电路设计和通信电路设计等。

Design and FPGA Implementation of FIR Filter Based on IP Core

GUO Yong,YANG Huan

(ResearchDepartmentofNorthInformationControlGroupCo.,Ltd.,NanjingJiangsu211153,China)

The paper introduces a method of how to design the parameter of the FIR filter and how to implement it in FPGA based on Altera’s IP Core.In order to achieve the capability of FIR filter demanded,the paper introduces a method of how to design the number of order ofh(n)andthetimevaluesofh(n)bothinMatlabandinIPCore,andimplementstheconvolutionoperationintimedomainbyprogramming.ThepaperalsointroducesthemethodandresultsofBitQuantificationofh(n)andinputdata.InordertovalidatethecorrectnessofFIRdesigned,thepapergivesthesimulatedinputwaveformandoutputwaveformfilteredbothinMatlabandinModelSim.ThesimulatedexperimentalresultindicatestheFIRfilterdesignedcanensuretheintegrityofsignalsinpassbandandthegoodfilteringeffectinstopband.Therefore,themethodintroducedhasthegoodapplicability.

FIR;IP Core;FPGA;time-domain convolution;waveform validation

10.3969/j.issn.1003-3106.2017.01.19

郭 勇,杨 欢.基于IP核FIR滤波器的设计与FPGA实现[J].无线电工程,2017,47(1):79-82.

2016-10-14

TN911.12

A

1003-3106(2017)01-0079-04