基于AT89S51单片机接口电路的时序仿真研究

侯进旺

(佛山职业技术学院,广东 佛山 528000)

基于AT89S51单片机接口电路的时序仿真研究

侯进旺

(佛山职业技术学院,广东 佛山 528000)

高阻态是数字电路接口器件一个重要的状态,是接口电路的硬件设计中容易忽视的一种状态。本文分析研究在某机床控制中74LS373接口芯片在单片机总线技术扩展I/O口时出现的总线冲突的时序仿真,使用接口芯片的高阻态可以有效解决多芯片I/O扩展时的总线冲突。

AT89S51单片机;接口电路;时序分析;仿真;总线冲突

0 引言

在基于单片机的工业产品控制电路设计中,输入输出通道电路通常较多地关心信号传输中输入输出通道的高、低电平,对高阻态关注较少。实际上硬件设计如果对芯片的高阻态不注意,将会造成控制电路中接口芯片短路烧毁。下面针对基于AT89S51单片机[1]总线技术进行I/O扩展时接口芯片74LS373高阻态的时序进行仿真分析研究。

1 基于单片机I/O扩展接口电路的硬件设计

1.1 基本扩展电路

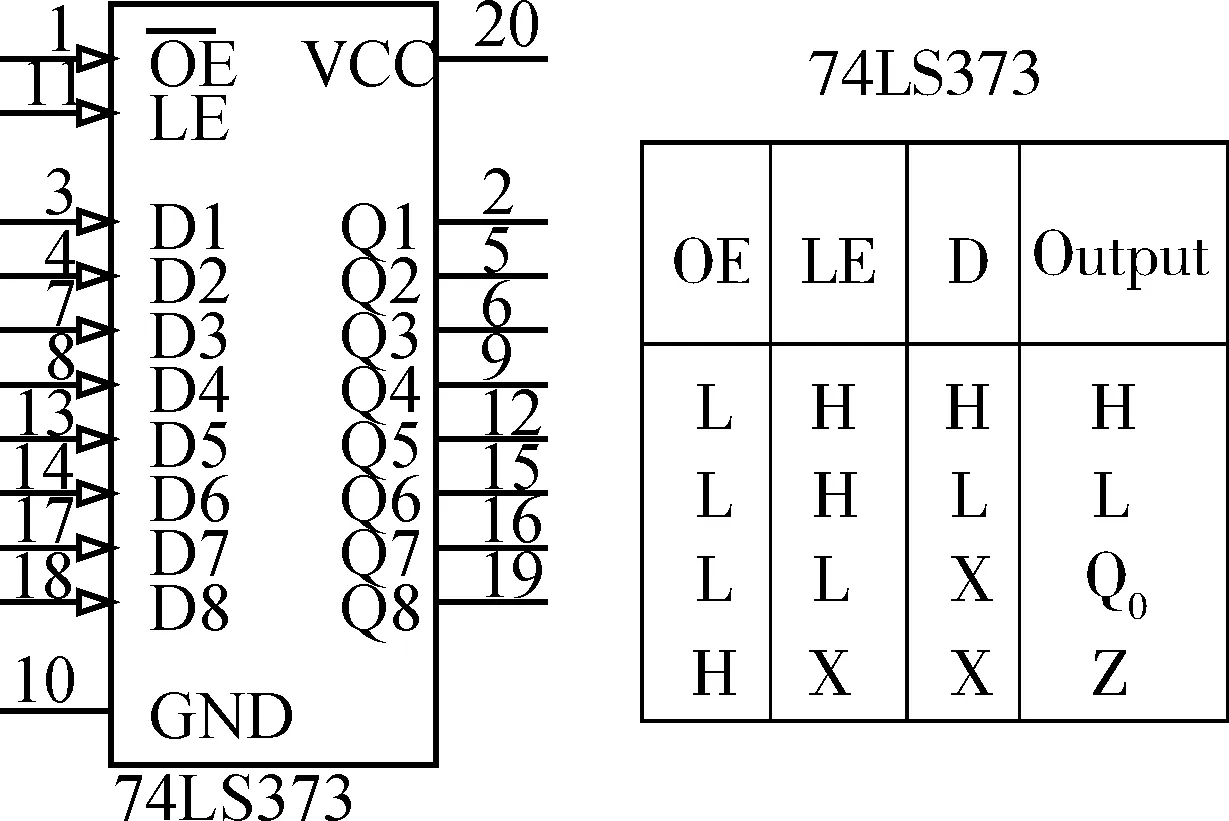

接口芯片74LS373是一个三态8D锁存器,通常用于单片机的输入输出接口,其元件原理图和功能表如图1所示。

图1 74LS373原理图与功能表

从图1功能表中知,当OE端为低电平,控制端LE为高电平时,输入D端的数据传送到输出端Q;当OE和LE同为低电平时,输出端Q保持原态(与输入D无关);当OE为高电平时,无论LE、D如何,输出均保持高阻态。

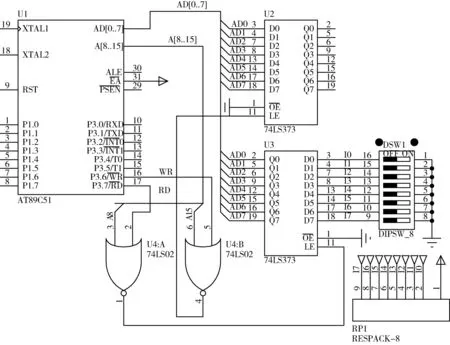

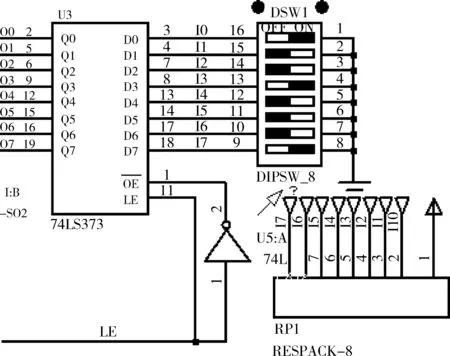

图2所示电路为基于单片机AT89S51总线技术和两片接口芯片74LS373进行I/O口扩展的电路[2]。U2扩展输出接口,U3扩展输入接口。U2和U3的接口地址分别为7FFFH和FEFFH。

在对图2电路进行PROTEUS[3]仿真时,设置输入开关的数据为01110110(76H),执行如下指令:

MOV DPTR,#0FEFFH

MOVX A,@DPTR ;读入U3开关数据

NOP

MOV DPTR,#7FFFH

MOV A,#55H

MOVX @DPTR,A ;向U2输出01010101

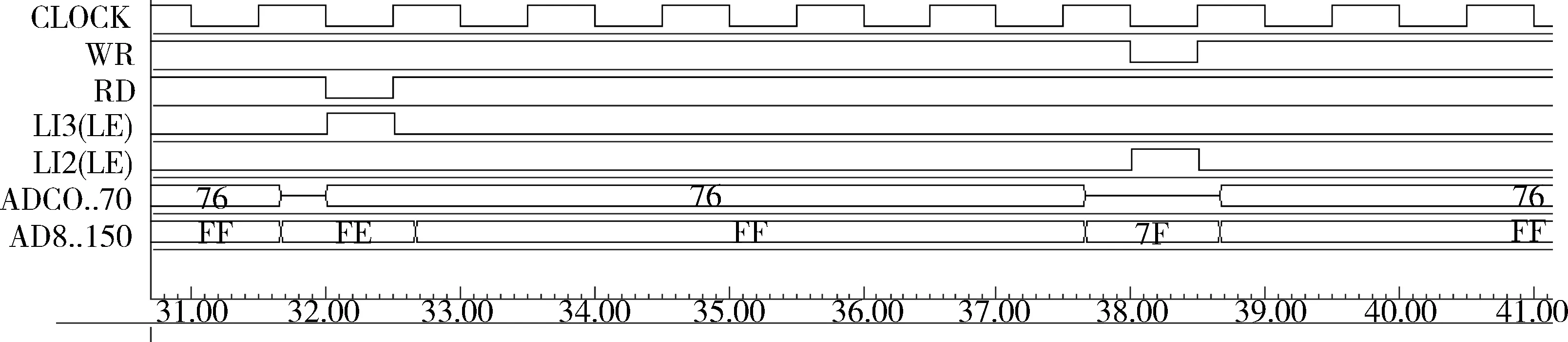

利用PROTEUS软件仿真得到基本电路图2的仿真时序图,如图3。从时序图中看出,在RD信号有效(低电平)之前,AD(0..7)(P0)数据为高阻态,说明在读U3时数据出现错误(正确应为FFH);在WR信号(低电平)前后,P0上的数据也为高阻态(正确应分别为FFH和55H),说明在U2输出时数据也出现错误;同时在对图2的电路仿真时,P0口的数据信号出现短路现象。

图2 基于单片机AT89S51总线技术和接口芯片74LS373进行I/O口扩展的电路

图3 图2电路的仿真时序图

分别对U2和U3执行输出和输入指令,通过时序分析知,U2的输出数据正确,U3的数据出现错误。

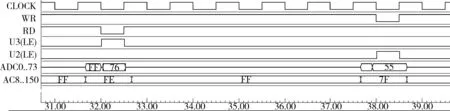

图5 重新设计后电路的仿真时序图

入接口扩展。在使用单片机总线技术扩展I/O口时,硬件设计必须要保证总线被单片机访问的接口芯片占据,而且不被访问的接口芯片与总线脱离。硬件设计时应该避免单片机的总线始终被某一个芯片占据。

[1] 余永权.Atmel89 系列单片机应用技术[M].北京:北京航空航天大学出版社,2002.

[2] 高玉琴.单片机原理与应用及C51编程技术[M].北京:机械工业出版社,2011.

[3] 张靖武,周灵彬.单片机系统的PROTEUS设计与仿真[M].北京:电子工业出版社,2007.

1.2 输入接口的扩展电路错误原因分析

从74LS373的功能表可以看出,当OE端保持在低电平,LE同时为低时,其输出保持原态,说明74LS373具有锁存功能。由于图2电路中U3的OE端常接地,使得总线始终被U3占领:当U3的LE为高时,芯片外部输入的开关信号送到芯片输出,当U3的LE为低时,其U2输出的数据状态被保持锁存,也就意味着数据总线P0口被U3保持在输入开关决定的数据。

事实上AT89S51单片机通过MOVX指令访问U2和U3时,先将U2和U3的口地址分别输出到P2口(高8位地址)和P0口(低8位地址),输出到P0的低8位地址数据可能与U3输入并保持的数据不同,从而造成P0口的数据冲突。

1.3 解决数据冲突的方法

从上述分析可以看出,造成数据冲突的原因是输入芯片U3的OE端常接地,使得单片机数据总线始终被U3芯片占据。因此在硬件设计时应该避免单片机的总线始终被某一个芯片占据的现象。

事实上,从74LS373的功能表看,它还有一个高阻态,只要保证当单片机不访问U3时或者U3被访问而在寻址阶段时,使U3的输出端始终保持高阻态,这样就能避免数据冲突。

如图4为修改后的U3控制电路,OE信号由U4A或非门输出信号取反得到。仿真结果如图5所示。在执行读入U3的指令后,数据总线(P0)上的数据为76H;在执行输出U2指令后,数据总线(P0)上的数据为55H,输入输出结果正确。

2 结论

通过以上分析和仿真,在基于单片机控制的电子电路设计中,时序的仿真分析是查找硬件电路错误的有效方法。

防止总线上数据冲突是硬件工程师在硬件电路设计中需要认真考虑的问题,而高阻态也是硬件电路设计中常用到的,这也是硬件工程师在电路设计中容易忽视的地方。

在使用单片机总线扩展I/O口时,常需要多个输入输出芯片时,正确运用接口芯片的高阻态是解决总线数据冲突的有效方法。

若接口芯片输出无高阻态控制,则该芯片不能用于输

Research on timing analysis simulation of interface circuit based on AT89S51 MCU

Hou Jinwang

(Foshan Polytechnic,Foshan 528000,China)

High impedance state is an important state of digital circuit interface device, which is easy to be neglected in the hardware design of interface circuit. This paper analyszes the time sequence simulation of bus conflict occurred in the 74LS373 interface chip in the control of a machine. The interface chip of high impedance state can effectively solve the problem of bus conflict when the chip is used to expand the I/O port.

AT89S51 MCU;interface circuit;timing analysis;simulation;bus conflict

图4 修改后的U3电路

TP368

A

1674-7720(2016)05-0043-02

侯进旺. 基于AT89S51单片机接口电路的时序仿真研究[J].微型机与应用,2016,35(5):43-44,48.

2015-12-10)

侯进旺(1959—),通信作者,男,副教授,主要研究方向:智能电子、工业控制。E-mail:fs_hjw@126.com。