基于FPGA的雷达目标模拟器设计

庄 雷,张海龙,李赛辉,吴元清

(中国船舶重工集团公司第七二四研究所,南京 211153)

基于FPGA的雷达目标模拟器设计

庄 雷,张海龙,李赛辉,吴元清

(中国船舶重工集团公司第七二四研究所,南京 211153)

介绍了一种基于FPGA的多通道雷达回波目标模拟信号产生的机理和特性,分析了常规雷达目标模拟器设计方法和局限性,重点阐述了一种多通道雷达目标回波模拟器的关键设计方法和可升级性等技术,仿真和实验结果验证了多通道雷达目标模拟器的正确性和有效性。

雷达目标模拟器; FPGA; 可升级性

0 引 言

随着现代雷达系统的功能日益复杂和使命任务多样化,其给系统调试难度也不断增大。在实际战场环境中进行复杂功能雷达系统的调试将会带来巨大的人力和物力资源耗费。因此,使用雷达目标模拟器仿真模拟目标参数和所处的环境具有很大的工程应用价值[1]。通过对多通道阵列雷达回波模拟器工作原理的研究,本文构建了基于Xilinx FPGA平台的新型雷达目标模拟器,解决了常规模拟器的设计和功能局限性问题,在相关仿真和实验室验证实验的过程中给出了一种多通道雷达模拟器的关键设计技术并分析了其优越性和可升级性,最后经实际使用证明其达到了预期性能。

1 多通道雷达目标模拟器原理

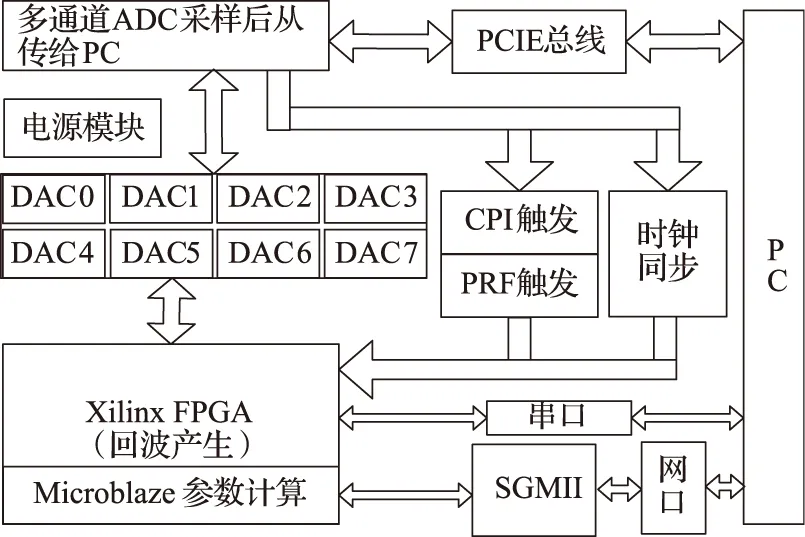

雷达目标模拟器系统组成如图1所示,包括PC侧控制界面(负责传输初始信息)、网络接口电路(千兆网传输目标初始参数信息)、ADC电路和PCIE总线(配合ADC用于采集回波到PC机后验证回波数据正确性)、FPGA核心处理电路、模拟信号输出电路(中频和射频输出)、时钟信号产生和分发电路、脉冲触发电路、电源电路等模块。

图1 系统原理架构

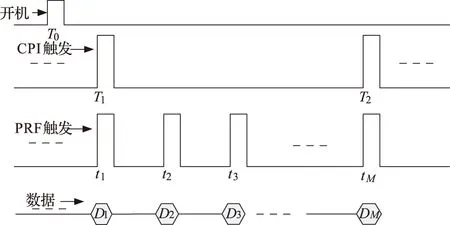

雷达目标模拟器工作时序如图2所示。

图2 模拟器工作原理时序图

开机时刻T0通过界面设定目标初始的距离、速度、方位、信噪比等信息,利用PC侧MATLAB GUI界面接收到的参数通过千兆网使用SGMII(Serial Gigabit Media Independent Interface)模式按照报文格式传输传给Microblaze,利用Microblaze计算当前CPI(Coherent Processing Interval)内的所有点迹和航迹信息。等待T1时刻到达后,按照PRF触发脉冲的顺序,将待模拟目标的参数信息传送给FPGA控制DDS输出。同时,利用这个CPI时间计算下一个CPI,待模拟目标所需的参数信息,等待传输。

目标的初始距离信息、速度信息、角度信息等参数的具体设计公式如下:

时延点数表示为

Ndelay=fsτ(t)

(1)

其中fs表示表示采样率,时延为

(2)

速度控制字表示为

(3)

其中多普勒频率表示为

(4)

相位控制字表示为

(5)

其中△φ表示阵元相位差。

设定雷达目标模拟器中DDS软核的控制字位宽为N,其中fs为采样频率。Microblaze接到初始数据指令后,根据上述公式,按照外部提供的触发脉冲CPI的节奏计算待模拟目标1~N的信息控制参数后,按照报文头、目标号、波束号、频率控制参数、相位控制参数、中频频率、信噪比、阵元相位差的顺序,最后加上结束码依次传输到FPGA内部RAM,用于控制DDS IP core产生LFM(Linear Frequency Modulation)信号。

验证功能实现按照外部触发同步信号即PRF(Pulse Repetition Frequency)脉冲信号,使用DAC输出模拟回波信号,供给雷达信号接收机,用于验证其性能指标。

2 多通道雷达模拟器关键技术

2.1 常规雷达目标模拟器局限性

常规的雷达目标信号的模拟功能主要是针对点目标信号进行常规信号(如线性调频信号、相位编码信号)的目标模拟。这种方法功能单一,一般模拟信号限制在零中频、参数固定不灵活、缺少人机友好界面,并且对于多目标信号和中频信号的模拟能力限制于硬件,可仿真目标的批次较少,实时计算能力欠缺。这必须单独使用核心计算处理芯片实时计算点目标的相关参数信息,增加了硬件成本。如果进行更多通道的回波模拟仿真需要重新修改硬件方案,并且增加大量人力和物力资源耗费,难于后续升级换代。

2.2 硬件设计

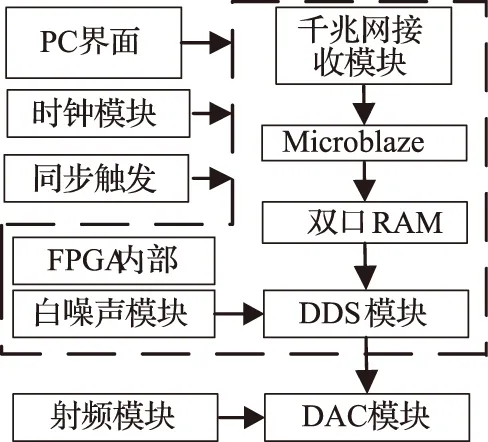

考虑后续升级实现更多目标信号模拟等功能,要综合考虑FPGA逻辑资源情况、I/O管脚数量、速度等级和性价比,最终选择了Xilinx公司的FPGA用于核心处理芯片。使用内部嵌入微处理器Microblaze处理系统,可以用于计算目标参数信息,利用 Block RAM构成双端口RAM,实现Microblaze和FPGA其他逻辑的数据访问。FPGA功能模块如图3所示。FPGA控制信号的分发、计算、传递,是信号处理的核心。它主要包括建立嵌入式千兆以太网硬核,负责和PC机界面进行信息传递,接收雷达目标信号的初始参数包括目标初始距离、初始速度、初始角度、回波信号形式、脉冲宽度、载频等信息[2]。

图3 功能模块设计图

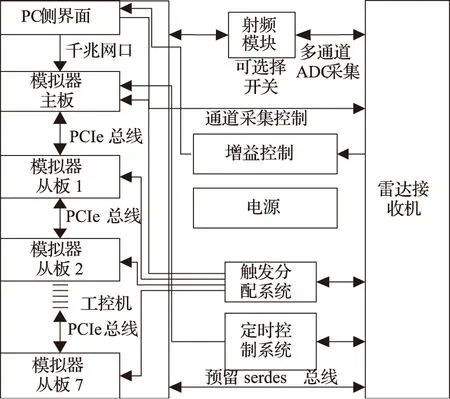

Microblaze处理器利用一个CPI的时间计算下一个CPI时间内的目标参数信息,控制DDS IP core用于产生模拟回波,送给DAC芯片。这样简化了常规雷达目标模拟器设计中必须单独使用计算核心芯片负责实时计算点目标所需的参数,节省了硬件成本。使用人机友好界面可以灵活设定系统参数,更改软件程序,缩短开发周期。本文所述的多通道雷达模拟器在进行更多目标和更多通道的回波模拟时可以增加从板,进行和主板的无缝升级,框图如图4所示。

图4 升级架构框图

通过在工控机中增加模拟器从板板卡和对应的总线后,主板负责接收界面控制信息,计算其他7个从板所需要的目标参数信息和时序触发,然后以广播方式打包发送给每个从板。各个从板根据地址信息接收主板分发数据,控制DDS输出待模拟数字波形,送给DAC产生模拟回波。据此,只需要更改软件算法和驱动程序即可实现快速升级,扩展成更多目标和通道。另外,设计中预留射频模块,包括一本振、二本振、功率放大器和带通滤波器等微波器件,将中频模拟回波混到射频后输出,供给雷达接收机验证性能参数指标。

2.3 软件设计

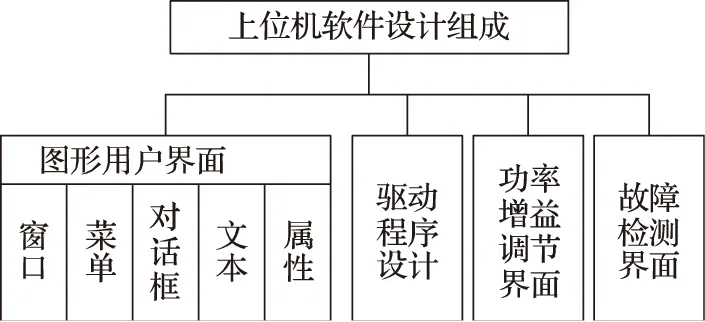

软件设计包括界面设计和逻辑设计。MATLAB GUI提供了图形用户界面设计功能。图形用户界面包含控件、菜单、按钮组、面板、工具栏、表等设计对象[3]。本文主要针对雷达目标的具体参数信息,采用MATLAB软件,调用相应功能软件包并计算对应目标参数。上位机软件组成如图5所示。

图5 上位机软件界面组成

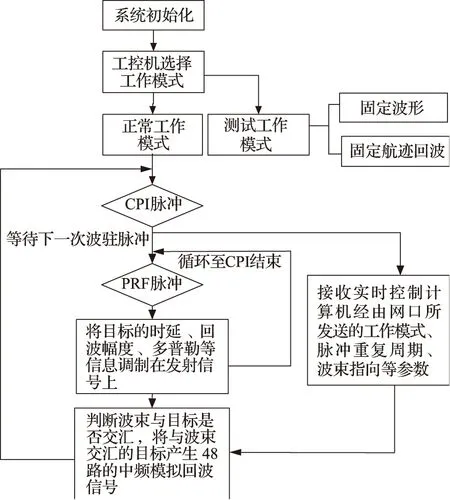

系统初始化完毕后,在测试工作模式时产生固定测试点频信号,在正常工作模式时根据CPI触发间隔,实时通过微处理器Microblaze计算DDS IP core所需要的控制信息传输传送给FPGA,然后按照PRF触发脉冲信息产生模拟回波送给DAC芯片产生待模拟回波信号。

雷达目标模拟器的逻辑代码设计使用Xilinx公司提供的ISE设计套件。逻辑程序设计流程图如图6所示。

图6 逻辑设计流程图

FPGA通过千兆以太网接收界面信息。按照PRF脉冲设定对应目标的控制参数传递给FPGA内嵌的Microblaze软核,其按照CPI的节奏,利用上个CPI的时间内计算下次CPI点目标所需要的参数信息,通过双口RAM按照地址映射传递给DDS IP core进行点目标的点迹和航迹的模拟。

3 实验验证

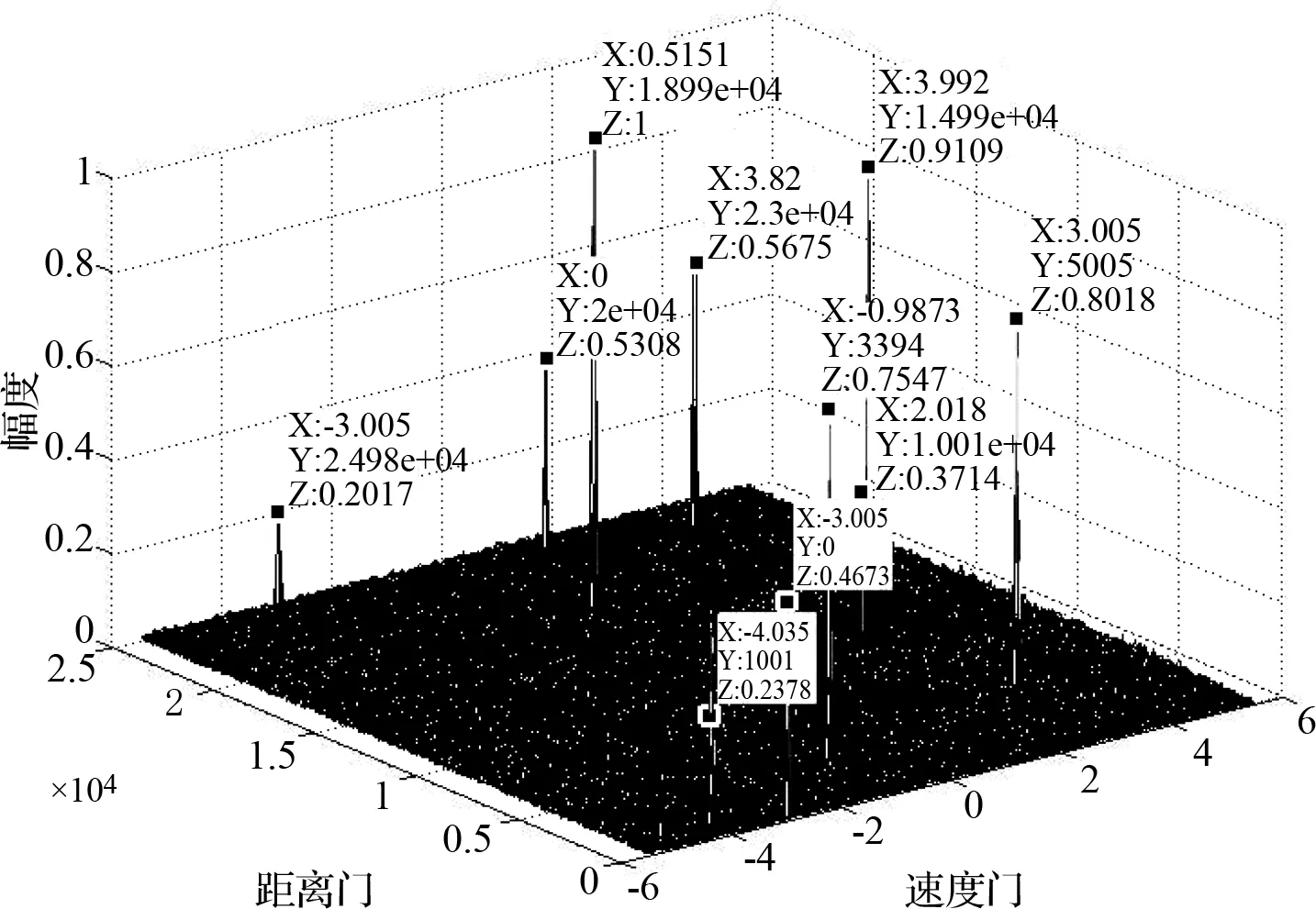

通过MATLAB GUI界面设定待模拟目标的距离分别为0、1、3.4、5、10、15、19、20、23、25 km。速度对应分别为-3、-4、-1、3、2、4、0.5、0、3.8、-3 m/s。仿真设定雷达载频为13.65 GHz,雷达信号脉冲重复周期为1 ms,信号带宽为30 MHz。基于上述参数产生的某单通道回波信号如图7所示。高斯白噪声是通过线性移位寄存器产生伪随机数后根据独立分布的中心极限定理产生。

图7 雷达目标模拟回波

经过雷达信号接收机采集导入PC机后使用MATLAB进行验证,得到图8所示结果。可以看出,经过MTD处理后估计出的距离分别是0、1.001、3.394、5.005、10.010、14.990、18.990、20、23、24.980 km。速度对应分别为-3.005、-4.035、-0.987、3.005、2.018、3.992、0.515、0、3.820、-3.005 m/s。根据距离门和速度门的定义可以得到目标模拟器模拟产生的回波数据是正确的,并且实现了多通道、多目标、可调节信噪比、方便升级等功能,同时也验证了系统方案的可行性。

图8 MTD后的结果

4 结束语

本文详细阐述了基于FPGA和MATLAB GUI软件界面的多通道雷达目标模拟器设计方法。该方法考虑了基带、中频和射频信号,可仿真多批点目标信号,不仅简化了数据运算,而且具有人机友好界面,方便后续升级,便于工程实现。计算机仿真结果和实验结果表明了该方法的有效性。该方法已经应用于某型号多通道雷达目标模拟器中,并对其他类型目标模拟器也有借鉴意义。

[1] 徐国平,等.雷达目标信号模拟器的设计与实现[J].电子设计工程,2013(16):31-33.

[2] 衣玮,袁湘辉,左雷,等.雷达模拟器的目标运动数据算法研究[J].船舶电子工程,2014(12):53-57.

[3] 刘卫国,蔡立燕,陈昭平,等.MATLAB程序设计教程[M].北京:中国水利水电出版社,2010:13-17.

Design of radar target simulator based on FPGA

ZHUANG Lei, ZHANG Hai-long, LI Sai-hui, WU Yuan-qing

(No.724 Research Institute of CSIC, Nanjing 211153)

The generation mechanism and characteristics of the multi-channel simulated radar target signals based on the FPGA are introduced, and the design and the limitations of the conventional radar target simulators are analyzed. The key design and the upgradability technique of a multi-channel radar target simulator are discussed emphatically. The simulation and test results indicate that the multi-channel radar target simulator is verified to be correct and effective.

radar target simulator; FPGA; upgradability

2016-08-30;

2016-09-10

庄雷(1984-),男,工程师,研究方向:雷达总体;张海龙(1989-),男,助理工程师,硕士,研究方向:雷达信号处理;李赛辉(1984-),男,工程师,硕士,方向:雷达信号处理;吴元清(1989-),女,助理工程师,硕士,研究方向:T/R组件。

TN955.2

A

1009-0401(2016)04-0045-04