基于I2C总线的数模混合电路设计与验证

魏榕山,钱振煌

(福州大学 物理与信息工程学院,福建 福州350116)

基于I2C总线的数模混合电路设计与验证

魏榕山,钱振煌

(福州大学 物理与信息工程学院,福建 福州350116)

模拟集成电路一般难以自动校准,并且IO管角较多,为使其更加高效智能,文中提出一种基于I2C总线的数模混合电路。利用I2C从机接口,对模拟控制寄存器组进行读写,完成对芯片功能的控制。并采用System Verilog、随机测试和覆盖率收集等验证技术搭建电路验证平台,对验证结果进行自动化分析,使代码覆盖率达到97%以上。结果表明,电路不仅达到预期功能,还减少了芯片管角,使电路更加智能可控。

I2C总线;FPGA验证;数模混合

I2C总线(Inter Integrated Circuit)是飞利浦公司提出的一种双向半双工协议,它与其他的总线相比突出的优势就是接口数少,通讯效率高[1-5]。现如今,I2C总线被广泛使用,其中包括德州仪器、英特尔、美信等[6]。本文基于I2C总线协议设计了一种用于控制低压差线性稳压器(Low Dropout Regulator,LDO)的从机接口电路,使模拟控制寄存器组可供片外进行读写,同时也减少了IO管脚个数。

1 I2C从机数模混合电路设计

1.1 I2C从机数模混合电路结构

如图1所示,整体数模混合电路由从机接口模块和LDO模拟电路模块构成。

图1 I2C从机数模混合电路结构图

I2C从机接口电路包含数据缓存接口、模拟电路控制寄存器组和控制电路。

在电路运行时,芯片通过I2C总线的SCL和SDA和外界进行通信。当从机接收到读操作后,数据从寄存器组流向数据缓存接口,然后通过I2C总线传输给主机。相反,如果是写操作,数据从总线传输到数据缓存模块,然后传送给模拟寄存器组。控制电路则用于产生各个状态所需要的跳边信号,让数据的发送接收能够有序的进行。通过以上方式,可以实现对模拟控制寄存器组的读写。

在模拟电路中,模拟寄存器组的每一位都相当于一个开关,它们分别与带隙基准、电荷泵输出电压、时钟占空比电路和模拟信号关键测试节点相连接,从而在一定程度上实现了LDO的可控可调。

1.2 I2C总线的读写操作

I2C总线由SCL和SDA两条串行总线构成,分别为时钟线和数据线。在总线上发起通信的为主机(Master),被寻址的器件为从机(Slave)[7-8]。本文所设计的数模混合电路也专门用于从机接口。

图2 总线电平传输过程

图2为总线电平传输过程,在数据传输时,主机先向从机发送需要寻址的从机地址和读写位(RW),当RW为高时代表读,为低时代表写。从机接收到这8位数据后,与自身的器件地址进行对比,如果一致,则表示配比成功,从机把SDA上的信号拉低,发送应答信号。

接着,主机收到从机的应答信号后,开始向从机发送数据,每发送完8位数据(DATA),主机将等待从机的应答(ACK)信号,如果应答信号为低,则继续发送,直到发送完毕。

1.3 I2C从机接口的设计

设计主要基于Verilog HDL语言,并采用状态机的方法实现[9]。根据I2C总线协议的内容,分为空闲、从机地址应答、寄存器地址、寄存器地址应答、数据和数据应答6个状态。

图3 I2C从机电路接口状态图

如图3所示,在开始时,电路处于空闲状态,并实时监测总线上的信号,当检测到接收的数据与自身地址一致时,电路进入从机地址应答状态。此时,从机将SDA总线拉低,根据主机发送的读写位(RW)判断电路的状态跳转。如果RW位为高,则电路进入数据状态;如果RW为低则进入寄存器地址状态。

电路在寄存器地址状态时,会把收到的寄存器地址保存,并进入寄存器地址应答状态,给主机发送应答信号。

在应答信号完成后,电路跳转为数据状态,此状态需要根据RW的值,进行主机与从机之间的数据传输。如果RW为1,则从机向主机发送数据;如果RW为0,则主机向从机发送。发送完8位数据后,状态机自动跳转为数据应答阶段。此状态将SDA信号拉低,告知主机这8位数据传输完毕。同时,状态机根据STO信号进行状态跳转,如果STO为0,电路进入数据状态,继续发送或接受数据。如果STO=1则表示传输完毕,状态机跳转为空闲状态。

2 I2C从机数模混合电路的验证

此设计基于System Verilog语言在Synopsys公司的VCS软件,搭建了对I2C从机接口电路的行为级仿真平台,验证其功能的正确性和完整性。

2.1 I2C从机验证平台的搭建

如图4所示,仿真环境主要包括发生器、检验器、驱动器和检测器[10]。

图4 I2C从机验证平台结构图

在测试开始,发生器随机产生读、写命令,然后通过不同的命令生成访问I2C从机所需要的从机地址、模拟寄存器组地址和数据,用邮箱的方式分别将其发送给驱动器和检验器。驱动器收到发生器的数据后,对读写数据进行解析,将数据串行发送给待测电路。监测器主要负责监测被测电路的输出,并将接收到的信号传给检验器[11]。检验器将收到的信号值与期望值进行比对,判断结果的正确性,最后将结果打印出来。

2.2 验证结果分析

图5 仿真时序波形图

图5为验证平台的仿真时序波形图,SCL和SDA为时钟线和数据线,mem_do_out0、mem_do_ou1、mem_do_out2、mem_do_out3、mem_do_out4分别为5组模拟控制电路寄存器组,每一组中包含8位寄存器。由图中可以看出,寄存器组随着SCL和SDA的变化,数据也发生改变,实现了对数据的读写功能。

2.3 I2C从机验证覆盖率收集

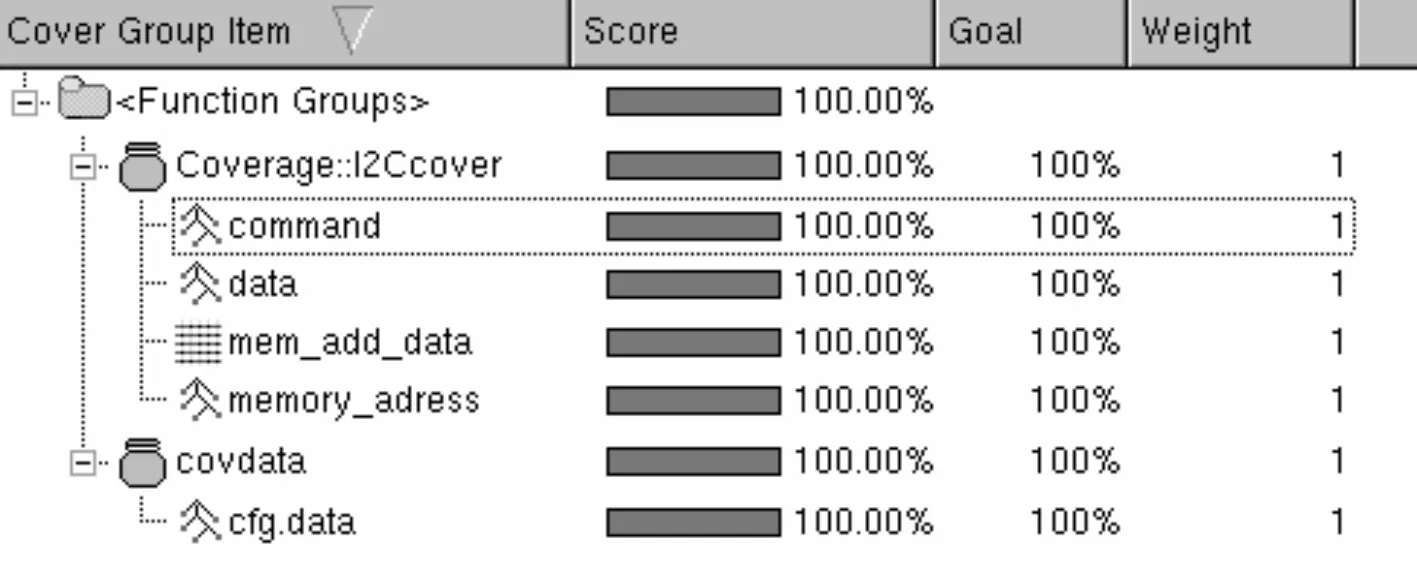

对于验证本身主要看的指标有功能覆盖率(Function Coverage)和代码覆盖率(Code Coverage)[12]。从图6可以看出,功能覆盖率已经达到100%。

图6 I2C从机接口电路功能覆盖率图

图7 I2C从机接口电路代码覆盖率图

衡量验证进展最简单的方式就是使用代码覆盖率[13]。从图7中可以看出,代码覆盖率达到了97.38%。需要注意的是,验证功能有可能不够完善,验证本身可能存在一些漏洞没有检测出来,所以也不能完全排除功能没有任何问题。

2.4 FPGA验证

本文采用两块FPGA板模拟I2C的主机和从机,对设计进行验证[14]。SignalTap II能够捕获和显示可编程单芯片系统(SOPC)设计中的实时信号状态,这样开发者可以以系统级的速度观察硬件和软件的交互作用[15]。电路通过Quartus II编译烧写入DE2-115 FPGA开发板,使用SignalTap II软件捕捉电路的时序波形。图8为I2C从机接口电路FPGA时序图。

工作过程:首先,主机寻址从机地址0xA0h,然后发送需要访问的模拟寄存器地址0x01h,接着写入数据0xA5h,最后将此寄存器的值读出为0xA5h,由此可知,结果正确。

图8 I2C从机接口电路FPGA时序

3 结束语

本文基于I2C总线,设计了一款用于模拟电路的I2C从机接口电路。采用System Verilog、随机测试和覆盖率收集等验证技术搭建的电路验证平台测试结果表明,代码覆盖率达到97%以上,电路不仅达到预期功能,还减少了芯片管角,使模拟电路变得更加智能的同时,也增加了它的可控性和可测性。

[1] 黄乐天. 数模混合集成电路设计课程研究[J]. 实验科学与技术, 2012(S1):226-229.

[2] 郭玲. 数模混合电路设计方法的研究及其在智能传感器设计中的应用[D]. 广州:华南理工大学, 2005.

[3] 鲁斌. 数模混合集成电路设计技术研究[D]. 合肥:合肥工业大学, 2006.

[4] 董珍珍. 数模混合型滤波器设计及其仿真[D]. 西安:西安理工大学, 2009.

[5] 路永坤. 用Verilog HDL实现I2C总线功能[J]. 电子技术应用, 2004,30(4):67-69.

[6] 张铖瑶. 用于数字输出传感器的I2C/SPI总线设计[D]. 哈尔滨:哈尔滨工业大学, 2012.

[7] 牟浩. I2C总线控制器的设计[J]. 科协论坛, 2010(10):56-56.

[8] 林健磊,殷瑞祥. I2C总线串行数据接口的Verilog实现[J]. 微计算机信息,2007, 23(23):43-44.

[9] 王金明,杨吉斌. 数字系统设计与Verilog HDL[M]. 北京:电子工业出版社,2002.

[10] 杨鑫,徐伟俊,陈先勇,等. SystemVerilog中的随机化激励[J]. 中国集成电路,2007, 16(10):37-41.

[11] Keaveney M, Mcmahon A, O’Keeffe N, et al. The development of advanced verification environments using System Verilog[J]. Journal of Environmental Management, 2008, 87(3):325-330.

[12] 罗登富,赵建明. 基于覆盖率的集成电路验证[J]. 现代电子技术,2009, 32(14):115-119.

[13] 克里斯·斯皮尔.System Verilog 验证[M]. 北京:科学出版社,2009.

[14] 吴继华,王诚.Altera FPGA/ CPLD 设计:高级篇[M]. 北京:人民邮电出版社,2005.

[15] 郭佳佳,胡晓菁,王永良.使用SignalTapⅡ逻辑分析仪调试FPGA[J].今日电子,2005(5):45-47.

Design and Verification of Mixed-signal Circuits Based on the I2C Protocol

WEI Rongshan, QIAN Zhenhuang

(School of Physics and Information Engineering, Fuzhou University, Fuzhou 350116, China)

Generally, it’s difficult to calibrate analog integrated circuits and reduce their IO pins. In order to make the analog integrated circuit become more intelligent and efficient, a mixed-signal circuit based on I2C protocol was proposed, which made a set of registers be read and written. An I2C interface circuit verification environment was built by System Verilog, random testing and collecting coverage to automatically analyze the result, which made the code coverage rate reach more than 97% .The results showed that the circuit not only achieved the desired functionality, but also reduced the chip pins and made it more intelligent and controllable.

I2C protocol; FPGA verification; mixed Signal

10.16180/j.cnki.issn1007-7820.2016.12.003

2016- 03- 03

国家自然科学基金资助项目(61404030)

魏榕山(1980-),男,博士,副教授。研究方向:微纳电子器件,集成电路设计。钱振煌(1989-),男,硕士研究生。研究方向:集成电路设计。

TN432

A

1007-7820(2016)12-009-03