两级高轻载效率数字功率变换器的研究

史永胜,田卫东,高静茹,李 利,高丹阳

(陕西科技大学 电气与信息工程学院,陕西 西安 710021)

两级高轻载效率数字功率变换器的研究

史永胜,田卫东,高静茹,李利,高丹阳

(陕西科技大学 电气与信息工程学院,陕西 西安 710021)

针对电源轻载效率低的问题,提出了一种数字(DSP)集成控制方法。该方法同时控制PFC级直流输出母线电压和全桥部分的开关时序,轻载时,通过调整母线电压并降低开关频率来减小开关损耗和环路电流损耗。实验结果表明,该变换器在10%额定负载下效率能达到90%,在5%额定负载下效率仍高于80%。

母线电压;开关方法;移相全桥(PSFB);轻载效率

0 引言

电源的轻载效率是当今信息时代电源设备进一步发展的必要关注课题之一。

为提高轻载效率,提出了许多方法:针对移相全桥变换器,文献[1-3]从死区时间角度出发,引入辅助电路或直接加宽死区时间,这改善了轻载效率,但是电路复杂度和负载实时灵活性降低,加上额外的损耗,限制效率的进一步提升;文献[4]通过动态调整母线电压降低开关损耗,但是没有对后级电路做进一步的研究;文献[5-6]通过分模式控制,提高了 DC/DC部分的轻载效率,但是没有考虑母线电压对效率的影响。

本文研究的两级变换器如图1所示,在轻载情况下,母线电压动态调整在降低开关管应力的同时使移相全桥的占空比保持在最大值,并且全桥部分工作在PWM控制和PWM Burst控制模式下,以进一步减小开关损耗和环路电流损耗;当负载增加到一定值时,全桥变换器改用移相控制。最后,基于TI的DSP平台(TMS320F28335),设计一台 600 W的试验样机验证控制方法的正确性和有效性。

图1 两级功率变换器结构图

1 两级结构及其集成控制系统设计

按照服务器系统架构(Server system architecture,SSI)标准[7],该电源系统分为两级,前级 AC/DC变换器,后级DC/DC变换器,如图1所示。前级PFC广泛采用 Boost变换器结构[8-9],还要满足 EN61000-3-2等的对电流谐波的要求,同时为达到功率因数校正的目的,对输入电压采样并作为输入电流的参考值,使输入电流与输入电压同相位;后级移相全桥(PSFB)在无辅助原件条件下完成零电压开关且适用于大、中功率场合的特点使它在DC/DC部分得到广泛应用[10]。

图2为集成控制时序图,按照输出电流值大小主要分为三种模态:模态1,极轻载(0~5%),母线电压保持在较低水平(340 V),直接采用PWM驱动信号,此时,原副边的电流都很小,整流体二极管导通损耗极小,原边几乎无环流;模态 2,轻载(5%~20%),进入 PWM Burst控制模式,该模式下,母线电压还是保持在较低水平(340 V),当输出电压超过其额定值的1%不再发出驱动信号,否侧有驱动信号,而且,在该模式下的开关频率低于正常工作开关频率,且母线电压值较低,使得轻载主要的开关损耗大大降低;模态3,进入移相控制模式,该模式下能自然实现零电压开关,且母线电压动态调整,使占空比保持在最大值,从而减小损耗,提升整体效率,当重载(70%~100%)时母线电压保持在400 V以满足重载保持时间的要求[11]。

图2 集成控制时序图

图3为母线电压自适应调整流程图,母线电压不断调整使移相全桥的占空比保持在最大值 0.48T,0.2T的时间为瞬态裕度和死区时间。

2 损耗分析

分别对移相控制和PWM控制下的全桥变换器做损耗分析。

2.1移相控制下的全桥变换器损耗

根据参考文献[10-11],原边开关管的关断损耗Poff_p:

图3 母线电压自适应调整流程图

式中,td(off)为开关管关断时间,Coss_p为原边开关管等效并联电容,IPP为原边峰值电流。

原边开关管开通损耗为 Pon_p:

其中,Ip2为原边电感续流终止电流。

原边单只开关管通态损耗 PMOSFET_con_p:

式中,I1,rms是变压器正常工作原边电流有效值,是原边环流期电流有效值。

同步整流管的通态损耗 PMOSFET_con_s:

式中 IDS_s_rms是流过管子的电流有效值,电感和变压器通态损耗 Pinductor_con,PTR_con:

式中 IL,rms为电感电流有效值。

磁芯损耗 Pcore:

2.2PWM控制下的全桥变换器损耗

原边开关管开关损耗 PSW_loss,p:

副边开关损耗 PSW_loss,s:

开关管的通态损耗 PMOSFET_con_p:

变压器通态损耗 PTR_con:

电感与磁芯损耗见式(5)、式(7)。

2.3损耗分布与对比

图4为轻载及极轻载时,一般移相控制和本文集成控制下的损耗对比,集成控制下效率提升了2.14%。

图4 轻载及极轻载模式下移相控制与集成控制损耗

由图2知,在轻载与极轻载模式下变换器开关管有效工作时序均为PWM信号。结合图5中变换器理论效率曲线,可知PWM全桥变换器在轻载和极轻载情况下确实能提高变换器的轻载效率。

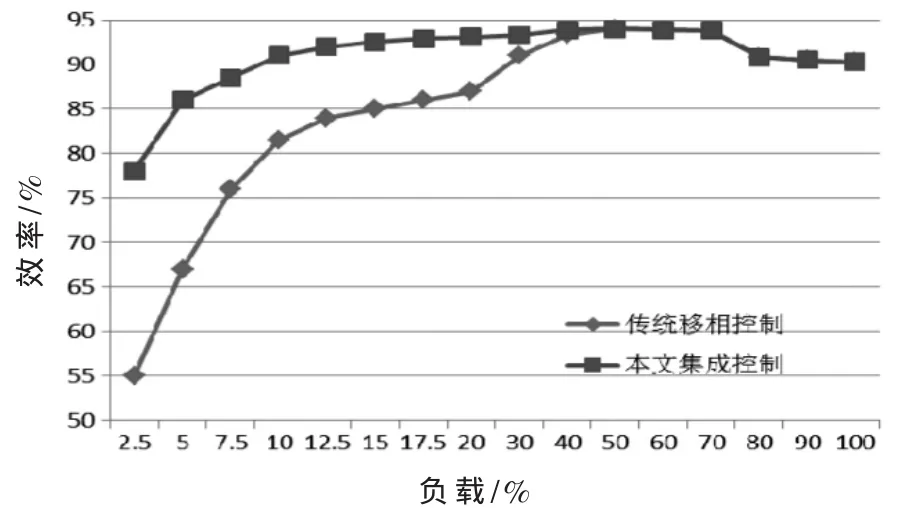

图5 效率曲线

3 仿真与实验分析

首先基于Psim9.0对电路进行了仿真。主要实验参数设计如下:谐振电感 Lr=48 μH,变压器变比 n=54:8,开关频率fs=100 kHz,死区时间 tdead=300 ns。

如图6、图7分别为轻载和极轻载条件下的工作波形,在仿真基础上搭建一台600 W的实验样机。实验表明,该变换器在达到高轻载效率的同时能保证正常工作较大负载范围内实现ZVS。图8为Q1驱动波形图,其他驱动波形类似。

图6 轻载工作波形

图7 极轻载工作波形

图8 Q1零电压转换

图9 整机效率

图9将本文中集成控制下的变换器与传统全桥变换器的整机效率作比较。可以看出,在低于5%额定负载的情况下,效率能维持在70%以上,5%~20%额定负载情况下效率达到90%以上,远高于传统全桥变换器效率。原因在于,本论文搭配输出电压可调的PFC并分模态控制变换器,使得变换器具有较高轻载效率。另外,数字控制减少了控制环路器件,减少了整机损耗。

4 结论

本文重点研究了两级功率变换器的轻载效率,结合数字控制技术提出了一种集成控制策略。在轻载和10%额定负载下效率分别提升了 6.9%、10.0%,可以对服务器、适配器等电源的发展起到进一步推动作用。

[1]KIM Y D,CHO K M,KIM D Y,et al.Wide-range ZVS phase-shift full-bridge converter with reduced conduction loss caused by circulate ingcurrent[J].IEEE Transactions on Power Electronics,2013,28(7):3308-3316.

[2]ZHONG C,SHASHA L,LIANGCHEN S.A soft switching full bridge converter with reduced parasitic oscillation in a wide load range[J].IEEE Transactions on Power Electronics,2014,29(2):801-811.

[3]KIM D Y,KIM C E,MOON G W.Variable delay time method in the phase-shifted full-bridge converter for reduced power consumption under light load conditions[J]. IEEE Transactions on Power Electronics,2013,28(11):5120-5127.

[4]LAI Y S,SU Z J.Novel on-line maximum duty point tracking technique to improve two-stage server power efficiency and investigation into its impact on hold-up time[J]. IEEE Transactions on Industrial Electronics,2014,61(5):2252-2263.

[5]史永胜,高丹阳,刘言新,等.数字控制DC/DC变换器轻载效率的研究[J].电子技术应用,2015,41(8):113-116.

[6]史永胜,余彬,王喜锋,等.基于DSP的高轻载效率数字DC/DC变换器[J].电子器件,2015,38(2):338-342.

[7]李冬,阮新波.三种服务器电源系统的比较分析[J].中国电机工程学报,2006,26(13):68-73.

[8]JANG Y,JOVANOVIO M M.A bridgeless PFC boost rectifier with optimized magnetic utilization[J].IEEE Transactions on Power Electronics,2009,24(1):85-93.

[9]LAI Y S,YEH C A,HO K M.A family of predictive digitalcontrolled PFC under boundary current mode control[J]. IEEE Transactions on Industrial Electronics,2012,8(3):448-458.

[10]张运成.倍流同步整流移相全桥直流变换器的研究[D].哈尔滨:哈尔滨工业大学,2014:11-18.

[11]LAI Y S,SU Z J,CHEN W S.New hybrid control technique to improve light load efficiency while meeting the hold-up time requirement for two-stage server power[J]. IEEE Transactions on Power Electronics,2014,29(9):4763-4775.

Research on two-stage power converter based on digital control with high light load efficiency

Shi Yongsheng,Tian Weidong,Gao Jingru,Li Li,Gao Danyang

(College of Electrical and Information Engineering,Shaanxi University of Science&Technology,Xi′an 710021,China)

To solve the disadvantage of traditional-anlog power supply low and less efficiency under light load condition,the scheme of digital integrated control based on the DSP is proposed.The basic idea of the proposed control technique is to control both DC-link voltage of PFC stage and switching method of full-bridge stage.Under light load condition,the output voltage of PFC stage is adjusted dynamically and switch frequency to reduce the switching losses and circulating current losses.The results indicate,in 10%load condition,the efficiency reaches 85%,and in 5%load condition,the efficiency is higher than 80%.The integrated control scheme can improve efficiency.

DC-link voltage;switching scheme;phase-shift full-bridge converter(PSFB);light load efficiency

TM461

A

10.16157/j.issn.0258-7998.2016.08.040

2016-01-30)(

2016-02-09)(

2016-01-19)

史永胜(1964-),男,博士,主要研究方向:特种电源和先进光电器件。

田卫东(1990-),通信作者,男,硕士研究生,主要研究方向:AC/DC变换器,E-mail:1101284761@qq.com。

高静茹(1991-),女,硕士研究生,主要研究方向:新型电子器件和AC/DC变换器。

中文引用格式:史永胜,田卫东,高静茹,等.两级高轻载效率数字功率变换器的研究[J].电子技术应用,2016,42 (8):162-165.

英文引用格式:Shi Yongsheng,Tian Weidong,Gao Jingru,et al.Research on two-stage power converter based on digital control with high light load efficiency[J].Application of Electronic Technique,2016,42(8):162-165.