基于WISHBONE总线的双向PCI高速传输接口设计*

梁 烨,简献忠,肖儿良,姜冠祥,蔡留美,郑照平

(1.上海理工大学 光电信息与计算机工程学院,上海 200093;2.上海雄博精密仪器股份有限公司,上海200444)

基于WISHBONE总线的双向PCI高速传输接口设计*

梁烨1,简献忠1,肖儿良1,姜冠祥2,蔡留美2,郑照平2

(1.上海理工大学 光电信息与计算机工程学院,上海 200093;2.上海雄博精密仪器股份有限公司,上海200444)

针对目前设计的PCI卡存在传输速度慢、复杂度高和购买PCI核价格昂贵的问题,提出了一种基于 WISHBONE总线的PCI接口双向传输设计的新方案。系统采用开源的WISHBONE总线的PCI接口的IP核,设计了基于Xilinx Aritx-7系列FPGA芯片的PCI接口卡,该卡兼容5 V和3.3 V电平;采用 DMA(直接内存存取)方式进行高速数据传输。实验表明,设计的PCI接口运行在主模式时,数据传输速率可达65×32 Mb/s,传输速率明显提升,且数据传输准确稳定,达到了设计目的,为高速PCI接口设计提供了一种新的思路。

PCI接口;DMA;高速传输;WISHBONE总线

0 引言

PCI总线是目前推出的一款高性能局部总线[1],能同时满足高数据传输和高功率输出,是中频数据采集与处理模块的理想总线接口[2]。PCI局部总线不受制于处理器,为中央处理器及高速外围设备提供了一座桥梁[3],用户可将高速外设通过局部总线直接挂接到 CPU总线上,使其与之匹配,从而打破了数据传输的瓶颈,使高性能 CPU的功能得以充分发挥。

PCI总线接口的设计思路总体上可分为两种方法,一是采用专门的接口芯片,二是采用可编程逻辑器件[4-5]。这两种方法在不同角度皆有利弊。

文献[6]提出专用芯片可以将复杂的总线接口转换为相对简单的用户接口。用户可集中精力于应用设计,而不是调试PCI接口。但这种方式造成了一定的资源浪费,缺少灵活性。为了解决这些弊端,文献[7]提出采用Xilinx、Altera以及 Atmel等公司的可编程逻辑器件 IP核实现PCI总线接口。最常用的IP核是Altera公司的PCI MegaCore和Xilinx公司的PCI LogiCore,但采取这两种IP核的费用不菲,且主模式设计难度较高,让大多数研究人员望而却步。文献[8]论述了 PCI主桥的的应用和WISHBONE片上总线技术,提出了使用单片机和FPGA架构实现基于PCI Bridge核的被动模式的PCI系统。

本文针对两种方式的不足,在文献[8]的基础上,针对WISHBONE总线特点及国外开放IP组织Open Cores网站免费提供的开源PCI-WISHBONE桥核,优化该IP核主传输模块状态机程序,仅使用一片可编程逻辑器件嵌入用户程序,将时钟频率提至66 MHz,首次实现了一种以高速DMA方式传输、主从共模的PCI接口设计。

1 PCI总线与PCI-WISHBONE桥核

1.1PCI总线

PCI总线是同步传输协议,所有PCI操作均同步于时钟。总线时钟有 33 MHz、66 MHz两种频率,位宽分为32 bit和64 bit两种,最大传输速率为 264 MB。系统中PCI总线的最大带宽可达:66×106×32=2.112 Gb/s。

重要的是,PCI可以支持一种名为线性突发的数据传输模式,可确保总线不断满载数据。这种线性的或顺序的寻址方式,意味着可以由一个地址起读写大量数据,然后每次只须将地址自动加1,便可接收数据流内下一个字节的数据。线性突发传输能更有效地动用总线的频带宽传输数据,减少无谓的寻址操作。同时,PCI对总线主控及同步操作的支持有助于改善PCI的性能,即可将任何一个具有处理功能的外围设备暂时接管总线,以加速执行高吞吐量、高优先次序的任务。PCI独特的同步操作功能可确保CPU能与这些总线同步操作,毋须等待后者完成任务。

1.2PCI-WISHBONE桥核

PCI-WISHBONE IP核提供了一个PCI总线和WISHBONE总线之间的接口,兼容PCI 2.2协议,支持WISHBONE SoC互联协议B版本。它适用于32位PCI接口,包含独立的主桥、从桥功能模块,支持启动程序与目标命令功能,例如存储器读写、I/O读写、中断应答等操作。

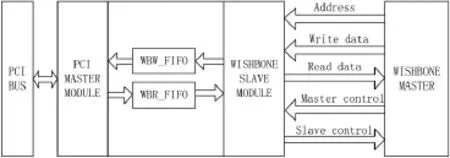

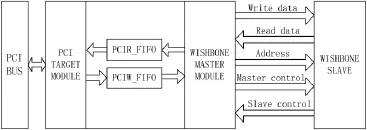

如图1、图2所示,PCI-WISHBONE桥核包括2个单元:PCI主单元和从单元,每一个单元都拥有自己的一套功能支持桥接操作。例如图1,PCI主单元与WISHBONE主单元共同处理WISHBONE总线起动的交易。首先,由WISHBONE从接口发起信号占用PCI总线,若PCI总线响应成功,WISHBONE接口将传输数据,地址以及命令经由 FIFO,通过 PCI接口传至 PC机内存空间。图2为PCI从模式机制,主要处理由上位机启动的事务,同上述主模式基本一致,此处不再叙述。

图1 PCI主单元结构

图2 PCI从单元结构

2 PCI高速传输接口设计

2.1硬件架构设计

本文设计的双向高速数据传输系统基于FPGA平台,以开源的PCI—WISHBONE软核为核心搭建串行通信接口平台,使其成为PCI总线与用户逻辑之间的桥梁,避开复杂的 PCI总线协议。其采用Xilinx公司的XC7A200T-2FFG1156主芯片作为硬件核心,结合基于WinDriver的驱动程序,采取规格为640×512的图像作为模拟数据源,以乒乓方式轮流读写主机内存,实现了高速图像数据的双向传输。

在硬件方面,根据PCI总线规范2.2版,当PCI接口引脚M66EN是高电平时,总线时钟频率可控制在33 MHz~ 66 MHz范围内,反之为0~33 MHz。该模块设计原理图如图3所示,用户可使用跳线帽自由控制PCI总线时钟频率。当引脚2与1相接时,总线时钟频率高达66 MHz。

图3 PCI总线时钟模块原理图

2.2PCI-WISHBONE桥核主模式传输设计

PCI-WISHBONE桥核内置功能接口允许用户端访问PCI总线,用户可将其设计为主模式传输方式,设计方案如下:

pci_constants、bus_commands和 pci_user_constants是桥核可外部修改的3个配置文件。用户可将其设置成客户端应用(Guest)与主端应用(Host)。本文设计采用Guest模式,支持 PCI总线的主机系统连接。在接通电源时,该设备独立软件扫描主机系统中任何连接PCI插槽的设备,主机系统进行配置周期,PCI桥和连接到主机系统的所有其他PCI设备在上电复位后响应。下面的步骤必须以正确的顺序来执行,以确保适当的PCI桥的操作:

(1)配置所有PCI基地址寄存器。

(2)启用PCI主操作和响应内存与I/O空间的从操作。

(3)配置合适的PCI配置空间Type00 Header寄存器。

(4)前3个步骤完成后,所有的配置寄存器可以在PCI Image0地址范围内使用存储器读写命令进行访问。而其它寄存器可配置合适的应用。

(5)当配置好所有的PCI桥寄存器后,软件便可以通过PCI从单元访问从设备或通过WISHBONE从接口启用主设备来访问PCI总线。

PCI-WISHBONE桥核采取中断机制,能够应对不同的事件产生中断,由中断控制和中断状态寄存器控制中断请求的产生。作为Guest桥时,由PCI总线INTA#引脚产生中断请求;而作为Host桥时则通过WISHBONE总线上INTA_O引脚发起中断。中断控制寄存器用于使能/禁止不同来源的中断。中断状态寄存器用于确定中断源,并清除中断请求。

2.3DMA双向传输状态机优化设计

为了方便测试,本文使用Verilog语言设计实现了一种规格为640×513的图像数据源,该数据流以62.5 MHz的同步时钟发送,由帧结束信号和图像有效数据组成。其中单副图像数据位宽为16,以列的形式传输,每帧图像结尾增加帧结束信号标志(第513行)。

为了提高传输速率,驱动程序需申请两段可读写内存块,将2个内存首地址通过从模块传递给FPGA,保存在寄存器中。同时,当驱动程序检测到PCI卡时,给予合适的中断、传输命令并及时回馈状态信号,这样驱动程序与FPGA完成交互。

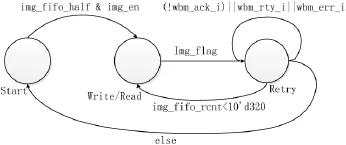

如图4所示,根据传输流程定义4种状态,分别为开始,读操作,写操作以及重试。状态机上电复位后处于Start状态,数据进入 PCI后,由状态机分辨上位机的命令(Img_en)发起内存读写事务。此时由于PCI的传输速率(66 MHz)远大于图像速率(62.5 MHz),需将数据暂存于FIFO中,等到上位机允许传输并缓存数据达到既定数量时(img_fifo_half),状态机转向读写操作状态。

图4 主模块状态机示意图

在 Read/Write状态下,对应的地址和数据将传给wbm_adr_o和wbm_dat_o信号线,传输完毕后进入 Retry状态。当主桥同PCI总线握手后,通过WISHBONE总线回馈给状态机信号(wbs_ack_o,wbs_err_o,wbs_rty_o,分别表示传输成功、错误和重试),从而继续发起下一次事务或重复本次事务直至本幅图像传输完毕。

当检测到图像帧结束标志时,预示着该幅图像传输即将完毕,此时FPGA会产生一个高位信号传至PCI接口中的INTA#引脚(中断引脚)通知上位机。一方面驱动程序以电平检测方式分辨出该信号,迅速清除中断并读取内存空间,保存数据或显示图像;另一方面主模块切换内存首地址,进行下一幅图像传输。乒乓传输方式的采用,不仅提高了传输速率,更给驱动程序保留处理时间。

3 实验验证

PCI传输系统程序主要包括模拟源和 PCI传输模块,均使用Xilinx公司的ISE14.4软件进行开发,硬件仿真软件ISIM进行仿真。数据处理方面可将16位的模拟源数据(img_in[15:0])与累加的内存地址进行拼接处理后分别送入PCI主模块中(wbm_adr_o[31:0]和wbm_dat_o [31:0])。

Xilinx公司7系列 FPGA芯片的基本逻辑单元称为CLB,每个 CLB包含 2个 Slices,每个 Slices由 8个寄存器(Registers)和 4个 6输入的查找表(LUTs)组成。该PCI传输接口设计FPGA资源使用率如表 1所示,寄存器、查找表使用率皆在1%~2%之间,被占用的Slice总数约占总数 5%左右,而触发器使用数量为 1 713,约占总数的34%。

表1FPGA资源使用率总结

表1结果表明,本设计能有效降低FPGA内部硬件资源使用率,在各种资源利用之间达到一种平衡,从而最大限度地发挥器件的功能。

系统搭建如图5所示,驱动程序在 Windows XP操作系统中实现。由于该项目设计了单独的PCB板作为模拟源输入,每行数据为0000-027F数据,经过PCI采集后将传输结果以灰度图像形式展现,每行数据由黑到白,与输入的模拟数据源相对应。经过多次的验证,该系统PCI时钟可达66 MHz,数据稳定,符合设计标准。

图5 PCI系统框架图

4 结论

双向PCI传输接口采用国外网站Open Cores开源的PCI-WISHBONE桥核设计了DMA双向高速传输接口,并实现了以FPGA为主处理器、主机为从处理器的图像传输系统。该接口卡目前已应用到三维免模板磨边机系统中,进行高速数据传输。实验发现,设计的 PCI接口卡具有传输速率高、配置灵活、简便、可移植性强等特点,满足项目高速传输数据的需要。

[1]田小林.基于 FPGA的PCI总线接口设计[J].今日电子,2004(6):60-62.

[2]杨军.基于 IP CORE的PCI接口设计及在数字中频采集与处理模块中的应用[D].成都:电子科技大学,2009.

[3]苏治国.PCI总线接口芯片 PCI9052及其应用[J].世界产品与技术,2002(5):36-37.

[4]HUANG J.Design of online pipeline ultrasonic data acquisition and storage system based on PCI Bus[C].Applied Mechanics and Materials.Trans Tech Publications,2014,651:2296-2300.

[5]Yu Hongsong.Design of general-purpose video image process system based on Compact-PCI bus and FPGA+DSP structure[J].Chinese Journal of Liquid Crystal&Displays,2015,30(2).

[6]曾哲昱.用CPLD实现 PCI总线目标接口[J].测控技术,2002(1):45-47.

[7]邹戗祁.PCI总线的实现方案及其实例[J].电子工程师,1997(7):7-8.

[8]徐江丰.基于WISHBONE片上总线的PCI Bridge核的研究和应用[J].电子设计工程,2005(4):23-26.

[9]WISHBONE Soc Architecture Specification,Revision B.1 [EB/OL].http://www.silicore.net.

The bidirectional interface design of PCI high-speed transmission based on WISHBONE bus

Liang Ye1,Jian Xianzhong1,Xiao Erliang1,Jiang Guanxiang2,Cai Liumei2,Zheng Zhaoping2

(1.School of Optical-Electrical and Computer Engineering,University of Shanghai for Sience and Technology,Shanghai 200093,China;2.Shanghai Supore Instruments Co.,Ltd,Shanghai 200444,China)

The PCI existed the problems of low transmission speed,high complexity and PCI Core prices,a new design scheme of PCI bidirectional interface based on WISHBONE bus was presented in this paper.The system architecture used open source called PCI-WISHBONE IP core and implemented a PCI interface card based on Xilinx Artix-7 series FPGA chip,which is compatible with 3.3 V and 5 V voltage and is focused on a method of high speed data transmission using DMA.The experimental results confirm that data transmission rate can reach to 65*32 Mbit/s when the PCI bus is run in the master mode,Transfer rate has been improved significantly with data transmission accuracy and stability.It provides a new sort of methods for the high-speed PCI interface design.

PCI interfaces;DMA;high-speed transmission;WISHBONE Bus

TP311.1

A

10.16157/j.issn.0258-7998.2016.08.018

上海市宝山区科委产学研项目(bkw2015130)

(2016-03-30)

梁烨(1992-),女,硕士研究生,主要研究方向:嵌入式系统。

简献忠(1969-),通信作者,男,博士,教授,主要研究方向:嵌入式系统,E-mail:jianxz@usst.edu.cn。

中文引用格式:梁烨,简献忠,肖儿良,等.基于 WISHBONE总线的双向 PCI高速传输接口设计[J].电子技术应用,2016,42 (8):77-79,83.

英文引用格式:Liang Ye,Jian Xianzhong,Xiao Erliang,et al.The bidirectional interface design of PCI high-speed transmission based on WISHBONE bus[J].Application of Electronic Technique,2016,42(8):77-79,83.