一种基于快速激活的硬件木马检测法*

裴 根,石朝阳,邹雪城,刘政林

(华中科技大学 光学与电子信息学院,湖北 武汉 430074)

一种基于快速激活的硬件木马检测法*

裴根,石朝阳,邹雪城,刘政林

(华中科技大学 光学与电子信息学院,湖北 武汉 430074)

硬件木马因其巨大的潜在威胁而受到学术界和工业界越来越广泛的关注,而传统的测试技术很难发现这些硬件木马,因此,针对硬件木马的隐藏机制,提出了一种快速激活并检测木马的方法,通过将木马原型植入微处理器 OR1200中,并利用大量测试用例激励,激活了木马,验证了该方法的正确性。

硬件木马;翻转概率;木马激活;木马检测

0 引言

在过去几十年,集成电路已经渗透到人类社会活动的各个领域,包括在金融、军事、工业、交通等关乎国家命脉的领域也得到了广泛的应用,因此确保集成电路的安全性与可靠性变得尤为重要。

围绕硬件木马检测,研究人员已经做了很多工作,但目前学术界仍缺少相应的用于评估各种木马检测方法有效性的评价准则[1]。现有的硬件木马检测技术主要可分为基于物理分析的检测方法、基于ATPG(自动测试矢量生成)的检测方法,以及基于旁路信号分析的检测方法。基于物理分析的方法是一种破坏性的方法,对芯片进行反向工程,还原出原始设计的电路,这种方法工作量很大,效果也不太好。基于旁路信号的旁路分析技术最初主要应用于密码分析学领域,通过监测采集IC密码芯片在工作时泄露的物理特征信息(如功耗、声波、运行时间、电磁辐射等),利用数学分析(重点是统计分析)方法获取IC密码芯片中的秘密信息。基于旁路分析的密码芯片正是利用原始电路与木马电路之间旁路信号的差异来检测木马,文献[2]首次提出采用电路的功耗信息来检测硬件木马的方法。此外,通过测量芯片电源端的瞬态电流信号,并对这些信号进行电流集成化分析[3]或基于区域的分析[4],可以有效地检测出小规模的硬件木马。文献[5]提出一种基于时延的物理不可克隆功能(Physical Unclonable Function,PUF)的电路结构,该结构能在芯片的测试阶段辅助检测硬件木马。文献[6]提出一种基于全芯片路径延时信息的新颖指纹生成方法。文献[7]提出了一种未用电路识别(UCI)技术,该文章结果显示UCI技术可以检测大多数常规简单的硬件木马。文献[8]提出了一种新的RTL级木马的代码设计风格以规避文献[7]中提到的UCI检测技术。文献[9]提出了一种反硬件木马的电路设计方法,通过密钥产生签名,对签名进行匹配,以检测硬件木马。

文献[2]~[6]的方法都是基于旁路信号分析,要生产出实际的芯片做测试,花销比较大,研究周期也很长。文献[7]提出的 UCI技术实际上是基于冗余电路分析,但是目前也有很多木马在设计过程中就巧妙地融合到正常电路中去了,并不能被当作冗余电路中识别出来,而且文献[8]就针对此UCI技术提出了一种规避的方法。文献[9]中的签名匹配技术在签名不匹配时只能警告电路可能植入了木马,并不能精确指出木马的存在位置。综上所述,本文基于木马的隐藏机制,提出了一种基于快速激活的RTL级硬件木马检测方法,本方法可以检测一些将电路中的低活跃度信号作为触发条件的硬件木马,同时可以定位这些木马,以方便恢复原始电路设计。

1 硬件木马的快速激活方法

1.1木马的激活概率分析

硬件木马具有隐蔽性高、激活概率低的特点,并且通过常规的测试流程很难激活发现这些硬件木马。图1展示了一个简单的三级逻辑门电路概率计算过程。我们以(P0,P1)来表征一个节点值为 0和 1的概率。概率计算过程遵循如下原则:(1)P0+P1=1;(2)不考虑门之间的拓扑学内在联系,每个节点都是独立的;(3)最原始输入端节点概率为(1/2,1/2)。从图1可以看到,到第三级中虚线框中的与门输出端值为1的概率为1/256。事实上,如果电路规模变大,级数增加,一些有更低的概率甚至难以触发的节点是可以预见的。

图1 电路的概率计算过程

1.2快速激活木马的机制

为了综合表征一个节点的概率分布,我们引入一个权重值——节点翻转概率Pt,Pt=P0×P1,平均翻转时间周期Tt=1/Pt。可见,节点翻转概率越小,需要的平均翻转周期越大。为了确保Pt大于一个设定的阈值Pth,根据可测性设计思想,一个虚拟扫描触发器(dummy scan flip-flop,dSFF)可以植入我们的电路中用来使 P0和 P1的值尽量靠近。如图2所示是虚拟触发器的结构图(与门和或门除外)。

图2 虚拟触发器的结构图

当节点 i的 P0<<P1时,一个与门放在 dSFF后面,同时将节点i与dSFF的输出Q连入与门输入端,与门输出作为新的节点i。当节点i的P0>>P1时 ,一个或门放在dSFF后面,同时将节点 i与 dSFF的输出Q连入或门输入端,或门输出作为新的节点i。本文中,dSFF-AND和dSFF-OR分别代表dSFF后面接了一个与门和或门。当TE(Test Enable)信号使能时,dSFF的输出Q由SI(Scan Input)来决定。当TE不使能时,植入电路内的dSFF对原始电路的功能不会有影响。

在测试模式下,dSFF的输出概率分布为(1/2,1/2)。假设节点i的概率分布(P0,P1),P1<<P0,有

可见新节点的概率P0和P1的值互相靠近1/2。那么节点翻转概率变化如下

图3 添加dSFF

2 实验验证

2.1测试方法

为了真实模拟硬件木马的植入及检测过程,我们使用了开源微处理器OR1200作为我们的测试平台。我们从TRUST-HUB上提供的一些 benchmarks中提取了 10个木马原型,如表 1所示,植入到 OR1200的源代码中。我们写了10个不同功能的C语言程序,利用 opencores提供的工具链编译成机器码,作为OR1200的测试用例,以便尽可能覆盖所有处理器功能。

表 1 实验中用到的木马原型[10]

首先我们通过功能测试确保木马在功能验证过程中不会被暴露,同时,用 Perl编写脚本统计信号节点的翻转概率(翻转次数/仿真时钟周期数),将 dSFF插入代码中。dSFF的插入流程如图4所示。Pth为节点翻转概率Pt的可设阈值。

图4 dSFF插入流程

2.2结果分析

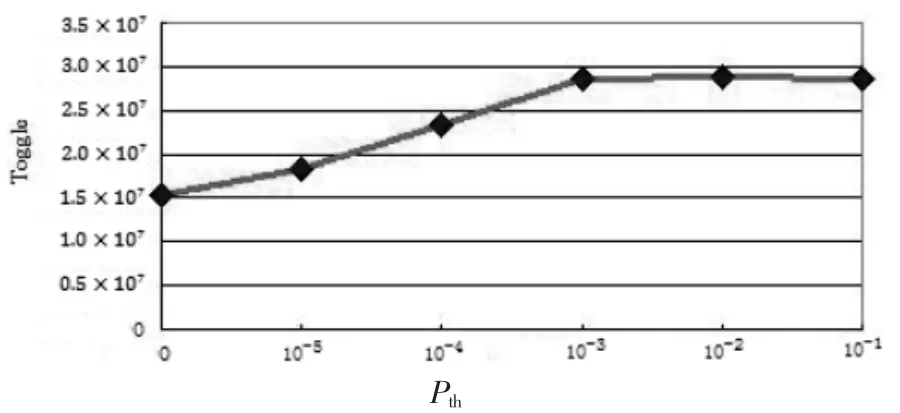

在检测实验过程中,我们设置不同的 Pth值,并利用脚本分析电路内部信号节点的翻转次数统计值 Toggle,如图5所示,随着 Pth的逐渐加大,电路的信号节点激活度逐渐增大。在Pth>10-3后,激活度增长趋势放缓。可见,插入dSFF在一定范围内可以增大电路的激活率,但是并不能无限增强,有一个极限值。

图5 电路激活度曲线

图6是植入木马被激活发现的个数与Pth的关系。在一定值内,由图5可知,电路激活度随着 Pth的增大而增大,木马的发现个数也随着Pth的增大而增大,在 Pth>10-3后,木马的被激活个数趋于稳定,说明木马的发现个数与电路的激活度有着直接的关系。同时我们可以看到,在不同的 Pth值范围里,并不能检测到所有植入的木马,可见,本方法还有一些局限性。

表2显示了试验中硬件开销,数据由 Quartus II软件的 compilation report获得。可以看到,植入的10个硬件木马对于原始设计的硬件开销影响1%都不到,基本上可以忽略不计。插入 dSFF的开销随着 Pth的增大而显著增大。所以,结合图6的数据,在检测木马的时候,硬件开销和 Pth值的选择需要有一个折衷考虑。

图6 木马的发现个数曲线

表2 硬件开销对比

3 结语

为了缩短硬件木马的激活时间,本文提出了一种快速激活以检测木马的方法,在设计的功能验证测试阶段,通过对电路内在节点的翻转概率分析,植入dSFF模块,缩短节点的激活时间。基于OR1200的测试结果表明,对于利用低活跃度信号作为触发条件的硬件木马,本方法可以很容易激活并检测出来,对于用特殊序列作为触发条件的硬件木马,本方法的激活成功率很有限。总的来说,硬件木马千千万万,并非本方法可以全部检测,新的方法需要我们继续努力研究去发现。

[1]JIN Y,KUPP N,MAKRIS Y.Experiences in hardware Trojan design and implementation[C].Hardware-Oriented Security and Trust.San Francisco:IEEE,2009:50-57.

[2]AGRAWAL D,BAKTIR S,KARAKOYUNLU D,et al.Trojan detection using IC fingerprinting[C].Security and Privacy.Berkeley:IEEE,2007:296-310.

[3]WANG X,SALMANI H,TEHRANIPOOR M,et al.Hardware Trojan detection and isolation using current integration and localized current analysis[C].Defect and Fault Tolerance in VLSI Systems,2008.Boston:IEEE,2008:87-95.

[4]RAD R M,WANG X,TEHRANIPOOR M,et al.Power supply signal calibration techniques for improving detection resolution to hardware Trojans[C].Proceedings of the 2008 IEEE/ACM International Conference on Computer-Aided Design.San Jose:IEEE Press,2008:632-639.

[5]LI J,LACH J.At-speed delay characterization for IC authentication and Trojan horse detection[C].Hardware-Oriented Security and Trust.Anaheim:IEEE,2008:8-14.

[6]JIN Y,MAKRIS Y.Hardware Trojan detection using path delay fingerprint[C].Hardware-Oriented Security and Trust. Anaheim:IEEE,2008:51-57.

[7]HICKS M,FINNICUM M,KING S T,et al.Overcoming an untrusted computing base:Detecting and removing malicious hardware automatically[C].Security and Privacy.Brisbane:IEEE,2010:159-172.

[8]STURTON C,HICKS M,WAGNER D,et al.Defeating UCI:Building stealthy and malicious hardware[C].Security and Privacy.Berkeley:IEEE,2011:64-77.

[9]CHAKRABORTY R S,PAUL S,BHUNIA S.On-demand transparency for improving hardware Trojan detectability[C]. Hardware-Oriented Security and Trus.Anaheim:IEEE,2008:48-50.

[10]TRUST_HUB[EB/OL].[2015-8-12].https://www.trusthub.org/

[11]OR1200 OpenRISC Processor.[EB/OL].[2015-8-12].http://opencores.org/or1k/OR1200_OpenRISC_Processor

A hardware Trojan detection method based on rapid activation

Pei Gen,Shi Zhaoyang,Zou Xuecheng,Liu Zhenglin

(School of Optical and Electronic Information,Huazhong University of Science and Technology,Wuhan 430074,China)

Hardware Trojans draw more and more attention of the academia and industry because of its huge potential in recent years.Traditional testing technology is difficult to find these hardware Trojans.To solve this problem,considering the hardware Trojan hidden mechanism,a rapid hardware Trojan activation method is proposed in this paper.According to implant several hardware Trojan prototypes into microprocessor OR1200 and take advantage of a large number of test vectors incentives,then using the rapid hardware Trojan activation method,Trojan horses are activated.Thus,the correctness of the method proposed is verified.

hardware Trojan,turning probability;Trojan activation;Trojan detection

TN918

A

10.16157/j.issn.0258-7998.2016.08.014

国家自然科学基金(61376026)

(2016-03-08)(

2016-02-03)

裴根(1991-),男,硕士研究生,主要研究方向:超大规模集成电路。

石朝阳(1991-),男,硕士研究生,主要研究方向:超大规模集成电路。

邹雪城(1962-),男,教授,博士生导师,主要研究方向:超大规模集成电路。

中文引用格式:裴根,石朝阳,邹雪城,等.一种基于快速激活的硬件木马检测法[J].电子技术应用,2016,42(8):63-66.

英文引用格式:Pei Gen,Shi Zhaoyang,Zou Xuecheng,et al.A hardware Trojan detection method based on rapid activation[J]. Application of Electronic Technique,2016,42(8):63-66.