基于逻辑表决器的组合逻辑电路的设计

江 丽,吴轶群

(湖南高速铁路职业技术学院机电系,湖南 衡阳 421002)

基于逻辑表决器的组合逻辑电路的设计

江 丽,吴轶群

(湖南高速铁路职业技术学院机电系,湖南 衡阳 421002)

用数字信号完成对数字量进行算术运算和逻辑运算的电路称为数字电路,可以分为组合逻辑电路和时序逻辑电路两大类。其中,组合逻辑电路是由最基本的逻辑门电路组合而成。文章以三人表决器为例介绍了三种设计方案,以便学生熟悉常见组合逻辑电路的特点及应用。

组合逻辑电路;逻辑表决器;设计

组合逻辑电路可以有若干个输入变量和若干个输出变量,其每个输出变量是其输入的逻辑函数,其每个时刻的输出变量的状态仅与当时的输入变量的状态有关,与本输出的原来状态及输入的原状态无关。电路没有记忆功能,输出状态随着输入状态的变化而变化,类似于电阻性电路,如加法器、译码器、编码器、数据选择器等都属于此类。

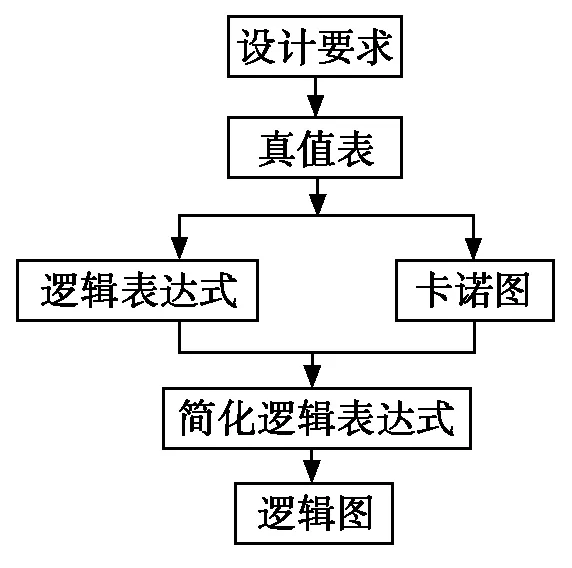

使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。设计组合电路的一般步骤如图1所示。根据设计任务的要求建立输入、输出变量,并列出真值表。然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。根据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路[1]。最后,用实验来验证设计的正确性。同样的逻辑电路设计可以用不同的设计方案来完成,本文以三人逻辑表决器为例来说明,TTL集成电路、中规模集成译码器和中规模集成数据选择器的逻辑功能和设计原理及其应用。

1 三人逻辑表决器的设计

设计要求与逻辑描述:用“与非”门设计一个表决电路。当3个输入端中有2个或3个为“1”时,输出端才为“1”。

1.1 采用基本逻辑门电路进行设计

组合逻辑电路的基本设计步骤如下:

1) 定义输入输出变量:定义设有A、B、C三位裁判,三人表决中至少要有两人同意,才可以通过。同意为1,不同意为0,输出为Y,达成以上条件Y输出为1,反之为0。

2) 根据逻辑功能列出真值表:

表1 三人逻辑表决器的真值表

图1 组合逻辑电路设计流程图

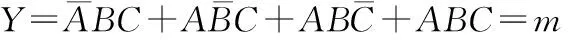

3) 由真值表写出输出逻辑函数表达式:

4) 化简逻辑表达式:

.

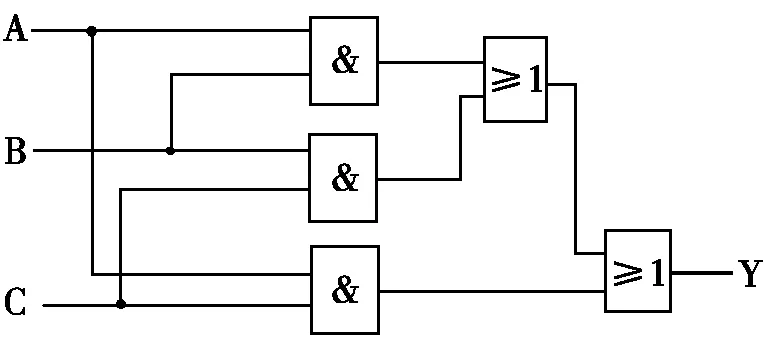

5) 画出逻辑电路图(如图2)

图2 逻辑电路图

1.2 用74LS138译码器进行设计

根据输入地址的不同组合译出唯一地址,故可用作地址译码器。接成多路分配器,可将一个信号源的数据信息传输到不同的地点[2]。

图3 数据多路分配器引脚图与功能示意图

二进制译码器还能方便地实现逻辑函数,由于n个输入变量的二进制译码器的输出提供了2n个最小项,而任何一个逻辑函数可以变换为最小项之和的标准与-或表达式。因此可利用译码器和门电路来实现组合逻辑电路。

.

根据上式,只需在一片74LS138的输出端加一个与非门就可以实现该逻辑函数。

图4 三人逻辑表决器逻辑功能实现框图

1.3 用74LS151数据选择器进行设计

数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。

数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别[3]。

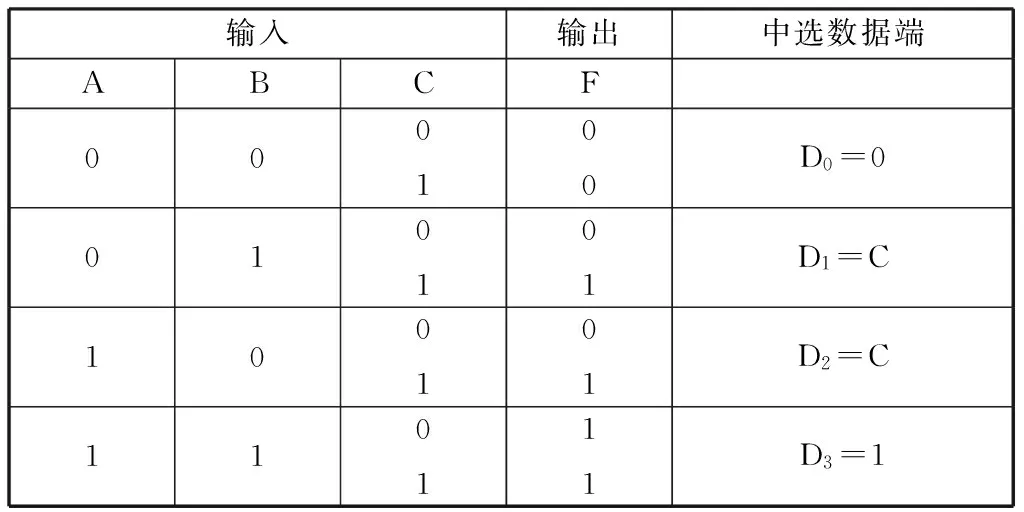

表2 八选一151数据选择器真值表

表3 四选一153数据选择器真值表

如:A2A1A0=000,则选择D0数据到输出端,即Q=D0。

如:A2A1A0=001,则选择D1数据到输出端,即Q=D1,其余类推。

Y=AB+AC+BC.

将逻辑函数转换成最小项表达式:

将不存在的最小项乘以0,存在的最小项乘以1,得到:

=m1·0+m2·0+m3·1+m4·0+m5·1+m6·1+m7·1.

即:

D0=D1=D2=D4=0

D3=D5=D6=D7=1

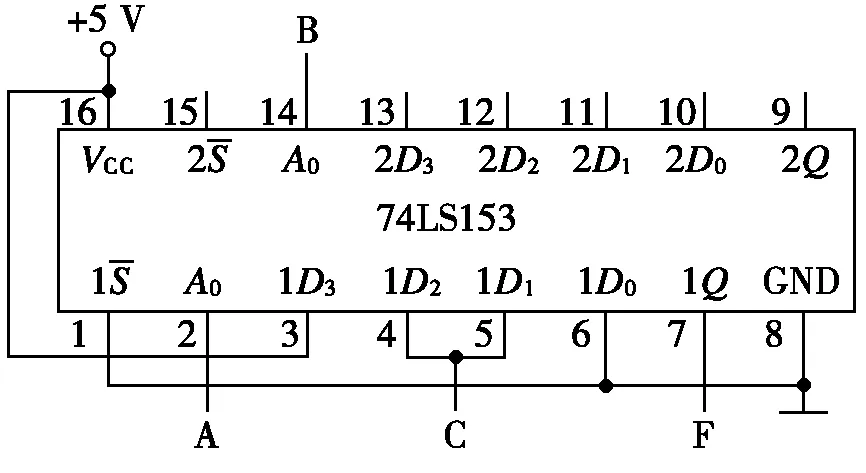

由此可以画出逻辑电路图(如图5)

图5 用8选1数据选择器

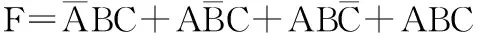

函数F有三个输入变量A、B、C,而数据选择器有两个地址端A1、A0少于函数输入变量个数,在设计时可任选A接A1,B接A0。将函数功能表改画成表3的形式,可见当将输入变量A、B、C中A、B接选择器的地址端A1、A0,由表3可以得到:

D0=0,D1=D2=C,D3=1

图6 用4选1数据选择器

[1] 阎石.数字电子技术基础[M].第4版.北京:高等教育出版社,1998.

[2] 李世雄,丁康源.数字集成电子技术教程[M].北京:高等教育出版社,1993.

[3] 李亚伯.数字电路与系统[M].北京:电子工业出版社,1998.

The Design of Combinational Logic Circuits Based on the Logic Voter System

Jiang Li,Wu Yiqun

(HunanTechnicalCollegeofRailwayHigh-speed,HengyangHunan421001,China)

Digital circuits which handling the calculation of values using arithmetic and logical operations can be classified into two classes: combination logic circuit and order part logic circuit.Among them,the combination logic circuit is composed of the most basic logic circuits.Taking the logic voter system as example,this article introduces three different designs,so that the students can be familiar with the characteristics and application of the combination logic circuit,

combination logic circuit; logic voter system; digital

2016-05-20

2016-08-07

江 丽(1982-),女,湖南邵阳人,讲师,研究生,主要研究方向:电路与系统设计。

1674-4578(2016)05-0036-03

TP331.1

A