基于Quartus II的计时电路设计

熊瑜

摘 要 Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。文章以一个计时电路为例,利用VHDL硬件编程语言和原理图结合,实现计时、校准、整点提示等功能,最后连接数字电路实验箱进行验证。

关键词 Quartus II 计时 校准 分频

中图分类号:TP274 文献标识码:A

0 引言

本文利用Quartus II 9.0实现由四个数码管显示的计时电路,以低两位按照 20 进制设计,高两位为任意进制设计为例,并按 1Hz 频率校准高两位的显示,按 10Hz频率校准低两位的显示,在计数到达某整点值时(例如 0300 的时刻),4盏 LED 灯一起按照 10Hz 闪烁 5 秒钟。

1电路设计

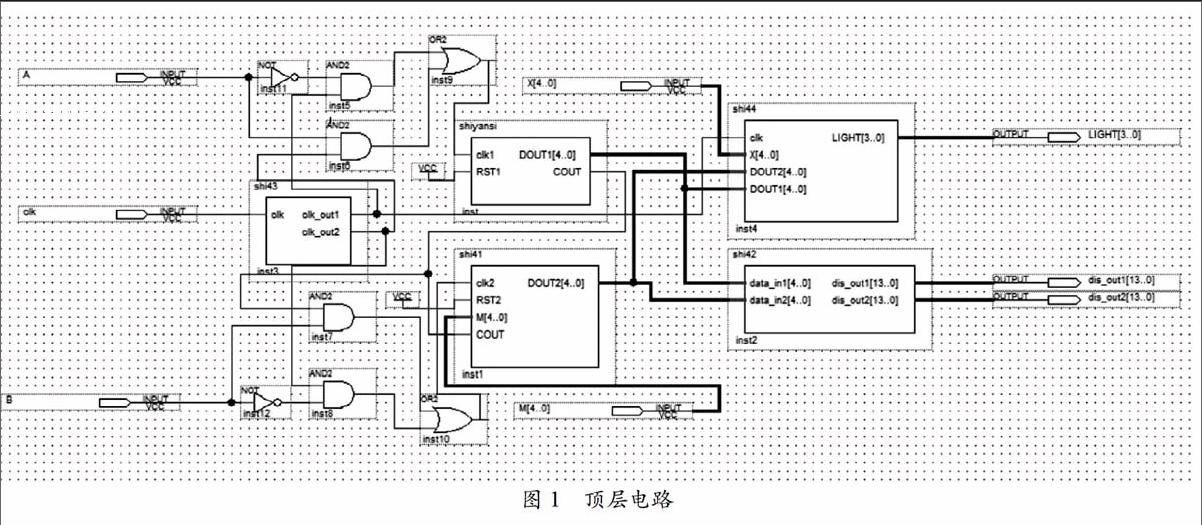

整体电路的程序包含4大部分:计数器(高低位两段)、七段译码器、分频器、整点闪烁。各电路模块拟通过硬件语言实现,生成原理图,再根据逻辑关系进行顶层电路的连接,至此其基本电路的设计情况完成。现将各模块实现方法呈现如下。

1.1计数器的设计

1.1.1低两位计数器的设计

低两位固定为二十进制,可用五位二进制编码其计数状态,程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY shiyansi IS

PORT ( clk1,RST1 : IN STD_LOGIC;

DOUT1 : OUT STD_LOGIC_VECTOR (4 DOWNTO 0);

COUT : OUT STD_LOGIC);

END shiyansi;

ARCHITECTURE fwm OF shiyansi IS

SIGNAL Q1 : STD_LOGIC_VECTOR (4 DOWNTO 0);

BEGIN

PROCESS(clk1,RST1)

BEGIN

IF RST1 = 0 THEN Q1<=(OTHERS => 0); COUT <= 0;

ELSIF clk1EVENT AND clk1=1 THEN

Q1<=Q1+1;

COUT<= 0;

IF Q1 >= "10100" THEN Q1<=(OTHERS => 0); COUT<= 1;

END IF;

END IF;

END PROCESS;

DOUT1<=Q1 ;

END fwm;

clk1为低位时钟输入,COUT为进位信号输出,DOUT1为五位计数信号输出。

1.1.2高两位计数器的设计

高两位要求为任意进制,用五位开关模拟五位二进制来编码32进制以内的可调进制,程序如下:

LIRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY shi41 IS

PORT ( clk2,RST2 : IN STD_LOGIC;

M : IN STD_LOGIC_VECTOR (4 DOWNTO 0);

COUT : IN STD_LOGIC;

DOUT2 : OUT STD_LOGIC_VECTOR (4 DOWNTO 0) );

END shi41;

ARCHITECTURE fwm OF shi41 IS

SIGNAL Q2 : STD_LOGIC_VECTOR (4 DOWNTO 0);

SIGNAL m1 : STD_LOGIC_VECTOR (4 DOWNTO 0);

BEGIN

PROCESS(clk2,RST2)

BEGIN

m1<=M-1;

IF RST2 = 0 THEN Q2<=(OTHERS => 0);

ELSIF clk2EVENT AND clk2=1 THEN

Q2<=Q2+1;

IF Q2 >= m1 THEN Q2<=(OTHERS => 0);

END IF;

END IF;

END PROCESS;

DOUT2<=Q2 ;

END fwm;

clk2为高位时钟输入,COUT为进位信号输出,DOUT2为五位计数信号输出。M为进制控制开关输入信号。

1.2七段译码器的设计

实现高低两位的译码,程序简单但较为冗杂,在此不列出。

data_in1、data_in2分别为低位和高位计数输入,dis_out1、dis_out2分别为14段低位和高位译码信号输出。

1.3分频器的设计

实验箱内晶振时钟频率为100MHz,进行分频分别得到10Hz 和1Hz的频率,较简单在此不再列出。

clk_out1为10Hz输出,clk_out2为1Hz输出。

1.4整点闪烁的设计

整点时刻低两位全部为零,高两位为任意指定的数。在这种情况下,LED灯要闪烁5S。因为低两位计数1S跳一次,所以可以用低两位的前5S实现定时。闪烁用10Hz的时钟频率来实现。其程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY shi44 IS

PORT ( clk : IN STD_LOGIC;

X : IN STD_LOGIC_VECTOR (4 DOWNTO 0);

DOUT2 : IN STD_LOGIC_VECTOR (4 DOWNTO 0);

DOUT1 : IN STD_LOGIC_VECTOR (4 DOWNTO 0);

LIGHT : OUT STD_LOGIC_VECTOR (3 DOWNTO 0) );

END shi44;

ARCHITECTURE fwm OF shi44 IS

SIGNAL A: STD_LOGIC_VECTOR (4 DOWNTO 0);

SIGNAL B: STD_LOGIC_VECTOR (4 DOWNTO 0);

SIGNAL C: STD_LOGIC_VECTOR (4 DOWNTO 0);

BEGIN

PROCESS(clk)

BEGIN

A<=X;

B<=DOUT2;

C<=DOUT1;

IF ((A=B AND (C="00000" OR C="00001" OR C="00010" OR C="00011" OR C="00100"))) THEN

LIGHT<=(OTHERS => clk);

ELSE

LIGHT<="0000";

END IF;

END PROCESS;

END fwm;

clk连接10Hz时钟信号,DOUT1、DOUT2分别为低位和高位计数输入,X为5位整点设置输入。

1.5顶层电路的连接

按照各部分的逻辑关系将以上原理图连接起来并引出输入与输出,如图1所示。其中,A为低位控制校准信号,B为高位控制校准信号。

2验证

将电脑与数字电路实验箱相连接,按照实验箱锁定各个引脚,实现输入控制与输出显示,并将其下载到开发板上。验证所设计的电路,符合要求。

参考文献

[1] 维普网.Quartus Ⅱ[J].今日电子,2008.

[2] 卢毅.VHDL与数字电路设计[M].科学出版社,2001.

[3] 李聪锟.数字电子技术基础[M].高等教育出版社,2014.

[4] 郑亚民,许敏.基于QuartusⅡ的带计时器功能的秒表系统设计[J].电子工程师,2005, 31(1):59-61.