基于IEEE-1588的高精度时钟同步系统设计*

谭 超,苏 超,胡诗俊,吴 燕,何旭东

(1.三峡大学电气与新能源学院,湖北宜昌443002;2.国网黄冈供电公司,湖北黄冈438000)

基于IEEE-1588的高精度时钟同步系统设计*

谭超1*,苏超1,胡诗俊1,吴燕2,何旭东2

(1.三峡大学电气与新能源学院,湖北宜昌443002;2.国网黄冈供电公司,湖北黄冈438000)

为提高高速铁路地震预警系统采集设备时间同步精度,设计了基于IEEE-1588的网络高精度时钟同步系统。系统利用STM32+FPGA构架搭建硬件平台,在FPGA中利用PLL延迟测量法实现高精度时间间隔测量,时间间隔测量精度达到600 ps;利用PHY芯片DP83640获取网络PPS时钟,在STM32中结合卡尔曼滤波与PID算法,实现网络PPS时钟对本地时钟的校正,以及对本地PPS相位校正,最终完成同步系统的软件设计。测试结果表明:本设计时钟同步误差优于3 ns,且具备长期稳定性。

时钟同步;IEEE-1588;PLL延迟测量法;分布式数据采集

高速铁路地震预警系统在铁路沿线及地震带附近设置大量地震数据采集装置,通过实时采集数据,在地震发生初期对铁路将受到的破坏进行快速估计和反应,在铁路受到地震破坏前减速或停车以降低损失[1]。所以,系统内各地震数据采集设备及中央处理单元间的时钟同步精度是预警成功与否的关键。目前系统的时钟同步方案为各设备单独配备GPS模块作为时钟参考源。由于GPS受他国控制、天气影响、成本高等原因[2],需要寻求其他解决方案替代或补充现有方案。IEEE-1588全称为网络测量与控制系统精密时钟同步协议标准,是一种主从同步系统,依靠系统内设备间以太网,系统内设备时钟与主时钟进行同步[3]。对于高速铁路地震预警系统中分布式数据采集系统,因为采集设备放置位置以及数据通过以太网传输等原因,与GPS相比,IEEE-1588的安全性、可靠性及经济型都更高[3]。基于IEEE-1588协议的时钟同步已在各领域中实际应用,文献[4]在数字化变电站中构建的OTN+PTN混合组网内精度达到±100 ns,文献[5]在水下采集领域实现精度优于1 μs,文献[6]在智能电网中利用软件实现,精度仅 31 μs。文献[7-8]设计了基于DP83640的IEEE-1588硬件实现,设计的时钟同步系统精度可达到10 ns级别。基于此,为了提高高速铁路地震预警数据采集系统同步的可靠性,以及降低IEEE-1588授时过程中,网络延迟引起的PPS信号相位抖动误差,提高同步精度,本文设计了一套基于IEEE-1588协议的高精度时钟同步系统。

1 系统方案及硬件平台设计

1.1时钟同步系统整体方案

地震预警系统时钟同步方案中,中央处理单元包含一个高精度主时钟,通过GPS或北斗授时等方式与标准时钟同步。系统中主时钟与所有从设备通过以太网相连,传输数据的同时利用IEEE-1588协议完成对从设备的授时,从设备结合网络授时时钟与本地时钟完成时钟同步功能,从而实现预警系统中所有设备时钟同步。

本文针对系统中从设备的时钟同步设计了硬件电路,在其基础上设计软件实现了高精度时钟同步系统。

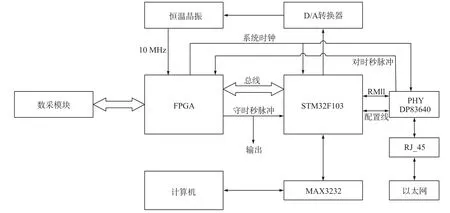

1.2从设备时钟同步系统方案

从设备时钟同步系统方案如图1所示,系统主要由STM32单片机、FPGA、恒温晶振MV180及PHY芯片DP83640组成。

图1 从设备时钟同步系统结构示意图

DP83640是NS公司推出的首款在PHY层支持IEEE-1588的PHY芯片,从设备利用DP83640提供的硬件时间戳方法完成IEEE-1588对时可以极大地降低开发难度以及提高对时精度[3]。STM32单片机通过PHY芯片DP83640与以太网进行连接,并控制DP83640与主时钟进行对时,将产生的网络PPS时钟传输至FPGA。FPGA对恒温晶振MV180输出的10 MHz时钟信号进行倍频后通过计数器方式产生设备本地PPS时钟。测量恒温晶振频率及网络PPS时钟与本地PPS时钟的相位差由FPGA完成,STM32利用FSMC从FPGA中读入频率和相位差测量数据,并在STM32单片机中完成频率修正算法和相位修正算法,分别得到频率修正值和相位修正值;利用频率修正值控制D/A转换器产生电压信号,以控制MV180的频率输出;STM32通过FSMC将相位修正值传至FPGA执行相位修正。

短时内,恒温晶振频率稳定性比网络PPS时钟高,而长期运行中,由于环境变化及老化误差等因素,恒温晶振输出频率将产生误差,从而导致本地PPS时钟精度下降,需要通过网络PPS时钟进行修正。恒温晶振频率误差会导致本地PPS时钟与网络PPS时钟相位差发生变化,不进行修正则误差将累加。因此,结合恒温晶振输出时钟与网络PPS时钟的优缺点,实现对从设备恒温晶振频率修正算法和本地PPS时钟相位修正算法是软件设计的重点。

2 恒温晶振频率修正方法研究

为完成恒温晶振频率修正,需要测量恒温晶振频率特性,研究高精度频率测量方法及修正方法。

2.1恒温晶振频率特性

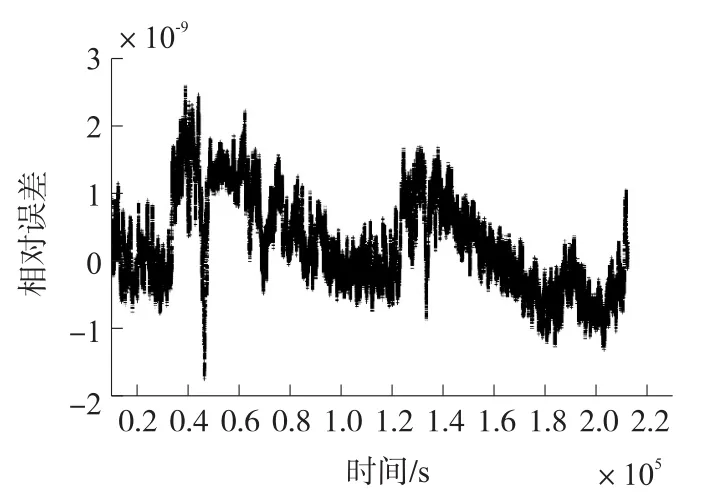

由于恒温晶振受温度和老化误差等影响,未对晶振进行控制的情况下,输出频率会随环境变化,长期变演为朝一个方向逐渐偏离基准频率[9]。图2是在室内环境进行60 h的实验结果。

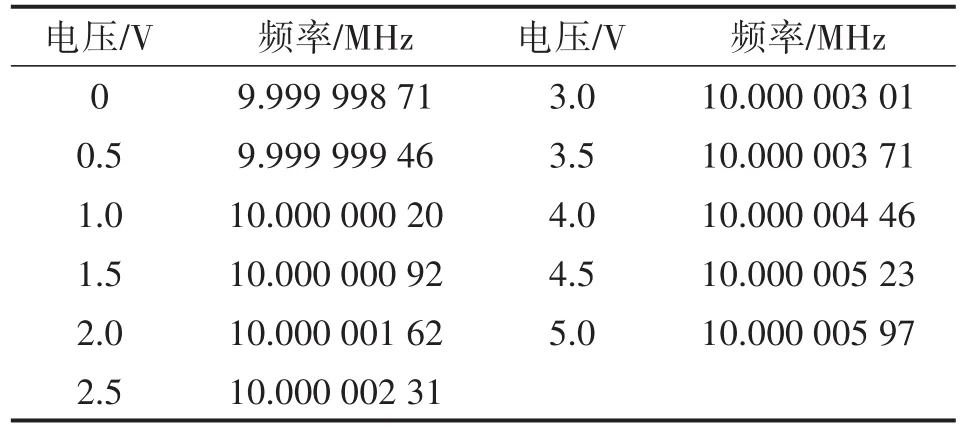

由图2可见,晶振误差在10-9级,随环境温度变化较大,且长期呈现出增加趋势,因此必须对晶振输出频率进行修正。为对恒温晶振频率进行控制,首先需要测量MV180的F-V特性曲线,实验数据见表1。

图2 未修正时恒温晶振输出频率相对误差

表1MV180F-V修正实验数据表

MV180的F-V特性可拟合为线性关系,根据PID算法,仅取比例环节,则实测关系表达式为:

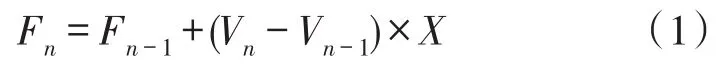

式中,Fn为修正后MV180输出频率,Fn-1为修正前输出频率,单位为MHz;Vn为单片机通过控制D/A输出的压控电压值,Vn-1为修正前D/A输出压控电压值,单位为V;X为实测数据经拟合得到的F-V系数,根据表1数据计算得1.43×10-6。

所以频率修正公式为:

式中,DAn为修正后D/A控制值,DAn-1为修正前D/A控制值,10为晶振输出频率目标值10 MHz,12为D/A位数,5为D/A输出电压范围。

2.2恒温晶振频率测量方法

由于网络PPS时钟周期为1 s,FPGA利用晶振时钟对网络PPS时钟周期进行测量,即可得到晶振频率。测量误差包括晶振频率误差和网络PPS时钟误差,在频率修正时对测量值进行处理即可得到较为准确的晶振频率误差。

为提高测量精度,设计采用粗测量与细测量结合方式。

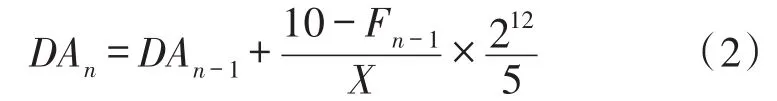

如图3所示,Clock_250 M为FPGA利用PLL将恒温晶振输出的10 MHz时钟倍频产生的250 MHz内插时钟,PPS_NET为接收到的网络PPS时钟信号。T0为以内插计数法直接测量得到结果,为计数器数值与内插时钟的周期4 ns的乘积。内插测量法分辨率为4 ns,误差最大可达8 ns,对守时时钟精度造成较大影响,所以需要增加时间细测量模块,对时间t1及t2进行测量。本方法测出的网络PPS时钟周期T=T0+t1-t2。

图3 网络PPS时钟周期测量方法示意图

图4PLL延迟测量法示意图

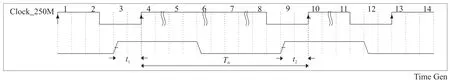

细测量采用PLL延迟测量法进行测量。如图4所示,FPGA利用PLL对晶振时钟进行倍频后输出4个250 MHz的内插时钟,依次延迟500 ps。当触发事件上升沿到来时记录4个内插时钟的状态值,s0~s7的8种状态分别对应触发事件落在延迟线内的区域的中间值,即{1000,1100,1110,1111,0111,0011,0001,0000}分别对应{3.75,3.25,2.75,2.25,1.75,1.25,0.75,0.25}单位为ns。如此,细测量的分辨率为0.5 ns,单次测量误差小于0.25 ns。由于内插时钟以测量时钟为基准延迟,所以触发事件在前,最后测得T=T0+t1-t2。总的时间测量分辨率为0.5 ns,总误差小于0.5 ns。

2.3恒温晶振频率修正方法

MV180的短期稳定性很高,长期会漂移;网络PPS时钟长期稳定性很高,误差表现为高斯分布[1,3]。为更精确地计算晶振频率误差,本文设计卡尔曼滤波器。卡尔曼滤波在对将来测量的误差进行估计时会将过去测量的估计误差与新测量的误差进行合并[10],设计如下:

式中,状态向量X为频率误差,Uk为现在状态控制量,A、B为一步转移系数,由于认为标准时间秒是恒定的,取 1;Pk|k-1是 Xk|k-1对应的协方差,Pk-1是Xk-1对应的协方差,Q是系统过程方差,MV180短时频率精度方差为2×10-12,此值取为0.002;Zk为FPGA实际测得的频率误差值,Kk为卡尔曼增益,H为观测系数,取1;R为测量值方差,误差来源包括授时时钟误差、测量误差及其他误差,根据测试结果分析取5。

计算得到频率误差值后,STM32单片机利用式(2)计算得到D/A控制值,用于改变D/A转换器输入值,以完成恒温晶振频率修正功能。

3 本地PPS时钟相位修正方法研究

本地PPS时钟由FPGA对内插时钟组进行计数产生,会因为恒温晶振频率误差产生相位误差。本文利用粗测量加细测量的方法测量网络PPS时钟与本地PPS时钟间相位差值,在STM32单片机中经由相位差修正算法处理后得到相位差修正值,由FPGA完成调相修正。

3.1本地PPS时钟产生及相位修正

本地PPS时钟由FPGA对250 MHz内插时钟组计数产生。在本地PPS产生模块中另外设计4路内插时钟,与图4中所示4路内插时钟后依次延迟500 ps,形成4 ns周期的8路内插时钟组。8路内插时钟分别接入FPGA设置的程控8路选择器,输出接秒计数器时钟输入端,并在计数器内部留有外部调整数据输入端口,用于步进为4 ns的误差调节。STM32单片机计算出修正参数后通过FSMC传至FPGA,控制本地PPS时钟相位改变,调整分辨率为0.5 ns。

3.2相位差测量方法

本地PPS时钟与网络PPS时钟相位差测量方法与晶振频率测量方法相同,由FPGA采用粗测量与细测量结合进行测量。测量分辨率为0.5 ns,误差小于0.5 ns。

3.3本地PPS时钟相位修正方法

经修正后的恒温晶振输出频率在短期和长期都具有较高的可靠性,相位差测量值误差主要来源于晶振频率误差和网络PPS时钟误差。与频率修正误差相同,设计同式(3)的卡尔曼滤波器,根据实验结果R取0.8,其他参数保持一致。

FPGA读取计算所得相位差修正值后对本地PPS时钟模块进行调整,完成本地PPS时钟相位修正功能。

4 验证与测试

本文将从设备守时模块与主时钟通过IEEE-1588协议进行时钟同步,验证从设备恒温晶振输出频率稳定性及从设备时钟与网络PPS时钟间相位差关系。

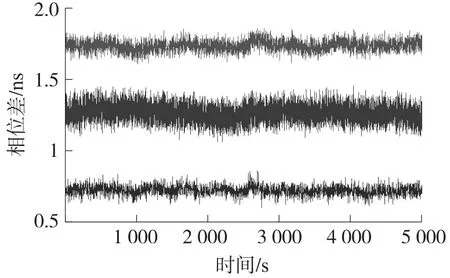

(1)PLL相位延迟精度验证。将4路PLL内插时钟经分频后分别输出值相邻管脚,检测同相位时两个管脚输出时钟相位差,再分别检测延迟内插时钟与基准内插时钟相位差。得到结果如图5所示,单位为ns,方差均小于0.1。根据测试所得相位差调整细测量模块中各区域对应的时间值,即可提高细测量精度。

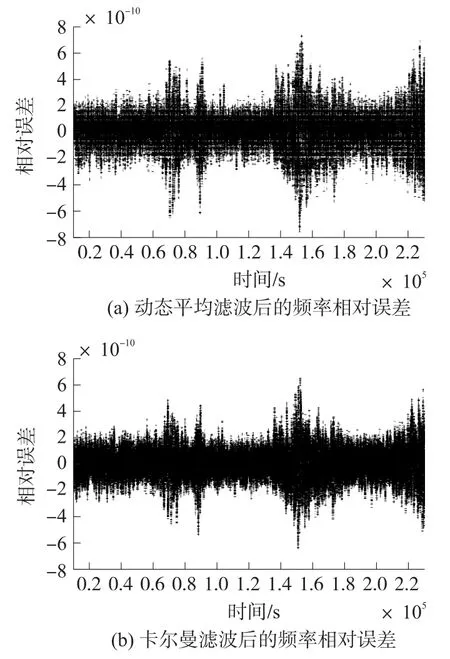

图5PLL相位延迟精度

(2)恒温晶振输出频率精度验证。在室内环境进行60 h实验,经过以100点为周期的动态平均法滤波后晶振频率误差如图6(a)所示,以卡尔曼滤波所得如图6(b)所示。可见,晶振频率相对保持恒定,误差集中在±4×10-10内,并且长期稳定,满足设计要求。

图6

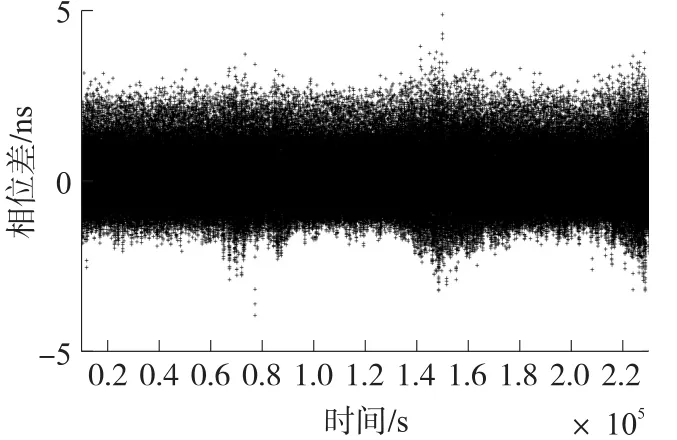

(3)本地PPS时钟相位精度验证。对本地PPS时钟与网络PPS时钟之间相位差进行测量,测量结果如图7所示,相位差测量值集中在±2.5 ns内,服从(0,0.8)的正态分布。相位精度误差优于3 ns,并具有长期稳定性。

图7 相位差误差测量值

5 结束语

为满足高速铁路地震预警系统中分布式数据采集的高精度时间同步需求,本文设计了基于IEEE-1588的网络PPS时钟同步系统,给出了实际的系统构成方案及高精度时钟同步方法。实验表明,通过此方法从设备时间同步精度优于3 ns,在分布式数据采集及无GPS信号等场合有一定的参考价值。

[1]王国新,孙奉劼,王东明.高速铁路地震预警时间与预警区域和震级的关系[J].中国铁道科学,2014(2):120-124.

[2]韩琳,范旭娟,潘登.几种IEEE 1588对时实现方法的分析与比较[J].测控技术,2013(2):74-76.

[3]文永康,文菠,齐永龙.分布式数据采集系统时间同步研究[J].计算机测量与控制,2014(4):1273-1275.

[4]吴维农,唐夲,卓灵.IEEE1588v2时间同步技术在新一代电力骨干网中应用研究[J].计算机测量与控制,2014(8):2533-2535,2545.

[5]Joaquín Del Río,Daniel Mihai Toma,Shahram Shariat-Panahi,et al. Smart IEEE-1588 GPS Clock Emulator for Cabled Ocean Sensors[J].IEEEJournalofOceanicEngineering,2014,39(2):269-275.

[6]Pallares-Lopez V,Moreno-Munoz A,Rosa JJGDL,et al.Synchrophasor for Smart Grid with IEEE 1588-2008 Synchronism[J]. Przeglad Elektrotechniczny,2012,88(1A):31-36.

[7]刘兆庆,潘邵武,张毅刚.基于DP83640的IEEE 1588应用研究[J].测控技术,2012(9):80-83.

[8]王康,胡永辉,何在民.基于DP83640硬件辅助的IEEE1588研究及实现[J].时间频率学报,2011(1):1-8.

[9]薛冲.基于晶体振荡器的老化建模及其智能补偿[D].西安:西安电子科技大学,2014.

[10]郭应时,王畅,张亚岐.噪声方差对卡尔曼滤波结果影响分析[J].计算机工程与设计,2014(2):641-645.

谭超(1982-),男,土家族,湖北利川人,三峡大学电气与新能源学院,讲师/博士,研究方向为电磁场传感器与测量、微弱信号检测以及智能仪表设计,ctgutc@ctgu.edu.cn。

Design of High Precision Time Synchronization System Based on IEEE-1588*

TAN Chao1*,SU Chao1,HU Shijun1,WU Yan2,HE Xudong2

(1.College of Electrical Engineering and New Energy,China Three Gorges University,Yichang Hubei 443002,China;2.State Grid Huanggang Power Supply Company,Huanggang Hubei 438000,China)

In order to improve the precision of data acquisition equipment of the earthquake early warning system for high speed railway,a high precision time synchronization system based on IEEE-1588 is designed.The system uses STM32+FPGA structure to set up a hardware,and it achieves high precision time interval measurement based on PLL delay measurement in FPGA,of which measurement accuracy is 600 ps.The system obtains network time by PHY chip DP83640,and combines Kalman filtering and PID algorithm in STM32 to correct local time and PPS phase by network time to complete software design of the synchronization system.The test result shows that error of time synchronization is less than 3 ns and stability maintains for a long-term.

time synchronization;IEEE-1588;PLL delay measurement;distributed data acquisition

TH714

A

1005-9490(2016)05-1103-05

项目来源:三峡大学2015年硕士学位论文培优基金项目(2015PY039)

2015-10-09修改日期:2016-01-08

EEACC:1230G10.3969/j.issn.1005-9490.2016.05.017