视频时序信号发生器的实现方法

苗绘玲

(杭州士兰微电子股份有限公司,浙江 杭州 310012)

视频时序信号发生器的实现方法

苗绘玲

(杭州士兰微电子股份有限公司,浙江 杭州 310012)

阐述了一种新型视频时序信号发生器的实现方法,并提供了详细的设计结构图。通过软件配置不同的时序描述指令,该发生器中的指令解码器和指令跳转器将时序描述指令解码,产生相应的连续时序信号,包括小尺寸和超大尺寸显示设备的时序信号,以及不规则分辨率的时序信号。视频时序信号发生器可以输出多标准的视频格式,满足各种视频显示格式的要求。

时序信号发生器;数字时序信号;视频格式

1 视频时序信号

电视技术中,传递图像的基本方法是:根据人的视觉特性,利用电子扫描方式将平面图像分解成像素,采用电信号来传送静止或活动图像。像素的传送具有以下两个特点[1]:第一,要求传送速度快,只有传送时间小于视觉暂留时间,图像才会给人以连续无跳动的感觉;第二,传送要准确,每个像素一定要在需要传送时才被转换、传送,并被接收方接收。且收、发双方每个像素被转换、还原的几何位置要一一对应,即收发双方应同步[2]。

目前市面上一些可以产生数字时序信号的集成电路,只是针对某些显示设备的应用而设计的,只能输出固定的几组视频时序信号,支持的视频标准单一,缺乏灵活性,往往只能满足特定视频系统,无法满足多种形式视频时序信号输入的需求。例如,某家公司的一款芯片输出分辨率最小为480i,最大为1 080p。根据其所支持的分辨率,该款芯片可以应用于TV显示,但是不能应用于小尺寸7 in(1 in=2.54 cm)、8 in或超大尺寸显示设备,例如车载电视、广告墙等,主要就是因该款芯片在支持基本的TV分辨率的同时,无法输出小尺寸和超大尺寸显示设备所需要的时序信号。按照传统的设计方法,要想输出多种时序信号,势必增加设计的选择条件,这样会增加硬件成本,控制灵活度也会大大降低。

本设计在不增加硬件成本的基础上,可以解决现有技术所支持的多标准视频格式有限方面的不足,提供一种视频时序信号发生器,该视频时序信号发生器可根据需要产生任意分辨率的时序信号,适用不同的视频格式,例如:采用本设计的同款芯片应用于TV显示的同时,也可根据客户需求产生应用于某款玩具的320×240时序,应用于车载电视的800×480时序。采用该设计的芯片应用范围比较广,不必局限于常用的一些分辨率,可满足各种视频显示格式的要求,只需根据用户需求改变软件配置,即可产生用户需要的任意时序信号。

2 视频时序信号发生器的工作原理

视频时序信号发生器由软硬件结合实现。软件将需要的视频时序信号用指令描述出来,例如:一帧内有多少行,每行的高低电平跳变位置,电平持续时间等信息;硬件通过CPU接收这些描述指令并加以存储,再通过指令解码器将这些描述指令解码,最后输出需要的视频时序信号。这样的设计只需要控制软件提供给硬件的描述指令,即可灵活地输出用户所需求的任意分辨率的时序信号。

视频时序信号发生器产生信号的步骤如下:

1)根据需要自定义指令码。

2)确定需要的视频格式,例如[3]:525p,525i,625p,625i,720p,1 080i,1 080p,VGA,SVGA,XGA,SXGA等格式中的一种,也可以是分辨率比较特殊的某一种视频格式。时序信号分为数字时序信号和数字复合时序信号两种,用自定义的指令码对所需要视频格式的时序信号进行描述,只需要描述一帧图像的时序信号。

3)用编译器将描述指令转为机器码。描述指令有数字和数字复合两种,分别产生数字时序机器码和数字复合时序机器码文件。

4)通过CPU将数字时序的机器码和数字复合时序的机器码分别送给硬件,硬件将两份机器码分别保存到两个存储器中。

5)视频时序发生器分别从存储器中读取机器码,产生数字同步和数字复合同步时序信号。

硬件从系统复位开始一直处于休眠状态,直到时序发生器被唤醒才开始工作。此时视频时序发生器从休眠状态跳到IDLE状态,然后开始运行机器码。通过指令解码器对指令进行解码,解码后的指令用来控制指令跳转器,产生下一个要读取的指令地址,也即存储器的读地址,并同时产生相应的时序信号。存储器中的指令运行完一遍后,产生的时序信号刚好为一帧图像。然后根据指令再跳转到指令的开始,重复执行上述机器码,产生下一帧图像的时序信号,依次类推,相应的视频时序信号就产生了。

3 视频时序信号发生器的实现方法

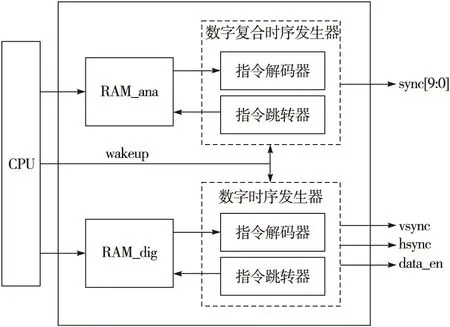

视频时序发生器,包括数字时序发生器、数字复合时序发生器和两个存储器(RAM_ana和RAM_dig),两个发生器均由指令解码器和指令跳转器组成,如图1所示。

图1 时序发生器的原理图

硬件通过CPU将需要解码的视频描述指令存储到相应的存储中,接收到wakeup信号后,时序发生器通过指令解码器和指令跳转器将视频描述指令解码,最后输出需要的视频时序信号。下面所示实施例中以525i模式的数字复合时序发生器为例,其他模式的时序发生器原理与此相同,其过程如下:

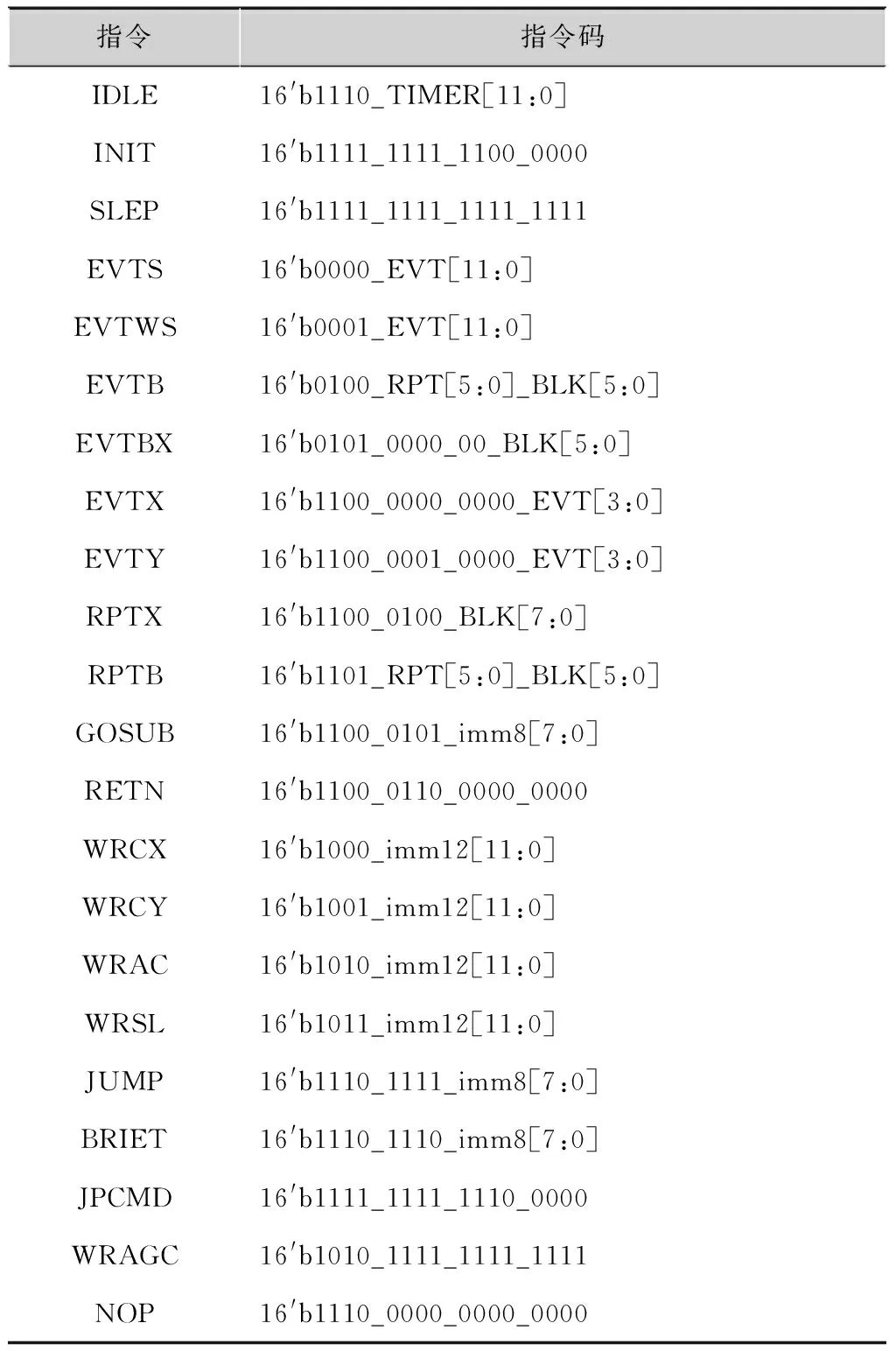

1)根据需要自定义视频时序信号发生器中用到的指令,如表1所示。

除了常见的IDLE,INIT,SLEP,RETN,JUMP,NOP等指令外,根据需要自定义新的指令,每个指令都定义了其对应的指令码。以IDLE为例,表1中IDLE对应的指令码为16′b1110_TIMER[11:0],如果硬件接收到一条指令16′b1110_0001_0010_0111,则表示硬件需保持空闲状态(IDLE)的循环次数为12′b0001_0010_0111(TIMER[11:0])。

2)确定需要的视频格式,例如525i格式。然后用自定义的指令码对所需要的视频格式进行描述,只需要描述一帧图像的时序信号。

数字复合时序信号的时序描述,首先,要详细说明一帧图像中各种脉冲所占行数,例如锯齿脉冲、后均衡脉冲、数据有效行脉冲、前均衡脉冲[3-4]。如果是隔行模式,则要为奇、偶场分别进行时序描述。其次,对每种脉冲进行具体到像素的描述,主要描述各种脉冲的高低电平跳变位置,电平持续时间等信息。不管这些信息如何变化,对一种视频格式来说,每行总的像素个数是固定的,例如525i格式一行总的像素为858个[3]。

表1指令定义

指令指令码IDLE16'b1110_TIMER[11:0]INIT16'b1111_1111_1100_0000SLEP16'b1111_1111_1111_1111EVTS16'b0000_EVT[11:0]EVTWS16'b0001_EVT[11:0]EVTB16'b0100_RPT[5:0]_BLK[5:0]EVTBX16'b0101_0000_00_BLK[5:0]EVTX16'b1100_0000_0000_EVT[3:0]EVTY16'b1100_0001_0000_EVT[3:0]RPTX16'b1100_0100_BLK[7:0]RPTB16'b1101_RPT[5:0]_BLK[5:0]GOSUB16'b1100_0101_imm8[7:0]RETN16'b1100_0110_0000_0000WRCX16'b1000_imm12[11:0]WRCY16'b1001_imm12[11:0]WRAC16'b1010_imm12[11:0]WRSL16'b1011_imm12[11:0]JUMP16'b1110_1111_imm8[7:0]BRIET16'b1110_1110_imm8[7:0]JPCMD16'b1111_1111_1110_0000WRAGC16'b1010_1111_1111_1111NOP16'b1110_0000_0000_0000

数字复合时序信号的时序描述的第一步,是定义总线高电平所对应的值(WRAC 221)。由于数字复合时序信号是用来模拟复合同步的模拟信号,故数字复合同步信号的高低电平不能简单用1和0表示,需要用总线来表述。可根据视频标准来定义数字复合同步高低电平所对应的总线值,例如525i的复合同步高、低电平分别对应221和0。

第二步,描述各种脉冲所占行数。由于[4]525i是隔行模式,故分奇、偶场进行时序描述,每场的行数为262.5行(525/2),525i格式的时序图如图2所示。

奇场(图2中4~266行)包含[4]:6个锯齿脉冲(占3行时间)、6个后均衡脉冲(占3行时间)、253个有效行、1个半行、6个前均衡脉冲(占3行时间),共262.5行。偶场(图2中266~525和13行)包含:6个锯齿脉冲(占3行时间)、6个后均衡脉冲(占3行时间)、1个半行、253个有效行、6个前均衡脉冲(占3行时间),共262.5行。以锯齿脉冲为例,程序描述如下:

//Serration Lines (6个锯齿脉冲)

EVTB5,1// 循环执行下面两条指令6次

GOSUB serration// 跳转到子程序serration

WRSL0// WE_SLOPE = 0

图2 525i格式的时序图

第三步,对每种脉冲进行详细描述,具体到像素。主要对各种脉冲的上升沿、下降沿、高低电平的值及高低电平持续时间等信息进行描述。以锯齿脉冲的子程序serration为例:

Serration:

GOSUB slope_down// 跳转到子程序slope_down

IDLE714 // 锯齿脉冲低电平持续时间 715T

GOSUB slope_up // 跳转到子程序slope_up

IDLE106 // 锯齿脉冲高电平持续时间 107T

RETN

slope_down:// 产生有10个阶梯的下降沿

WRSL-23// WE_SLOPE -23

WRSL-22// WE_SLOPE -22

IDLE 7 // 执行8次(WE_SLOPE - 22)

WRSL0 // WE_SLOPE值不变

RETN

slope_down: // 产生有10个阶梯的上升沿

WRSL22// WE_SLOPE +22

IDLE 7 // 执行8次(WE_SLOPE + 22)

WRSL23// WE_SLOPE +23

WRSL0 // WE_SLOPE值不变

RETN

锯齿脉冲serration子程序首先跳到slope_down子程序,产生锯齿脉冲的下降沿;然后执行下一条命令“IDLE 714”,该命令使总线为0的状态保持715个单位时间。然后执行slope_up子程序,该子程序产生锯齿脉冲的上升沿,原理与slope_down类似。最后再执行命令“IDLE 106”,也即slope_up的最后一个阶梯值221保持107个单位时间。所有的serration子程序执行完后产生的波形如图3所示。

图3 锯齿脉冲serration

由于描述指令代码的可编程性,数字复合同步信号的精度可通过修改描述指令代码实现,只需改变数字复合时序信号上升沿和下降沿跳变期间的阶梯个数。

3)525i的视频复合时序信号实际上就是将程序按照表1翻译为对应的指令码。例如:由于表1中定义WRAC对应的指令码为16′b1010_imm12,则指令WRAC 221对应的机器码为0xA0DD。

对于当前例子525i的视频复合时序信号,不需要启动数字时序信号发生器。通过CPU将机器码存储到数字复合时序信号发生器的存储器中,也即图1中的RAM_ana。存储器的深度应以所要支持的视频格式中机器码最长的视频格式为标准来定义。

4)数字视频时序发生器从系统复位开始一直处于休眠状态,图1中的wakeup信号用来唤醒数字视频时序发生器,使其处于工作状态。wakeup的时间点可以具体到某一行的某一个像素点,由CPU配置。视频时序发生器被唤醒后从休眠状态跳到IDLE状态,然后开始运行机器码。

视频时序发生器包括指令解码器和指令跳转器两部分。指令跳转器产生存储器的读地址,存储器将读地址中对应的机器码传递给指令解码器。指令解码器对收到的机器码进行解码,解码的依据为表1所定义的指令。例如当16位指令的高8位是8′hEF时,当前指令解码为JUMP。解码后的指令送给指令跳转器。

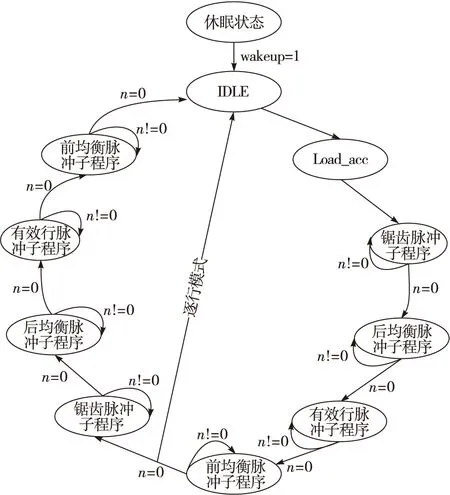

如图4所示,指令跳转器是一个状态机,主要控制指令的状态和存储器的读地址跳转。

图4 指令跳转器

默认状态下,状态机处于休眠状态,CPU的初始化也可使状态机从任意状态跳回到休眠状态。通过CPU配置wakeup有效,状态机开始工作,从休眠状态跳到IDLE状态,并在下一个时钟跳到Load_acc状态。Load_acc状态用来设置同步信号高电平的值,当前例子525i模式中将同步信号的高电平设为221,同步时序信号从该状态开始输出。

Load_acc状态只有一个节拍,下一个节拍将根据时序信号的指令描述跳到锯齿脉冲的子程序部分。硬件将程序中记录的锯齿脉冲子程序地址作为存储器的读地址,从存储器中读取锯齿脉冲的子程序,并将程序中锯齿脉冲的个数n记录下来。根据子程序中描述的总线状态,包括总线上升沿、下降沿、高低电平的值等信息产生一行的锯齿脉冲,然后返回到主程序,判断n是否为0,不为0则继续跳到锯齿脉冲的子程序中,循环执行该子程序,直到n为0为止。然后程序跳转到主程序的后均衡脉冲程序部分,同样根据程序记录后均衡脉冲的个数n和子程序的地址,然后根据此地址跳转到后均衡脉冲的子程序部分,经过几个循环产生相应个数的后均衡脉冲,再跳回到主程序中。后面的几个脉冲产生的方法与前面描述的锯齿脉冲方法类似。当一帧图像的时序信号完成,程序跳回到主程序的开始,重复执行上述机器码,产生下一帧的时序信号,如此循环下去,连续的时序信号就产生了。

视频时序信号发生器根据需要可以产生任意分辨率的时序信号,可以满足各种视频显示格式的要求。在实际应用中,这样的视频标准多样化,它的运用领域广泛,可应用于各种尺寸的显示设备,没有视频尺寸方面的限制,例如液晶电视、广告墙、车载电视等。

4 总结

本设计通过软件控制视频信号的时序,即描述指令的可编程性,可方便调整同步信号的时序,例如:同步头宽度、前肩宽度、后肩宽度、有效数据的起始位置等;另外,描述指令的可修改性,使得该设计只需根据不同视频模式修改输入给硬件的机器码,不需要增加额外的硬件设计,大大节约了硬件实现成本。

本设计可以满足输出行场信号的周期性和输入、输出行场信号的同步性。实现了多标准的视频格式输出,可以满足各种视频显示格式的要求。弥补了现有时序发生器精度低、缺乏灵活性的不足。

[1]姜秀华,张永辉,章文辉.数字电视原理与应用[M].北京:人民邮电出版社,2003.

[2]李志辉.浅谈数字电视技术的现状与发展[J].数字技术与应用,2012(10):219-220.

[3]黄子强.液晶显示原理[M].北京:国防工业出版社,2006.

[4]KEITH J.视频技术手册[M].5版.杨征,田尊华,张杰良,等,译.北京:人民邮电出版社,2009.

Method of video sequence signal generator

MIAO Huiling

(HangzhouSilanMicroelectronicsCo.,Ltd.,Hangzhou310012,China)

A new method of video sequence signal generator is described, and the detailed design structure is provided. By the software configuration of different timing instruction code, the instruction code is decoded by the instruction decoder and jump instruction in generator, then arbitrary continuous timing signals are generated, including small size and large size display equipment timing signal, and irregular resolution timing also can be produced. Multi standard video format can be outputed by video timing signal generator to meet the requirements of a variety of video display format.

sequence signal generator; digital sequence signal; video format

TN911.72

BDOI:10.16280/j.videoe.2016.10.010

核高基(核心电子器件、高端通用芯片及基础软件产品)科技重大专项(2012ZX01031-002-002)

2016-08-23

文献引用格式:苗绘玲.视频时序信号发生器的实现方法[J].电视技术,2016,40(10):45-49.

MIAO H L.Method of video sequence signal generator[J].Video engineering,2016,40(10):45-49.

苗绘玲(1978— ),女,本科生,主研视频信号处理。

责任编辑:时雯