基于CPLD的四位计数显示

梅李林 赵瑛 沈祖斌

【摘 要】设计的计数器能实现从0到9999的计数,并具备清零功能。计数器采用原理图层次化设计的方法,用四位七段数码管显示。通过分时复用技术,实现数码管的分时复用和熄灭前导零。运用QuartusⅡ软件进行设计和功能仿真,最终下载到EPM240T100C5N开发板上验证。

【关键词】CPLD;分时复用;前导零;多位计数

0 引言

CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL发展出来的器件,是一种用户根据自身需要而自行构造逻辑功能的可编程数字集成电路。其基本设计方法是使用集成开发软件平台,采用多种输入方法,如原理图、硬件描述语言、状态图及输入输出响应法等,并生成相应的目标文件。通过下载电缆将构造代码下载到目标芯片中,实现所设计的数字系统。

使用的集成开发软件平台为QuartusⅡ。QuartusⅡ为Altera公司的综合性PLD/FPGA开发软件,具有原理图、VHDL、VerilogHDL、AHDL和Megafunction等多种设计输入方式,内嵌有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

一般来说,QuartusⅡ软件开发平台为使用者给予了和结构基本无关系的全集成化环境。把软件布局、软件布线以及软件系统的验证都全部放入到一个无缝环境中,使设计人员可以非常方便快捷地对 PLD 产品实现设计输入、编译、仿真以及器件编程下载。QuartusⅡ平台汇集了包括概念设计、算法开发、建模仿真等集成环境,是一款综合性非常强的开发软件,能够很好地实现自设计输入至硬件配置的完整 PLD 设计方法及步骤流程,是能够在一个相对单一的特定设计空间内,给予一系列综合、仿真和下载的软件工具,这对加强硬件系统设计的环境有着积极的意义。

设计四位计数器中使用了原理图的方式,在QuartusⅡ上来描叙整个设计流程,同时采用功能仿真的方式来进行结果的验证,并经过下载电缆将构造代码写入EPM240T100C5N开发板中进行最终的验证。采用分时复用技术来实现数码管的控制,分时复用技术是用一条线路传输多路数据,基于分时段使用同一线路的技术。在此设计中,有四个七段数码管,若不用分时复用技术则每个七段数码管都需要与之对应的引脚和译码器,一共需要28(7*4)个引脚和四个译码器。而使用分时复用技术只需要一个数码管的引脚加上四个位选的引脚,一共只需11(7+4)个引脚和一个译码器。这对于系统I/O资源紧张的设计是个有效节省I/O资源的方法,并节省设计的成本。

1 设计四位计数器

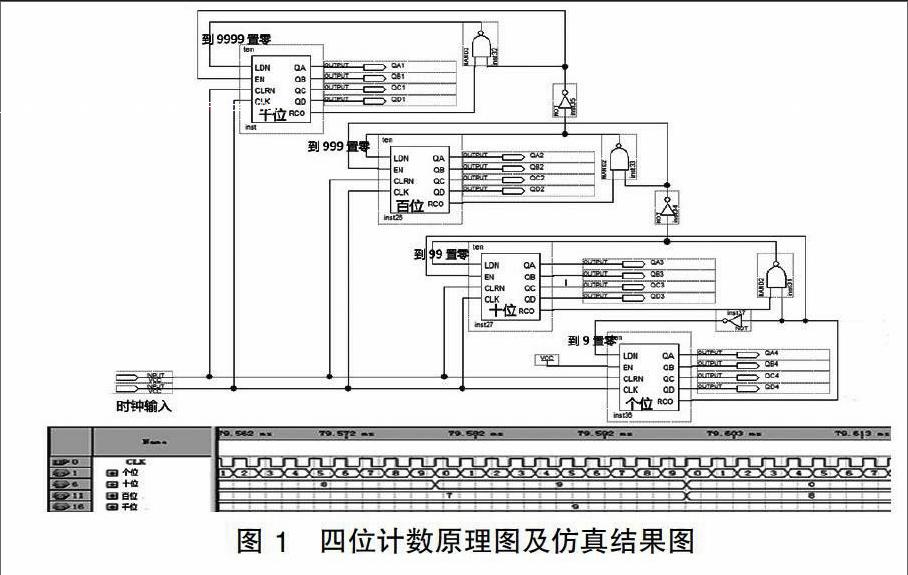

四位计数采用74LS161的同步置数法,每一位的计数状态为(0000)→(0001)→(0010)→(0011)→(0100)→(0101)→(0110)→(0111)→(1000)→(1001)→(0000)。四位计数使用4个74LS161级联,分别表示个位十位百位千位,最大能表示的数为9999。采用原理图层次化设计的方式,将4个74LS161的CLK时钟脉冲输入端串连在一起。计数采用同步置数法,使用个位的进位使十位CEP和CET使能。每当有一个进位到来的时候上一位使能一次,在时钟脉冲的作用下加1。这样就实现了初步的计数器。

于是发现一个问题:当十位为8的时候,个位的进位信号到来会使十位为9。由于采用的置数法,当十位数中当出现1001的时候,就会产生一个进位信号并且会重置当前位。这就导致计数器十位百位千位的9不能正常显示。

经过对这个现象的分析,发现是在进行计数器设计的时候,没有考虑到十位百位千位重置问题,简单的以为和个位一样出现9就重置并产生进位。通过对计数原理和同步置数法的分析,发现十位百位千位的重置不是出现9就重置。例如十位,如果要将十位数重置为0,只有当十位本身为9且个位产生下一个进位的时候,才能重置十位并给百位一个进位信号。设计的思路为当脉冲到来时开始计数,产生的进位信号直接给上一位数,上一位数由于有进位信号的使能于是加1。如果十位要给上一位进位信号且重置自身,那么就需要下一个进位信号和自身的进位信号通过一个与非门得到一个低位信号。低位信号重置自身,并通过一个非门产生进位。设计的原理图和通过QuartusⅡ功能仿真的结果如图1所示。

图 1 四位计数原理图及仿真结果图

2 四位显示的分时复用

图2 四位显示的分时复用原理图

四位计数显示采用了分时复用技术。分时复用是用不同时段来传输和处理不同的信号,能达到多路传输和处理的目的。四位显示的分时复用原理图如图2所示。通过一个4选1的选择器来选择显示的位数。将一个周期划分为4个等分的时间,每个等分的时间通过4选1的选择器来选择一个输入,并通过BCD码到7段字形的处理,最终显示在七段数码管上。当人眼在观察数码管时,光信号传入大脑神经,需经过一段短暂的时间,光信号的作用结束后,视觉形象并不会立即消失,这种残留的视觉称“后像”,视觉的这一现象则被称为“视觉暂留”。正是由于视觉暂留的存在,在多位计数的时候才得以采用分时复用,人眼被欺骗而认为是四位同时在显示。

3 熄灭多位显示的前导零

在计数器中我们发现刚刚开始计数的时候计数器显示为0001,千位百位十位的零没有任何意义。这样显示出来不符合一般的阅读习惯,也不利于数字的辨识。如果出现这样的零就是属于前导零。在四位七段数码管中有4个控制位选的引脚,查询开发板原理图得知数码管的位选引脚是低电平有效。通过控制数码管的位选端达到熄灭前导零的目的。熄灭前导零不是当某一位出现0就熄灭这一位的数码管,而是当某一位为0且前面没有不为0的数,那么就熄灭这一位以及前面所有的0。如果一个数为0但是前面有一个非0的数,那么这一位0是有效的,不能熄灭。如图3为通过位选控制前导零的原理图。

(1)如果某一位数为0,同时这一位数前面没有非0的数。它的BCD码0000通过或非门后为高位,由于2-4译码器默认输出低位,将2-4译码器输出的这一位低位与通过或非门运算得到的高位进行或运算,最终产生一个高位信号给位选端,位选端无效,熄灭这个为0的数码管。

(2)如果某一位不为0,通过或非门后得到低位,这个低位通过与门后为低位。这个低位信号和2-4译码器的低位通过或运算得到的为低位,于是位选端有效,点亮这一位数码管。

(3)如果某一位为0且前面有不为0数。不为0的这一位通过或非门后为低位,为0的这一位通过或非门后为高位。它们通过与运算后得到的还是低位,再与2-4译码器输出的低位进行或运算得到一个低位,于是位选端有效,点亮这个为0的数码管。

4 结果验证

在上面进行仿真结果正确后,就可以进行引脚分配。在引脚分配之前需要选择使用的器件型号,本设计使用了合肥零零电子科技有限公司的EPM240T100C5N开发板进行目标芯片的在电路验证。在进行引脚分配时需要查询四位计数器中使用的七段数码管、重置、时钟脉冲在开发板中的引脚编号,然后进行分配。在进行引脚分配后需要重新编译后才能下载运行。

将开发板的JTAG与USB下载线连好,接通电源。在QuartusⅡ中选择“Tools-Programmer”进行下载写入。下载完成后观察开发板上的数码管显示结果。验证结果和预期完全一样,至此说明设计没有问题。

5 总结

四位计数显示采用QuartusⅡ作为开发平台,通过原理图来设计整个流程,并采用了层次化设计的方式使得整个设计的流程更加清晰。整个设计中使用数码管的显示,分时复用等技术。分时复用技术在多位计数显示上的使用,使得系统中有限的I/O资源能显示更多的位数,从而大大的降低了成本。这种设计方式将会被很多领域借鉴并使用。我们在设计中考虑到了人们的阅读习惯,于是熄灭前导零,使设计出来的计数器更加人性化,只有这样才能被人类所接受。

【参考文献】

[1]欧阳星明.于俊清.数字逻辑(第四版)[M].华中科技大学出版社,2009.

[2]周润景,图雅,张丽敏.基于QuartusⅡ的FPGA/CPLD数字系统设计实例[M].2007.

[3]吴亮亮.基于QuartusⅡ平台的数字系统设计[J].电子电路设计与方案,2016.07.008.

[4]谈宏华.用CPLD实现多处理器数据的分时共享[J].单片机与嵌入式系统应用,2005(10):12-14.