基于FPGA的E1成帧器的设计与实现

徐思燕,邓宇

(西华大学计算机与软件工程学院,成都610039)

基于FPGA的E1成帧器的设计与实现

徐思燕,邓宇

(西华大学计算机与软件工程学院,成都610039)

提出一种基于FPGA的E1成帧器的设计与实现,分析E1基本帧和复帧的结构,设计基于FPGA的E1基本帧、复帧的接收同步检测和发送形成帧的电路,完成E1成帧器的RTL描述,并利用ModelSim仿真软件对设计的电路进行仿真验证。

FPGA;E1;成解帧

0 引言

随着通信事业的不断发展,成帧器芯片的应用越来越广泛,需求量也越来越大。以往的成帧器通常使用ASIC或软件编程的方式实现。ASIC方式虽然保证了成帧器的稳定性和速度,但是它的价格一般都比较昂贵。软件编程方式虽然灵活,但是缺乏稳定性。设计一款既稳定又灵活的成帧器成为市场的需求。

本文提出一种基于FPGA实现E1成帧器的方式,它既集成了ASIC的稳定性又集成了软件的灵活性。

1 E1帧结构介绍

符合G.704标准的E1帧结构如图1所示,E1的工作效率为2048Kbit/s,图中的每一行就是一个基本帧,每个基本帧长度为256比特,由32个时隙(ts0~ts31)组成,每个路时隙由8bit码组成,其中时隙ts1~ts15,ts17~ts31分别用来传数字信息的数据时隙,ts0用来传输帧同步信号(FAS),循环冗余校验位(Ci),同步告警位(A)和备用位(S),ts16用来传输信令。

复帧(MF)由16个E1帧组成。在复帧中,E1帧被分为FAS帧和NFAS帧,两种帧在复帧结构中交替出现。FAS帧和NFAS帧的区分是通过ts0的第bit2来区分,NFAS帧的bit2为‘1’,FAS帧的bit2~bit8为帧同步信号,用来实现基本帧同步。G.704协议规定帧同步信号FAS为“0011011”。

复帧的第一帧ts16的前四个码位分配给复帧定位使用,其定位码组是“0000”,第6bit为复帧对告比特,无报警时固定为‘1’。复帧中第2~16帧的ts16作为30个话路的信令时隙,每路信令占4个码位,在这里以4比特为单位实现30路信令的同步交错复用,同时不能为“0000”。但由于目前国内使用的是公共信令,所以一般使用的帧应该是PCM31即31路话路,ts16传也为数据,本设计也是针对这种帧结构。

图1 E1帧/复帧结构

2 E1成帧器的RTL实现

E1成帧器由div_clk、deframe_module和frame_ mdoule三部分组成,分别实现E1成帧器的工作频率、解帧和成帧。

本成帧器传输的数据是E1信号,其帧的重复频率为8000帧/秒,复接后比特率是2.048Mbit/s。经过计算可知传输1位数据需要500ns,而系统的时钟为100MHz,即周期为10ns,为了达到传送与接收数据的同步且传输率为8000帧/秒,需要对系统时钟进行50分频。

deframe_module模块负责E1帧的解析。其中主要的部分就是对基本帧和复帧同步的检测。首先对基本帧的检测,根据ITU-T G.704标准要求,基本帧同步检测需要经过以下过程,第一步检测到正确的帧同步信号FAS(0011011);第二步检测下一帧是不是NFAS帧,即检测ts0的bit2是否为1;第三步,检测第3帧,第二次发现正确的帧同步信号FAS。在以上的过程中,如果任何步骤出现问题,帧的同步检测又得从第一步开始。帧同步检测确定后,如果发生以下情况之一发生就判断帧同步检测丢失,第一种情况,连续检测到3个NFAS帧的ts0的bit2位不为1;第二情况,连续检测到3个错误的FAS帧同步信号。本设计中使用了有限状态机的方法来实现对帧的同步检测和丢失检测,其框图如图2所示。

图2 基本帧同步检测状态图

根据帧的重复频率,计算可以得知,传输一个复帧的时间为2ms。复帧同步检测的条件是在8ms内接收到4个复帧中,有两个或者两个以上正确的复帧同步信号(001011)。如果出现基本帧丢失或者连续4个复帧中没有找到正确的复帧同步信号,就判断复帧丢失。

Frame_module模块是负责基本帧和复帧的成帧。本设计中主要是按照IUT-T G.704通信协议的标准要求,把接收的数据进行封装,形成基帧和复帧,其中复帧中包含FAS和NFAS两种帧,然后把包装好的信号发送出去。

3 仿真验证

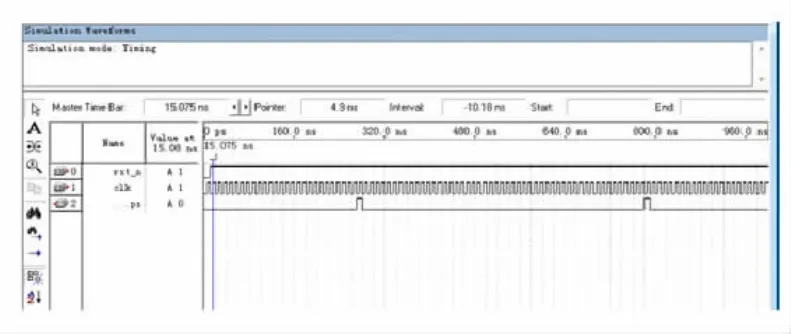

本设计中使用Verilog HDL对系统进行RTL级描述,使用ModelSim软件进行仿真。图3为时钟分频的仿真结果。图中的clk为系统时钟,clk_bps为分频后的时钟即就是E1所需的时钟频率。

图3 时钟分频仿真结果

图4为deframe_moduled的仿真模块,图中CLK为系统时钟信号,clk_bps为系统时钟分频后得到的2.048MHz的时钟信号。RX为接收到的E1帧信号,是通过仿真文件rx_module.vt写入的模拟E1信号数据。cnt、cnt_t分别为基本帧的比特计数、复帧的时间计数。fram_sig为基本帧同步检测的确定信号,当通过基本帧检测的过程后,该信号就将被置为1,进入下一次基本帧检测时,该位复位。mult_fram为复帧同步检测的确定信号,当检测到正确的复帧同步信号时,该位被置1。经过仿真验证,本设计中的基本帧和复帧的同步检测符合G.704通信协议标准要求。

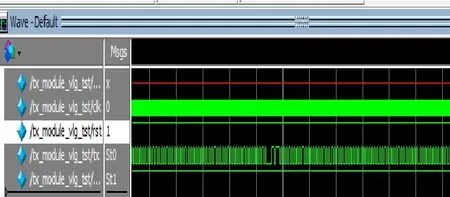

图5为frame_moduled的仿真模块,图中的clk为2.048MHz的时钟信号。rst为复位信号。tx输出为E1成帧的信号。图中的帧为FAS帧和NFAS帧,两种帧交替出现。当基本帧为FAS帧时,时隙ts0的bit2~bit8为帧同步信号(0011011);当基本帧为NFAS帧时,时隙ts0帧的第bit1用来传复帧定位信号MFAS(001011),由于复帧信号只有六位,只需用到NFAS帧的前6帧,NFAS帧的后2帧用来传误块指示比特E0和E1,时隙ts0的bit2为1,为FAS帧和NFAS帧的区分位。经过仿真验证,本设计中形成的基帧和复帧符合ITU-T G.704标准要求。

4 结语

本文设计了一个满足ITU-T G.704通信协议要求的,实现了基本帧、复帧的同步检测和成帧的E1成帧器。本文分别从E1帧结构,成解帧的RTL实现,仿真验证等方面做了详细的介绍。经过时序仿真和实验验证,证明本设计合ITU G.704标准的要求,可以在低成本FPGA上实现。该实现方式最大的特点就是灵活,它既可以定制各种电路,又减少受制于专用芯片的束缚。本设计中的FPGA芯片选用的是Altera公司低成本CycloneII系列中的EP1C12Q240C8。经过QuartusII软件的编译、时序分析和功耗分析,本设计满足资源、时序和功耗的要求。

图5 frame_moduled模块仿真结果

[1]杨锐.基于FPGA的16E1/T1光纤复接系统的研究与实现.中国矿业大学.通信与信息系统.硕士论文,2008:1-50.

[2]张秀贤,张毅等.DS21554在E1数据传输分析仪中的应用[J].微计算机信息,2008,7-1:171-173.

[3]ITU-T G.704 Synchronous Frame Structures Used at 1544,6312,2048,8448 and 44736 kbit/s hierarchical levels[S].Geneva:ITU,1998.

[4]耿立华,李占勇等.一种基于FPGA的E1数字传输分析仪成解帧实现方法[J].微计算机信息,2012,28(9):213-223

[5]帕尔尼卡.Verilog HDL数字设计与综合[M].夏宇闻,译.第2版.北京:电子工业出版社,2009.

Design and Implementation of E1 Into Frame Based on the FPGA

XU Si-Yan,DENG Yu

(College of Computer and Software Engineering,Xihua University,Chengdu 610039)

Proposes the design and implementation of a kind of E1 into frame Based on FPGA,analyzes the basic frame and E1 frame structure,basic frame,designs E1 multi-frame receiving synchronous detection and sending form the frame of the circuit based on FPGA,completes the E1 frame becoming of RTL description,and uses ModelSim simulation software to design the circuit simulation.

FPGA;E1;Framing and De-framing

1007-1423(2016)16-0044-03DOI:10.3969/j.issn.1007-1423.2016.16.013

徐思燕(1986-),女,四川宜宾人,硕士研究生,研究方向为嵌入式系统及其应用

2016-04-06

2016-05-25

邓宇(1991-),男,四川泸州人,硕士研究生,研究方向为嵌入式系统及其应用