用于非制冷红外探测器的SAR ADC设计

缪竟鸿,秦战明,陈力颖

(天津工业大学 电子与信息工程学院,天津 300387)

用于非制冷红外探测器的SAR ADC设计

缪竟鸿,秦战明,陈力颖

(天津工业大学 电子与信息工程学院,天津300387)

设计了一种用于非制冷红外探测器图像处理的12 bit逐次逼近型模数转换器(ADC),转换电压为2~4 V.其D/A转换器采用电阻和电容混合结构,节省芯片面积,减小系统复杂度;比较器采用放大锁存结构,应用失调存储技术,满足非制冷红外芯片图像处理对ADC速度与精度的要求.芯片采用Global Foundries 0.35 μm混合模式CMOS工艺进行设计和流片.仿真结果表明:在输入信号为50 kHz、采样率为1 MS/s时,信纳比(SNDR)为72 dB,有效位达到11.6 bit,模拟部分功耗2 mW,满足非制冷红外探测器对ADC指标的要求.该设计提高了非制冷红外探测器的图像处理能力,消除了ADC外接引入的噪声.

红外探测器;非制冷;数模转换器;比较器;电容阵列

红外探测器是一种可探测目标的红外辐射,并通过光电转换、电信号处理等手段将目标物理的温度分布图像转换为视频图像的设备[1].非制冷红外探测器的诞生及发展是红外技术领域一次革命性的飞跃,其衍生的非制冷红外热成像技术得到广泛应用.目前大多非制冷红外探测器通过外接ADC(模数转换器)进行信号的模数转换,容易引入噪声,不利于对信号的处理.

近年来数字技术迅猛发展,A/D转换器的速度和精度也大幅度提升,后来出现的流水线型A/D转换器更被广泛应用于图像处理[2],然而非制冷红外芯片对图像处理要求较低,内部时序要求其嵌入一组ADC阵列,单个功率较高的流水线型A/D转换器并不适合.伴随CMOS(互补金属氧化物半导体)工艺技术的提高,逐次逼近型模数转换器(SAR ADC)以其低功耗、中等分辨率、中等精度、输出数据不存在延时以及尺寸小的优势,能和非制冷红外探测器完美结合[3].本文设计一种用于非制冷红外探测器图像处理的片内逐次逼近型A/ D转换器.依据红外图像的精度和探测器的系统整体要求,本A/D转换器选用5 V电源,转化电压为2~4 V,是采样率1 Msps的12位逐次逼近型模数转换器.

1 工作原理

非制冷红外探测器采用电阻型微测辐射热计,敏感元是热敏电阻.当红外光照在一个探测像素上,被敏感区域吸收,引起其温度变化,热量从敏感区流向周围环境.温度变化不同引起不同的电阻变化,通过读出电路对信号进行逐行读出和积分,每一行信号在上一行信号读出时积分,并把它转化成电压信号,而多路复选信号开关会把每一行信号的响应信号逐一输出,并通过buffer(缓冲器)电路接到无输出延时的SAR ADC上进行模数转换,经DSP(数字信号处理)处理后接到显示器,视频标准采用60帧/s的NTSC制.

传统的逐次逼近式模拟数字转换器结构由采样保持电路及执行搜索算法的反馈环组成[4].在搜索算法中,输入电压被数字转换器的输出电压所逼近.这个反馈环由逐次逼近式逻辑模块、比较器、一个N位的数模转换器组成.逐次逼近型数模转换器的核心部分为D/A转换器和比较器.根据缩放方法划分,数模转换器(DAC)分为电流按比例缩放型、电压按比例缩放型和电荷按比例缩放型.对于低精度的ADC,采用电荷按比例缩放型的DAC(数模转换器)模块来实现,但是比较器功耗更大[5].然而伴随位数的增加,用于对电容阵列的充电和放电的功耗增多,且电容阵列的电容值呈指数增加.在高位的ADC中,电容阵列要耗费很多面积和功耗,因此降低电容阵列的面积和功耗显得很重要[6].本项目中的逐次逼近式ADC采用电阻和电容的混合架构.如图1为传统混合架构的SAR ADC的结构框图.复位后,数字逻辑电路最高位置1,其余位置0,输出通过电容、电阻阵列转换成模拟信号,此模拟信号与输入通过比较器进行比较,比较器的结果控制数字控制逻辑电路进行加权或减权,使得其输出的数字量逼近输入的值.

图1 传统SAR ADC结构图Fig.1 Traditional structure of SAR ADC

2 电路结构设计

本文设计的ADC应用到非制冷红外芯片内部用于图像处理,所以ADC的各项指标要根据红外焦平面的时钟频率、响应率、噪声等效温差的大小以及信号的动态范围决定.根据所选用红外焦平面,主时钟频率要求为5 MHz,根据奈奎斯特采样定理,采样频率至少为10 MHz,因为SAR ADC的采样频率限制,采用由10个采样率为1 MHz的ADC组成的阵列可满足要求,所以单个ADC的功耗与面积需要尽可能降低.红外焦平面响应率为10 mV/K,噪声等效温差为100 mK,动态范围为2~4 V.由此可确定,ADC的分辨率至少为=1 904,ADC的精度至少为11 bit,为保证系统正常工作,应有一定余量,选定12 bit.

2.1阻容混合型DAC电路

图1给出了传统SAR ADC的结构框图,其一般转化区间从0 V开始,为了适用于非制冷探测器读出电路的信号对ADC的要求,把转化区间设计在了2~4 V,为满足其面积需求,设计了阻容混合型DAC的电路如图2所示.

图2 阻容混合型DAC结构图Fig.2 Structure of RC hybrid DAC

一个7位(27)电阻串通过开关信号Sn连接到电容阵列的下极板,通过C0的电荷重分配来完成高7位的转化,电阻串把转化电压(2~4 V)单调地分成了128个电压,通过数字逻辑电路控制开关Swn(0)—Swn (127)和Swp(0)—Swp(127)的开关状态,因为Swn和Swp由相同的逻辑控制,所以Vrefp总比Vrefn高一个LSB.5位二进制的电容阵列完成低5位的转化,这些电容的上极板连接到比较器的输入端,电容的底极板通过开关控制信号Sp1—Sp5、Sn1—Sn5与Vrefp和Vrefn连接,电容C1~C5把一个电阻所分电压再细分为5 bit,从而完成12位的转化.由于电容的失配会产生INL,不同电容采用成比例的对管开关[7-8].基准电压源产生不随温度变化的基准电压,这个电压被用作比较器的参考电压.

阻容混合型DAC电路的工作过程如下:初始化后,进入采样和保持阶段,随着开关Sf与Sm闭合,电容阵的底极板通过开关控制信号Sn1—Sn5接入信号Vin,上极板连接到Vcom,将电容阵上的失调误差消除,采样结束后Sm先断开,Sf后断开,以减少电容上电荷的流失,开关Sn闭合,在电阻串中用逐次搜索算法找到输入电压所对应的电阻段,即使得Vrefn为小于Vin时所能取到的最大值,通过7个时钟周期完成高7位的转化,接着进行低5位的比较,电容阵的底极板切换到一个逐次逼近序列,电容C1—C5的底极板在Vrefp和Vrefn间进行选择,Sni和Spi的开闭状态相反,如Sn1闭合,则Sp1断开,直到DAC的输出电压接近VCOM,最终完成12 bit的转换.此电路结构,由于电阻串是单调的,不管电阻是否失配,高7位都是单调的,电容阵列只转化了5位,减小电容匹配难度;电容阵列和电阻阵列转化的位数可以适当调节,电阻阵列增大,可提高转化速率,但会增加功耗,引入更多开关;电容阵列直接由MOS(金属-氧化物-半导体场效应晶体管)开关驱动,如果建立开关瞬态过度的时间足够长,将不会产生失调误差.逐次逼近型ADC的简化模型如图3所示.

图3 逐次逼近型ADC的简化模型Fig.3 Simplified model of SAR ADC

图3(a)电阻电容阵列的输出电压为:

式中:Vcom为基准源输出电压;Vrefn为前7位电阻阵列的阶梯电压;Vin为输入采样电压,经7个周期后确定Vrefn为Vin所在的阶梯电阻的负端电压.图3(b)为低5位的简化模型.这样DAC的输出为:

式中:i、j分别为电阻串、电容串位数;VR+为转化电压的上限;VR-为转化电压的下限.联立式(2)和式(3)得:

电阻的积分非线性(INL)很差,电容的微分非线性(DNL)很差,因此应该加强电容电阻的匹配,保证INL和DNL达到要求.

2.2比较器

电压比较器通常分为开环比较器和可再生比较器,比较器的分辨率和分辨延时是不可调和的矛盾,要实现分辨率和速度的折中,最优解决方案就是将前置放大器和latch锁存器相结合[9-11].图4为本设计选用比较器的结构框图.本文采用带三级前置运算放大器和latch再生电路的比较器结构,同时采用输入失调存储和输出失调存储级联的消失调技术.电容C1、C2均为耦合电容,C1=C2,在复位(失调存储)阶段用于存储前置放大器的失调电压,在比较阶段用于将前置放大器输出变化量耦合到二级预放大器输入端.

图4 比较器的结构框图Fig.4 Block diagram of comparator

为了满足SAR ADC的要求,比较器的分辨率必须达到±0.5 LSB,本设计ADC的1 LSB为483 μV,比较器的增益必须满足:

式中:VS为比较器的最小输出摆幅;(VR+-VR-)/212即为ADC的最低有效位(LSB)[12-14].本设计的比较器预防大级采用三级级联的运放结构,其中放大器A1,主要对小信号进行快速响应,因此放大器A1的设计带宽比较大,增益很小;放大器A2和A3采用相同的放大电路,其采用共源共栅的放大结构,减少回程噪声,其负载采用带弱正反馈的交叉耦合结构,提高增益;锁存器采用动态锁存结构,减小功耗[15].

由于版图设计会有性能损失,在电路设计中应该有足够的设计余量,经设计优化,比较器在5 V电压下,工作频率在25 MHz,准确分辨0.2 mV.

3 版图设计及仿真结果

SAR ADC的版图是数字模拟混合集成的版图,模拟电路比较敏感,电阻电容阵列的失配,比较器的比较延时增大,都会对ADC整体性能产生很大影响.电阻阵要放在一个P+环内,且连接电阻和开关的线应该等宽,长度接近;电容采用中心对称结构,如图5所示,在电容阵列的周围加上伪电容,尽量保证各位的寄生电容成比例.比较器完全采用对称布局,尤其是每级前置放大器的输入对管,采用了多插指中心对称的结构,而且前置放大器与锁存器分别放在两个不同的保护环内,减小两者之间的干扰.ADC整体面积为5 00 μm×1 200 μm.芯片采用Global Foundries 0.35 μm混合模式CMOS工艺进行流片.

图5 CDAC的版图布局Fig.5 CDAC layout design

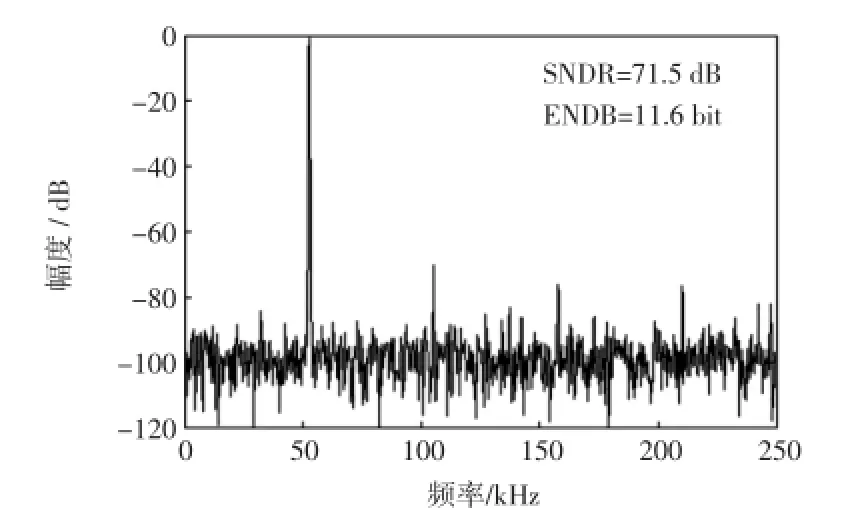

对逐次逼近A/D转换器进行整体数模混合仿真,设定ADC采样率为1 MS/s,输入正弦信号,最大幅值为4 V,最小幅值为2 V,频率为52.49 kHz,用ADC对输入信号进行连续采样,得到4 096个12位二进制数,用MATLAB对数据进行快速傅里叶(FFT)变换,得到频谱图,如图6所示.

图64096 采样数据的FFT结果Fig.6 FFT result of 4096 sampling data

由图6可见,在ADC采样率为1 MS/s,输入频率为50 kHz左右时,SNDR为71.58 dB,有效位为11.6 bit.仿真时模拟电源电压为5 V,静态电流为2 mA,满足非制冷红外探测器对ADC功耗的要求.

4 结语

本文设计了一个5 V 12位的逐次逼近式ADC,用于红外芯片片内图像处理.用电容电阻的混合结构来设计DAC,能缩小芯片面积和系统的复杂度.芯片用0.35 μm的CMOS工艺来设计,仿真结果显示信噪失真比为71.58 dB,有效位达到11.6 bit,模拟部分功耗2 mW.仿真结果显示,该ADC能够完成芯片内部的数模转换,满足图像处理对红外芯片读出电路的性能需求.

[1]邢素霞,张俊举,常本康,等.非制冷红外热成像技术的发展与现状[J].红外与激光工程,2004,33(5):441-444. XING S X,ZHANG J J,CHANG B K,et al.Recent development and status of uncooled IR thermal imaging technology[J]. Infrared and Laser Engineering,2004,33(5):441-444(in Chinese).

[2]武海军.混合结构逐次逼近模数转换器研究与设计 [D].广州:华南理工大学,2014. WU H J.Researchment and design of SAR ADC with mixture strure[D].Guangzhou:South China University of Technology,2014(in Chinese).

[3]ZHAO H L,ZHAO Y Q,ZHANG Z S.A cryogenic SAR ADC for infrared readout circuits[J].Journal of Semiconductors,2011,11:152-156.

[4]江利,赵志宾.一个10位逐次逼近式ADC电路[J].上海电气技术,2010,3(4):39-43. JIANG L,ZHAO Z B.A 10-bit successive approximation ADC circuit[J].Journal of Shanghai Electric Technology,2010,3 (4):39-43(in Chinese).

[5]CHIU Y,GRAY P R,NIKOLIC B.A 14-b 12-MS/s CMOS pipeline ADC with over 100-dB SFDR[J].IEEE Journal of Solid-State Circuits,2004,39(12):2139-2151.

[6]玻梅.低电压低功耗逐次逼近模拟数字转换器电路技术[D].北京:清华大学,2010. BE M.Approximation ADC technoiogy with low voltage and low power comsunption[D].Beijing:Tsinghua University,2010(in Chinese).

[7] MATSUZAWA A.Trends in high speed ADC design[C]//2007 7th International Conference on ASIC.2007:245-248.

[8]GU W R,YE F,REN J Y.An 11-bit 22-MS/s 0.6 mW SAR ADC with parasitic capacitance compensation[J].Journal of Semiconductors,2014(8):155-161.

[9]HONG H,LI S L,ZHOU T.Design of a low power 10 bit 300 ksps multi-channel SAR ADC for wireless sensor network ap-plications[J].Journal of Semiconductors,2015(4):162-168.

[10]PROMITZER G.A 12-bit low-power fully differential switched capacitor noncalibrating successive approximation ADC with 1 MS/s[J].IEEE J Solid-State Circuits,2001,36(1):1138-1143.

[11]AGNES A,BONIZZONI E,MALOBERTI F.Design of an ultra-low power SA-ADC with medium/high resolution and speed[C]//IEEE International Symposium on Circuits and Systems.2008:1-4.

[12]VERMA N,CHANDRAKASAN A.A 25 μW 100 kS/s 12b ADC for Wireless Micro-Sensor Applications[C/OL]//ISSCC 2006.[2015-04-22].http://www.mtl.mit.edu/researchgroups/ icsystems/pubs/conferences/2006/nverma_isscc2006_slides.pdf.

[13]WALDEN R H.Analog-to-digital converter survey and analysis[J].IEEE Journal on Selected Areas in Communications,1999,17(4):539-550.

[14]SIRAGUSA E,GALTON I.A digitally enhanced 1.8 V 15 B 40 Ms/S Cmos pipelined ADC[C]//International Solid-State Circuits Conference.2004:452-538.

[15]LEI S,QIN Y D,GAO S Q,et al.Analysis on capacitor mismatch and parasitic capacitors effect of improved segmentedcapacitor array in SAR ADC[C]//Third International Symposium on Intelligent Information Technology Application.2009:280-283.

Design of SAR ADC for uncooled infrared detector

MIAO Jing-hong,QIN Zhan-ming,CHEN Li-ying

(School of Electronic and Information Engineering,Tianjin Polytechnic University,Tianjin 300387,China)

A 12 bit successive approximation analog to digital converter(ADC)with switching voltage 2-4 V was designed for image processing of uncooled infrared detector.The D/A converter used a RC hybrid structure that minimizes the overall chip area and system complexity.To meet the requirements of the speed and accuracy of ADC,the comparator used the amplifier latch structure,and applied the offset storage technology.The chip was designed and taped out in Global Foundries 0.35 μm CMOS technology.According to the simulation results,the ADC has a signal to noise distortion ratio(SNDR)of 72 dB for a 50 kHz input sine wave at 1 MS/s.The effective number of bits(ENOB)is 11.6 bit,power consumption by the analog portion is 2 mW,these meet the requirements of the uncooled infrared detectors′indicators for ADC.This design improves the image processing capabilities of uncooled infrared detector,eliminating external noise introduced by the ADC.

infrared detector;uncooled;analog-to-digital converter(DAC);comparator;capacitor array

TN376

A

1671-024X(2016)04-0081-04

10.3969/j.issn.1671-024x.2016.04.014