多芯片陶瓷封装的结-壳热阻分析方法

高 辉,仝良玉,蒋长顺(无锡中微高科电子有限公司,江苏无锡214035)

多芯片陶瓷封装的结-壳热阻分析方法

高辉,仝良玉,蒋长顺

(无锡中微高科电子有限公司,江苏无锡214035)

随着半导体行业对系统高集成度、小尺寸、低成本等方面的要求,系统级封装(SiP)受到了越来越多的关注。由于多芯片的存在,SiP的散热问题更为关键,单一的热阻值不足以完整表征多芯片封装的散热特性。介绍了多芯片陶瓷封装的结-壳热阻分析方法,通过热阻矩阵来描述多芯片封装的散热特性。采用不同尺寸的专用热测试芯片制作多芯片封装样品,并分别采用有限元仿真和瞬态热阻测试方法分析此款样品的散热特性,最终获得封装的热阻矩阵。

多芯片封装;陶瓷封装;热阻;热仿真;热阻测试

1 前言

系统级封装(SiP)通常指将一个功能性的系统或子系统组装到单一的封装内。为了实现系统性的功能,SiP包含两颗以上具有不同功能的芯片,可能还有无源器件、MEMS等,芯片可能有2D排布或三维堆叠的形式。SiP满足了半导体行业对系统高集成度、小尺寸、低成本等方面的要求,因此受到了越来越多的关注。随着系统集成度的提高,封装体内热流密度增大,SiP的热管理和热分析变得更为关键。

陶瓷封装由于其气密性的特点,多被用在航空航天等军事领域。对于单芯片封装,封装器件的结-壳热阻可以根据相关的标准进行测试,如GJB548B-2005(方法 1012热性能)、GB/T14862-93或 JEDEC JESD51-14等[1]。由于SiP产品中存在多颗芯片,采用单一的热阻值很难准确描述内部多芯片的散热情况及芯片之间的耦合加热情况。

图1 陶瓷系统级封装(SiP)结构示意图

本文介绍了多芯片陶瓷封装的热阻分析方法,并采用不同尺寸的专用热阻测试芯片制作2D多芯片陶瓷封装样品,分别采用有限元方法和瞬态电测试法对封装电路进行热阻分析。

2 多芯片封装热阻分析与测试方法

2.1多芯片封装热阻分析方法介绍

封装的散热特性一般用热阻的概念来衡量,对于单芯片封装,热阻的定义如式(1)所示。

其中,Rjx表示芯片到某一参考位置的热阻,Tj为芯片结温,Tx为参考点的温度,Pd为芯片的功耗。对于陶瓷封装,常用的为热阻结-壳热阻(Rjc),表示芯片到封装外壳的散热性能。Rjc体现封装自身的散热能力,后期的板级、系统级热分析可以用此参数简化分析模型。

图2 2D多芯片封装热阻示意图

系统级封装(SiP)的芯片排布可以采用3D堆叠或2D平铺的方式,由于芯片之间存在相互加热现象,采用单一的热阻值不能有效描述封装的散热特性。多颗芯片同时发热的情况下,芯片的结温可以采用叠加原理来分析,即芯片温升等于自身加热功率造成的温升与其他芯片对其加热造成温升的叠加效果。

对于一个包含N颗芯片的封装,可以采用N×N阶的热阻矩阵来描述封装的散热特性[4~5]。如图2所示的SiP器件包含两颗芯片,则最终获得的热阻矩阵结构如式(2),其中Rii为每颗芯片的自热阻,表示每颗芯片到封装外壳的散热特性;Rij为耦合热阻,表示第i颗芯片对第j颗芯片的耦合加热效果。

Rii可以按照单芯片封装的热阻分析方法进行确定,本文采用瞬态热阻分析法进行自热阻的测试,下文将进行介绍。

对于耦合热阻Rij,主要用来表示芯片间的相互加热作用。本文采用的计算方法如下:

其中,ΔPi为第i颗芯片的功耗变化值,Ti和Tj分别为第i和第j颗芯片的结温。

2.2瞬态热阻测试方法

热阻测试中必须先测得芯片结温,目前业界多采用电学测试法测试芯片结温,具体可参照JEDEC JESD51-1电学法测试标准。根据GJB548B(方法1012热性能)进行陶瓷封装结-壳热阻测试时,除了芯片结温,还需要采用热电偶进行封装外壳温度(Tc)的测量。Tc的测试点一般在芯片的正下方,通常为外壳的最高温度点;但对多芯片封装来说,由于封装体内包含多颗芯片,最高壳温位置很难确定。

瞬态热阻测试法主要是根据对一个垂直于发热面的一维传热路径,当施加/断开加热功率后,发热面温度的变化与时间的平方根呈线性关系。根据JEDEC JESD51-14瞬态双界面热阻测试方法,将待测器件贴于冷板上,改变器件与冷板界面状态(一次不添加填充物,另一次添加导热硅脂或油类物质)进行两次测量,并对两次测量的温度响应曲线进行处理获得结构函数曲线,则两条曲线分离点之前的热阻即为待测器件的结壳热阻。采用瞬态法进行热阻分析时,可以省略对壳温的测量,更适合于多芯片的热阻测量。

3 多芯片封装结-壳热阻测试与结果分析

3.1多芯片封装器件

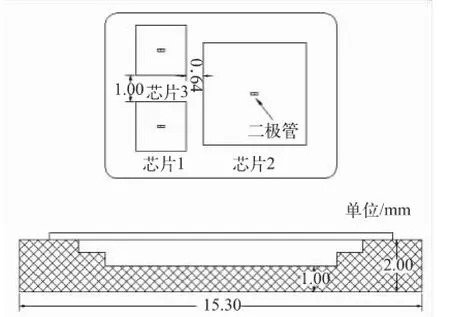

图3所示为一款CSOP24型陶瓷封装外壳界面图及其内部的芯片分布,封装体内共包含3颗芯片,其中,芯片1和芯片3的面积为1.91 mm×1.91 mm,芯片2的面积为3.82 mm×3.82 mm,芯片的距离如图中所示,芯片1和芯片3距离约1.0 mm,芯片1和芯片2距离约0.64 mm。为方便对封装芯片结温的测量,3颗芯片均为专用热阻测试芯片,芯片中心约80%的面积为有效发热区域,温敏二极管处于芯片中心的位置。

3.2多芯片封装结-壳热阻测试

根据JEDEC JESD51-14双界面瞬态热阻测试方法对CSOP24进行结壳热阻测试。热阻测试采用T3ster瞬态热阻测试仪进行,封装电路贴在冷板上,冷板通过20℃氟油进行恒温冷却。根据2.2部分瞬态法热阻测试方法,分别对每颗芯片单独施加功率,待芯片温度稳定后,断开加热功率,记录3个芯片的降温曲线;改变器件与冷板的界面状态进行第二次测试,并记录芯片的降温曲线。根据每颗芯片前后两次的降温曲线,分别获得自热阻和耦合热阻值。

图3 多芯片封装外壳及其内部芯片分布

图4为测试软件处理后得到的芯片1自热阻结构曲线,经软件的自动处理计算,确定自热阻(R11)为11.36℃/W,按照式(3)计算芯片间的耦合热阻R12为14.1℃/W。同样的方法获得其他几组热阻数据,如表1所示。

图4 R11和R12热阻测试结构曲线

表1 芯片温升及热阻测试结果

3.3测试结果与分析

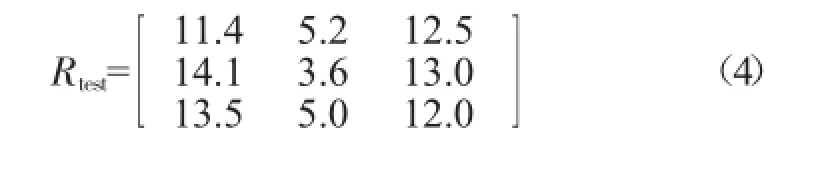

通过测试获得的热阻测试矩阵如式(4)所示。由于每个热阻测试芯片的温敏二极管在芯片的中心位置,所获得的芯片降温曲线也都是芯片中心点的降温曲线,因此按照式(3)计算得到的耦合热阻值比实际值大。

从测试结果看,芯片1和芯片3大小相同,但由于加热功率有差异,热阻值也出现一定的差异。整体的热阻矩阵并不呈对称分布,小芯片(芯片1和芯片3)对大芯片(芯片2)的加热作用要弱于大芯片对小芯片的加热作用。

4 结-壳热阻仿真与分析

4.1仿真模型与参数

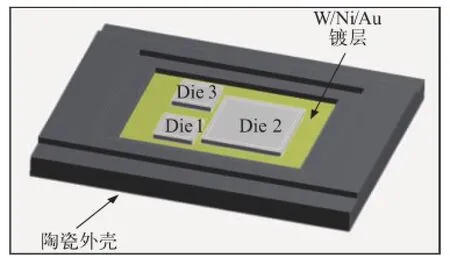

图5 多芯片封装实际芯片分布

根据第三部分的测试结果,在对芯片2施加功率时,芯片1和芯片3的温升有差异,为此对芯片的实际分布进行了确认,如图5所示,芯片1和芯片3相对芯片2的位置有差异,为此根据芯片实际分布,建立三维仿真模型如图6所示。

芯片表面80%的区域设为有效发热面积。由于热阻测试过程中获得的所有温度均为芯片中心温度,因此仿真中也取芯片中心点的温度进行分析。

图6 多芯片封装三维仿真模型

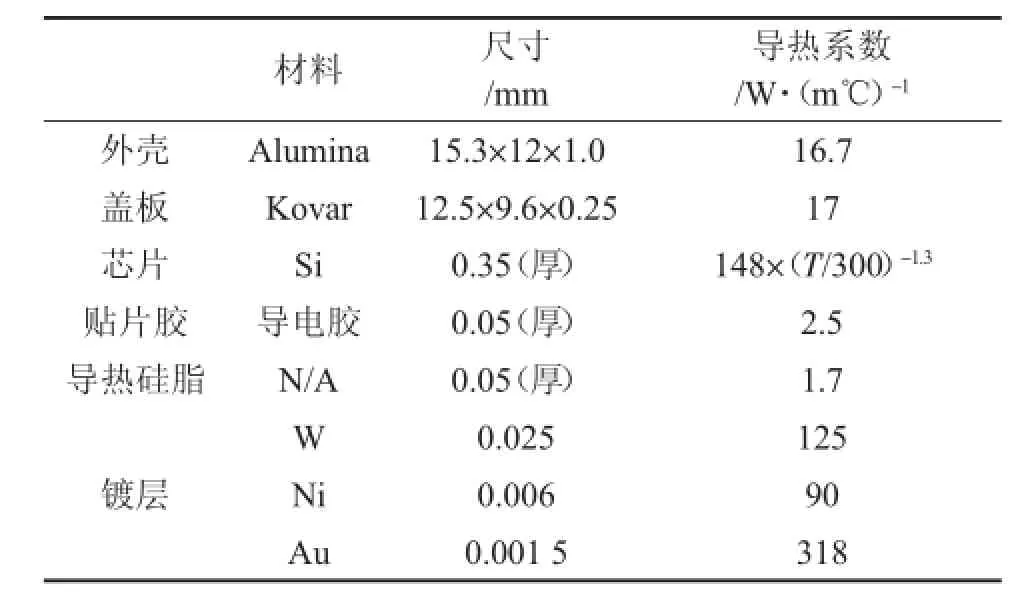

材料参数如表2所示,其中芯片(Si)的导热率对温度较为敏感,因此采用温度相关的导热系数。

表2 模型尺寸与材料参数(T/K)

4.2边界条件与结果分析

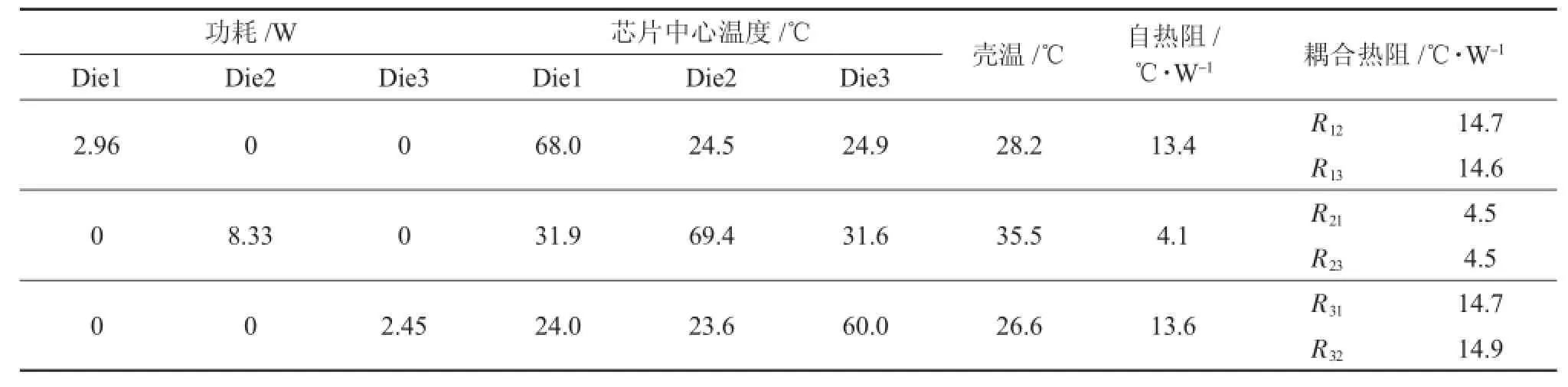

仿真时,模拟实际的测试环境,在外壳陶瓷基板底部添加一层导热硅脂,导热硅脂远离基板一侧施加恒温冷却条件(20℃)。分别对3个芯片单独施加功耗,确定各自的自热阻及耦合热阻,耦合热阻按照式(3)计算;所有芯片温度均取自芯片表面中心点,相关参数及仿真结果如表3所示。为便于比较,按表1芯片实测时的功率给芯片施加加热功率。

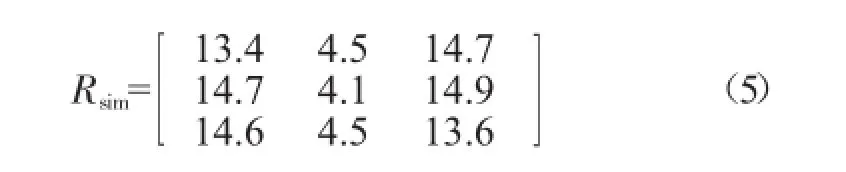

根据以上分析结果,确定此款封装产品的热阻矩阵如式(5)。

对比式(4)与式(5),测试结果与仿真结果的单项热阻值还存在一定的差异(最大的差别为2.2℃·W-1),但仿真获得的热阻值与测试值的差别在可接受范围内(误差小于20%)。由于结-壳热阻的测试结果与外部散热条件、功率等都有关系,仿真条件与测试条件的差异、材料参数的误差等都可能造成测试与仿真结果的不一致。同时,测试得到的热阻矩阵并非对称分布,即Rij≠Rji,实际情况下,两颗芯片的大小不同,相互的加热效果也不同,仿真与测试结果是一致的。因此对于多芯片封装,在封装设计阶段可以利用仿真方法对封装的散热特性进行较为准确的预估。

表3 热阻仿真结果

5 总结

本文对多芯片陶瓷封装结壳热阻的表征方法进行了介绍分析,并就一款2D多芯片封装的热阻进行仿真与测试分析。分析发现,对于多芯片封装,芯片间的互加热效应是不可忽略的。对多芯片封装可采用热阻矩阵来描述封装自身的散热特性,热阻矩阵包含芯片的自热阻及各芯片间的耦合热阻;仿真方法可以对封装的散热特性进行较为准确的预估。多芯片封装热阻分析方法对于封装自身散热特性评估、后期的整机散热分析等有着积极的意义。

[1]GJB548B-2005.微电子器件试验方法和程序[S].

[2]GB/T 14862-93.半导体集成电路封装结-外壳热阻测试方法[S].

[3]EIA/JESD51-14.Transient Dual Interface Test Method for the Measurement of the Thermal Resistance Junction to Case of Semiconductor Devices with Heat Flow Trough a Single Path[S].ELECTRONIC INDUSTRIES ASSOCIATION,1995.

[4]AndrásPoppe,YanZhang,GáborFarkas.Thermal characterization of multi-die packages[C].2006 Electronics Packaging Technology Conference,2006:1-6.

[5]MartaRencz.Thermal issues in stacked die packages[C]. 21st IEEE SEMI-THERM Symposium.

Studies on Analysis Method of Junction-to-Case Thermal Resistance of Ceramic Multi-chip Packaging

GAO Hui,TONG Liangyu,JIANG Changshun

(Wuxi Zhongwei Hi-tech Electronics Co.,Ltd.Wuxi 214035,China)

The increasing demands for higher system integration scale,smaller size andlower cost has focalized increasing public attention on system in package(SiP).For SiP multi-chip packaging,heat dissipationis of particular importance.Single thermal resistance cannot fully represent the thermal performance of multi-chip packaging.The paper introduces the analysis method of junction-to-case thermal resistance for ceramic multi-chip packaginganddescribes the thermal characteristics using thermal resistance matrix.The test sample assembled with thermal chips of different sizes is used to obtain thermal resistance matrix usingfinite element method and transient thermal resistance test method.

multi-chip packaging;ceramic packaging;thermal resistance;thermal simulation;thermal resistance test

TN305.94

A

1681-1070(2016)07-0001-04

2016-1-21

高辉(1978—),男,陕西户县人,2003年毕业于长春理工大学,同年进入中国电子科技集团公司第58研究所,主要从事集成电路封装设计及项目管理工作;

仝良玉(1988—),男,江苏徐州人,2013年南通大学硕士研究生毕业,同年进入无锡中微高科电子有限公司,主要从事陶瓷封装的设计与仿真工作。