基于有限状态机的二进制序列信号检测器的设计

李建伟(长治学院电子信息与物理系,山西长治,046011)

基于有限状态机的二进制序列信号检测器的设计

李建伟

(长治学院电子信息与物理系,山西长治,046011)

本文用Verilog HDL语言在Altera公司的现场可编程逻辑器件EP1C6Q240C8上设计了一个8位序列信号检测电路。文中介绍了Verilog HDL状态机设计电路的方法,给出了所设计电路的仿真波形,并最终在可编程逻辑器件EP1C6Q240C8上实现了该电路。

有限状态机(FSM);序列信号检测器;Verilog HDL;EP1C6Q240C8

0 引言

序列信号检测器是将一个指定序列从数字码流中识别出来,它在雷达、遥测、数据通信、密码认证等领域中用有着广泛的应用。

在设计序列信号检测器时可以采用可编程逻辑芯片和硬件描述语言相结合的方式进行,与常规的设计方法对比,该设计方法简化了电路硬件的设计过程,使设计者将更多的精力用于软件设计,而且电路设计的稳定性也有显著提高。

1 有限状态机(FSM)及其设计电路步骤

1.1有限状态机硬件优势

当前以硬件描述语言为工具,逻辑器件为载体的系统设计越来越广泛。在设计中,状态机是最典型,应用最广泛的电路模块,其结构模式相对简单、层次分明、运行速度高效、执行时间确定。

有限状态机可应用于各种系统控制,如:微处理机与外设之间的控制、工业控制数据的加密与解密,数字信号与处理中的时序控制等。

1.2有限状态机的结构示意图

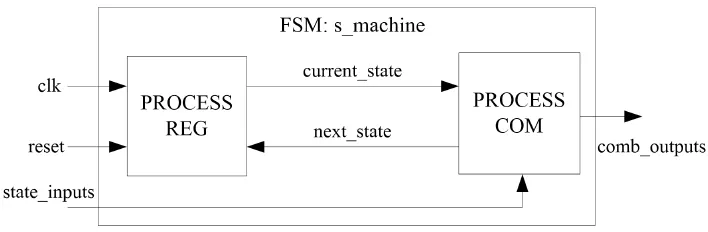

常用状态机的一般结构示意图如图1所示。

1.3有限状态机设计的一般步骤

利用状态机进行设计有如下几个步骤:

图1 状态机的一般结构示意图

(1) 定义输入变量和输出变量。

(2) 根据具体问题,定义状态机可能出现的状态。

(3) 用二进制码对出现的状态进行合理编码。

(4) 用Verilog HDL语言对状态机进行描述。

1.4设计电路说明

设计一个二进制串行输入信号为“10101110”的序列信号检测电路,并通过一个7段数码显示译码器作为检测结果的输出显示,如果串行序列为“10101110”,译码器显示“C”,否则显示“F”。

2 序列信号检测器的设计

2.1设计思路

设计时假设电路的初始状态为s0,如果输入信号按照“10101110”的次序依次输入,则电路的状态依次出现s0→s1→s2→s3→s4→s5→s6→s7→s8,当出现s8时,输出状态显示为“C”。

2.2Verilog HDL源程序

图2 序列信号发生器的仿真结果

图3 GW48实验系统电路结构图

2.3程序说明

程序中clk是时钟信号,上升沿有效;rst是异步清零信号,高电平有效。如果rst产生一个有效信号,当前状态进入s0,同时程序启动组合进程,开始执行条件分支语句。为和实验系统有机结合,程序的输出sout定义为一个4位位宽的矢量。

2.4功能仿真

在对源程序编译后,进行仿真时,选择Assignments-Settings-Simulator Settings-Simution -mode-functional仿真,仿真结果如图2所示。

仿真波形显示,当有正确序列“10101110”进入时,时序进程在时钟脉冲的上升沿会完成状态s0~s8的变化。当到了状态s8时,输出序列标志sout=1100(译码后显示为“C”),否则输出序列标志sout=1111(译码后显示为“F”)。

2.5引脚锁定

该电路的硬件测试是在GW48实验系统上完成的。GW48实验系统的核心器件是采用Alter公司的EP1C6Q240C8芯片。EP1C6Q240C8芯片是Altera公司推出的新一代低成本、中等规模的FPGAGW48实验系统的电路图如图3所示。

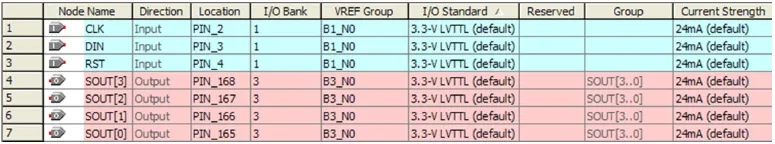

结合实验系统,在进行引脚锁定时,按键7用来控制复位信号CLR;按键6来控制时序脉冲CLK;需要检测串行序列数输入信号DIN与PIN_3连接;输出端AF接PIN_168~ PIN_165。引脚锁定如图4所示。

2.6硬件测试

编程下载后,用按键2和按键1输入两个十六进制待测序列数“10101110”(密码),按键6(CLK)8次后,串行输入的8位二进制序列码与预置码“10101110”相同,数码8的显示就从字符“F”变成字符“C”。

3 结论

用有限状态机编写的该序列检测器成功的通过了综合和布局布线,从仿真波形和硬件测试结果发现,该电路功能完全正确,实现了预定任务。通过该电路的设计可以看出,与传统的电路设计方法比较,EDA技术可以用HDL语言对数字系统进行抽象的行为与功能描述,可利用计算机在电子设计的每一个阶段来模拟验证,确保了设计过程的正确性,从而降低了设计成本,缩短了设计周期。

[1] 潘松,黄继业.EDA技术实用教程(第四版)[M].北京:科学出版社,2012.

[2] 周小仨.基于verilog的序列检测器设计[J].软件工程师,2015,(3):7-8.

[3] 张武.基于VHDL的有限状态机设计[J].华东理工学院学报,2007,30(4):366-369.

[4] 李瑞,孙显龙等.基于FPGA和VHDL的序列检测器设计[J].微处理机,2012,33(5):4-6.

[5] 刘斌,孙志雄.基于FP G A 的序列检测器设计[J].科技信息,2013, 30(6):306.

[6] 李芸,黄继业等.EDA技术实践教程 [M].北京电子工业出版社,2014.

Detecting Device Design for Binary Sequence Signal Based on the Finite State Machine

Li Jianwei

(Department of Electronic Information and Physics,Changzhi University,Changzhi Shanxi,046011,china)

In this paper,a detecting electric circuit for 8 binary digits sequence signal is designed by employing the language of Verilog HDL,based on Field Complicated Programmable Logic Device EP1C6Q240C8 from Altera Company.This paper first introduce the design method for the detecting electric circuit device by use of Verilog HDL finite state machine,subsequently show the simulation waveforms for the designed electric circuit device,and finally implement the detecting functionality of the electric circuit device at the Field-Programmable Gate Array EP1C6Q240C8.

Finite State Machine(FSM);Sequence Detector;Verilog HDL;EP1C6Q240C8

图4 EP1C6Q240C8引脚锁定

TP302

A