LED交通屏控制器的设计与应用

金 星,贾 鑫,刘 俊

(中海网络科技股份有限公司,上海 200135)

LED交通屏控制器的设计与应用

金星,贾鑫,刘俊

(中海网络科技股份有限公司,上海 200135)

针对LED交通屏在我国高速公路、城市快速路及地面道路等交通监控领域广泛应用的现状,基于Cortex-M4芯片和Cyclone IV芯片研究开发一款全功能的LED交通屏控制器。介绍该LED交通屏控制器的核心芯片、整体架构及其在交通路况显示控制方面的实现方法。经相关部门检测,该控制器性能优异、实际运行稳定,运用该控制器是一种有效、可行的LED交通显示屏控制方案。

智慧城市; 智能交通; ARM; FPGA; 交通路况显示控制

0 引 言

自1923年LED显示屏诞生以来,其相关技术随着电子工业的快速发展而得到不断提高。因其具有亮度高、功耗小、驱动简单、耐冲击、工作电压低、易于集成、寿命长和性能稳定等优点而受到广泛关注,有着极为广阔的发展前景。

LED显示屏在高速公路、城市快速路、道路交叉口等交通监控领域均有着广泛运用,被称为LED交通屏。其在高速公路上应用时主要包含以下功能:

(1) 根据与交通引导信息发布系统联动的卡口监控系统提供的监控数据,发布其管辖范围内行驶车辆的超速违章等信息;

(2) 可变成情报板,为驾驶人员提供目前的路况信息,如前方施工、车祸地点、强风、浓雾等警示标语;

(3) 可显示简单的图形、限速值等,以便驾驶人员能更好地掌握目前的路况;

(4) 作为城市道路指示,以避免因道路不熟而走错及发生交通阻塞,减少交通事故发生;

(5) 利用实时动态交通分配和交通流预测理论及LED交通指示牌为出行者提供到达目的地的最优路线;

(6) 发布人性化的友好提示信息,如谨慎驾驶、注意安全、请不要疲劳驾驶、热烈欢迎领导来视察指导工作、庆祝国庆等。

1 LED交通屏控制器核心芯片研究

1.1主处理器芯片

LED交通屏的核心技术主要集中在控制器,目前大部分异步显示屏主处理器采用的芯片都是单片机、ARM7或Cortex-M3系列芯片。

1) 单片机系列芯片(MCS-51等)具有小体积、低功耗、低成本的优点,集成了8位CPU,拥有4 000字节ROM、128字节RAM、4个8位并口、1个全双工串行口和2个16位定时/计数器;适合于红绿LED灯、道路LED指示标志灯等比较简单的LED显示屏。

2) Classic系列芯片(通用处理器ARM7)具有小体积、低功耗、低成本、低电压损耗和快速中断响应的优点,拥有32位的RISC结构处理器和高性能RISC,适用于实时系统,支持虚拟内存、简单但功能强大的指令系统,支持SRAM内存,但不支持SDRAM和DDR-SDRAM;普通应用于路口单双色LED显示屏。

3) Cortex-M3系列芯片(嵌入式处理器)在“Classic系列”基础之上强化其控制能力和电源管理,具有强大的中断管理、高代码密度和低功耗等特点,适合跑裸机程序,支持SRAM内存,但不支持SDRAM和DDR-SDRAM;可应用于高速公路、城市道路等环境较恶劣的单双色LED交通屏。

综合以上处理器的特点,不同的控制芯片在不同的较低屏上均有使用。然而,以上控制芯片受ARM微处理器的处理速度、体系架构和大容量SDRAM接口等的限制,很难在较大像素点阵、较高显示内容帧频和较复杂动态显示效果的情况下有完美动态显示效果。

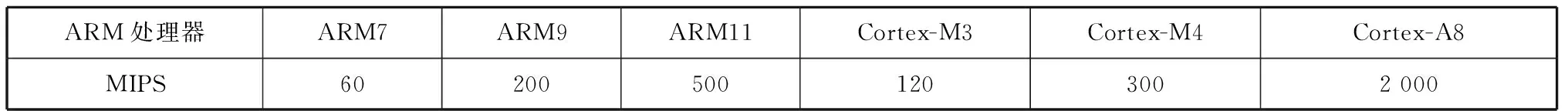

基础性能指“处理器的整数运算能力”,是处理器最重要的指标,一般用MIPS(Million Instructions executed Per Second )表示,即“每秒可以执行的百万条指令数”。表1列出了常见工业级ARM处理器的基础性能(以面世的时间为顺序,下同)。

表1 常见工业级ARM处理器的基础性能

由表1可知,ARM7的性能最差,Cortex-A8的性能最好。

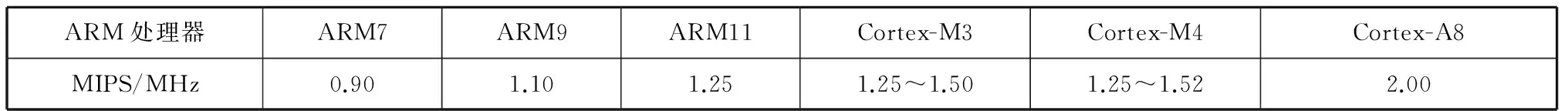

代码执行速度反映了“处理器在相同主频下的整数运算能力”,指处理器运算能力与主频的比值,一般用MIPS/MHz表示,即“每兆赫兹每秒可以执行的百万条指令数”。表2列出了常见工业级ARM处理器的代码执行速度。

表2 常见工业级ARM处理器的代码执行速度

由表2可知,ARM7的代码执行速度最慢,Cortex-A8的代码执行速度最快。代码执行速度与ARM的架构密切相关,采用新架构ARM的代码执行速度明显优于采用旧架构ARM的代码执行速度。

对于高分辨率、高刷新率的全彩LED交通显示屏,控制器需拥有较大内存来处理与交换显示的数据。以QVGA的三色屏为例,其内存最小值为230.4 KB,若再加上程序所占用的内存,则最少需要384 KB的内存。而目前几乎所有ARM处理器的内部RAM都无法满足此要求,因此必须增加外扩随机存取存储器(Random Access Memory, RAM)。常见的RAM类型有SRAM、SDRAM和DDR-SDRAM等3种。虽然几乎所有的ARM处理器都支持SRAM内存,但工业级大容量SRAM的价格极其昂贵,设计产品时一般不考虑,因此一般选择支持SDRAM或DDR-SDRRAM的ARM处理器。由于ARM7、Cortex-M3不支持SDRAM及DDR-SDRAM,因此选择ARM9或Cortex-M4之后的ARM处理器。

“Cortex-A系列”与“Cortex-M系列”相比中断管理简单、实时性较差,不适合室外恶劣环境。因此,“Cortex-M4系列”芯片是目前最适用于高分辨率、高刷新率的全彩LED交通显示屏控制器的芯片。Cortex-M4系列芯片的主要性能见表3。

表3 Cortex-M4系列芯片主要性能

1.2协处理器芯片

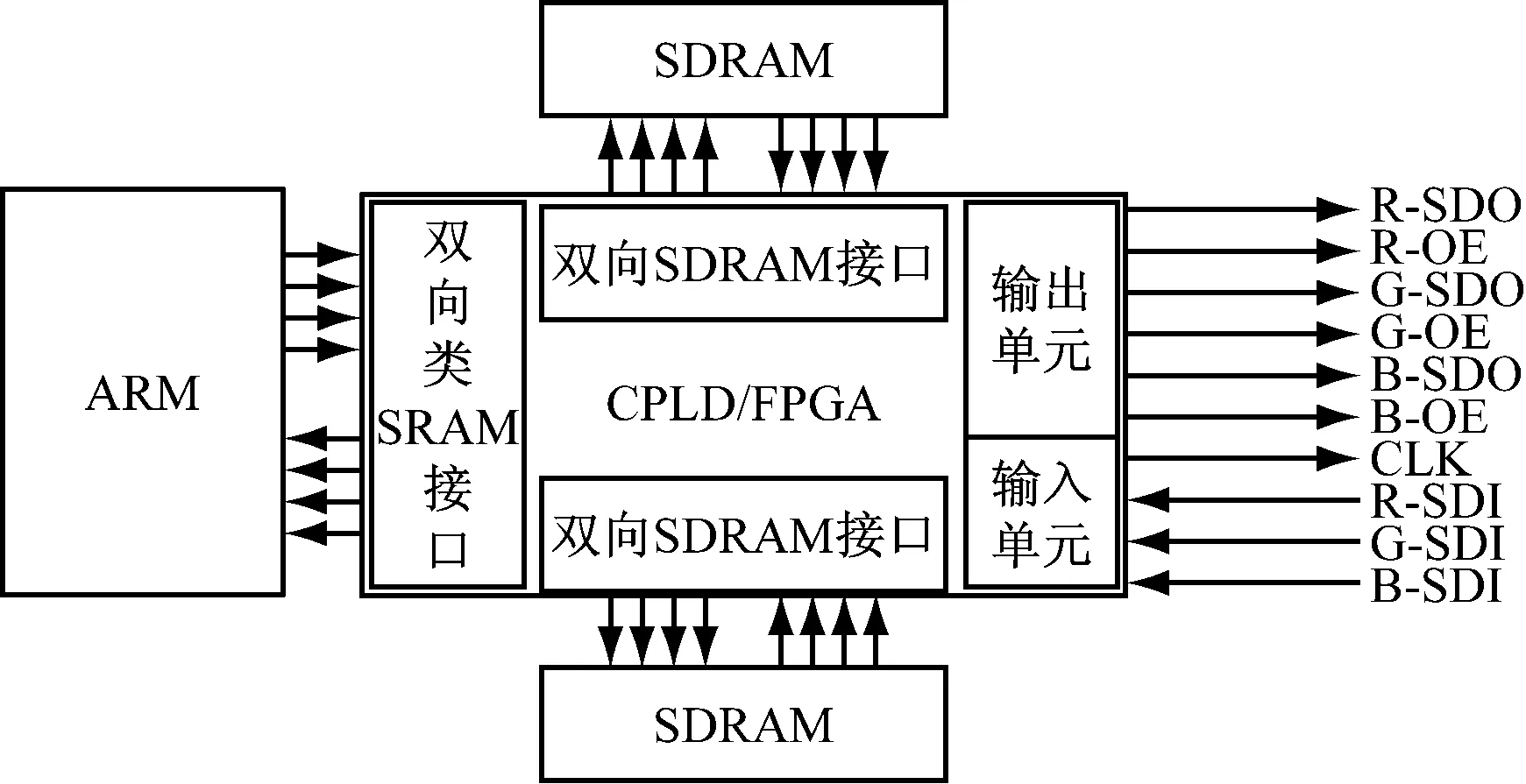

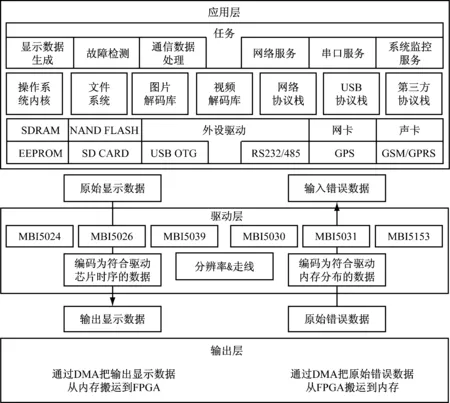

控制器中协处理器采用CPLD/FPGA。ARM负责显示数据的生成,通过“双向类SRAM接口”把这些数据发送给CPLD/FPGA;CPLD/FPGA通过2片“双向SDRAM接口”将接收到的显示数据保存到SDRAM中并发送给“输出单元”。ARM与CPLD/FPGA协同工作的框架见图1。

图1 ARM与CPLD/FPGA协同工作的框架

控制器包含1个“双向类SRAM接口”、2个“双向SDRAM接口”、1个“输出单元”和1个“输入单元”,故协处理器至少需要12 000~15 000个逻辑单元、170个用户I/O。

FPGA器件相比CPLD器件具有更高的集成度、更复杂的布线结构和逻辑实现;同时,在FPGA中有较多的软核可供使用。使用软核可极大地提高设计的稳定性并减少逻辑单元的使用。

2 LED交通屏控制器整体架构

2.1硬件架构

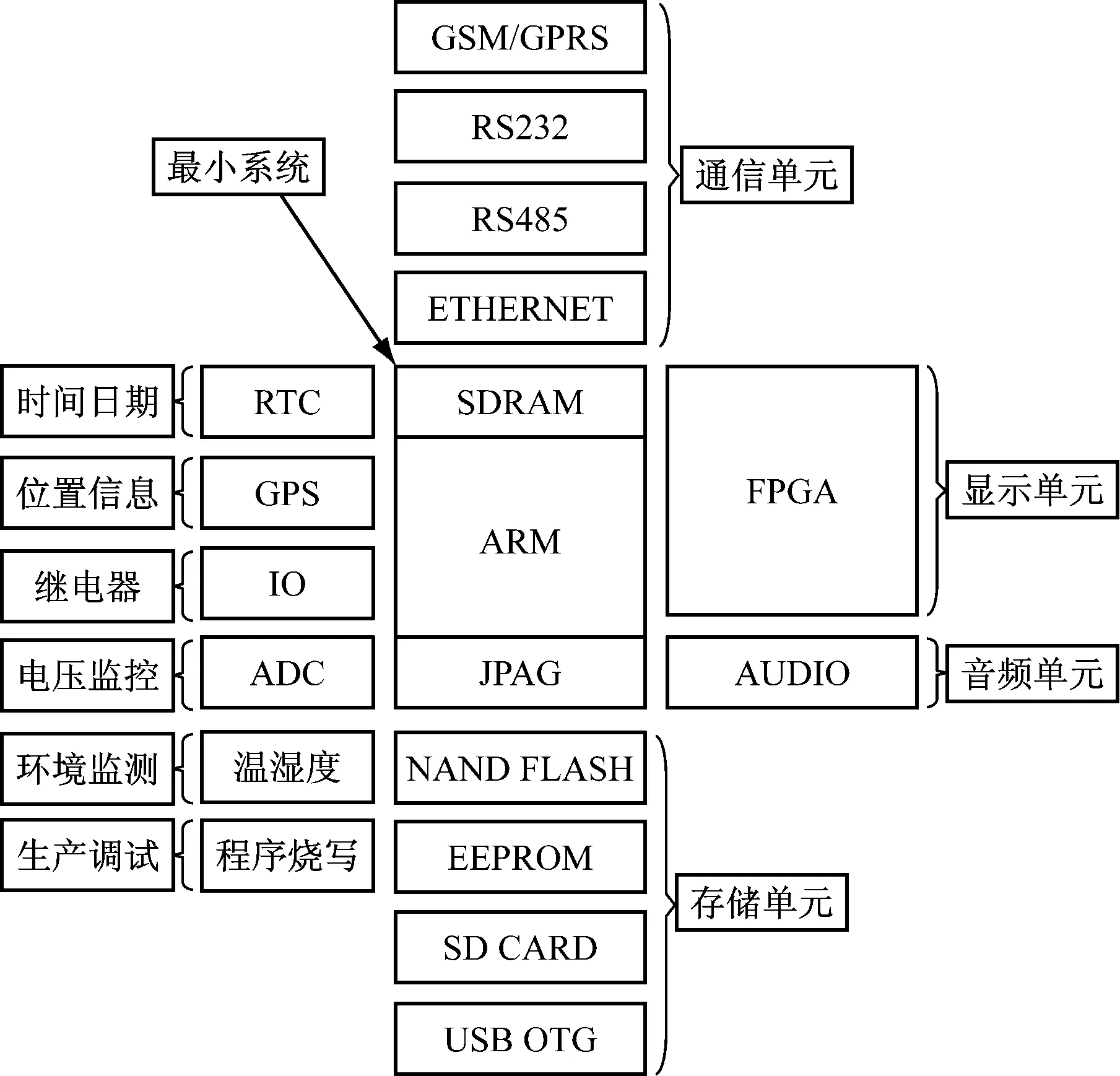

图2 LED交通屏控制器硬件原理示意图

LED交通屏控制器硬件包括“最小系统”、“存储单元”、“通信单元”、“音频单元”、“显示单元”和“其它单元”等六大部分。

2.1.1最小系统

最小系统为系统正常运行所需要的最小硬件环境,包括ARM处理器、SDRAM与JTAG调试接口及晶振等外围辅助电路。

2.1.2存储单元

(1) NAND FLASH为系统提供大容量的非易失存储空间,可用来保存字库、图片、音频和视频文件等。

(2) EEPROM用来保存系统的配置信息,如设备编号、系统版本号、MAC地址、IP地址等不需要经常改变的数据。

(3) SD CARD为系统提供可移动的存储空间,可用来保存ARM和FPGA的升级文件等。

(4) USB OTG为系统提供USB OTG接口,以便外接U盘等USB接口的存储设备。

2.1.3通信单元

(1) ETHERNET为系统提供以太网通信,可实现控制命令的接收与发送、音频与视频流的接收与发送及系统升级等功能;此外,其还提供使用以太网的第三方通信协议的支持。

(2) RS232与RS485为系统提供串口通信,方便串口设备的接入。

(3) GSM/GPRS为系统提供2G/2.5G移动通信支持。

2.1.4音频单元

音频单元为系统提供音频播放功能,包括语音播报、语音报警、视频中音轨播放等。

2.1.5显示单元

显示单元通过FPGA协处理器将ARM处理器输出的显示数据发送给LED显示屏,同时负责回收LED显示屏上的错误数据,并将最终数据返回给ARM处理器作后续处理。

2.1.6其他单元

(1) RTC单元为系统提供实时的时间与日期信息;

(2) GPS单元为系统提供地理位置信息;

(3) I/O单元为系统提供数字量的输出(如I/O信号的输出),可用来控制继电器等;

(4) ADC单元为系统提供模拟量的捕获,可用来检测电压等;

(5) 温湿度单元为系统提供环境的温度和湿度信息;

(6) 程序烧写单元为ARM和FPGA程序的烧写提供接口。

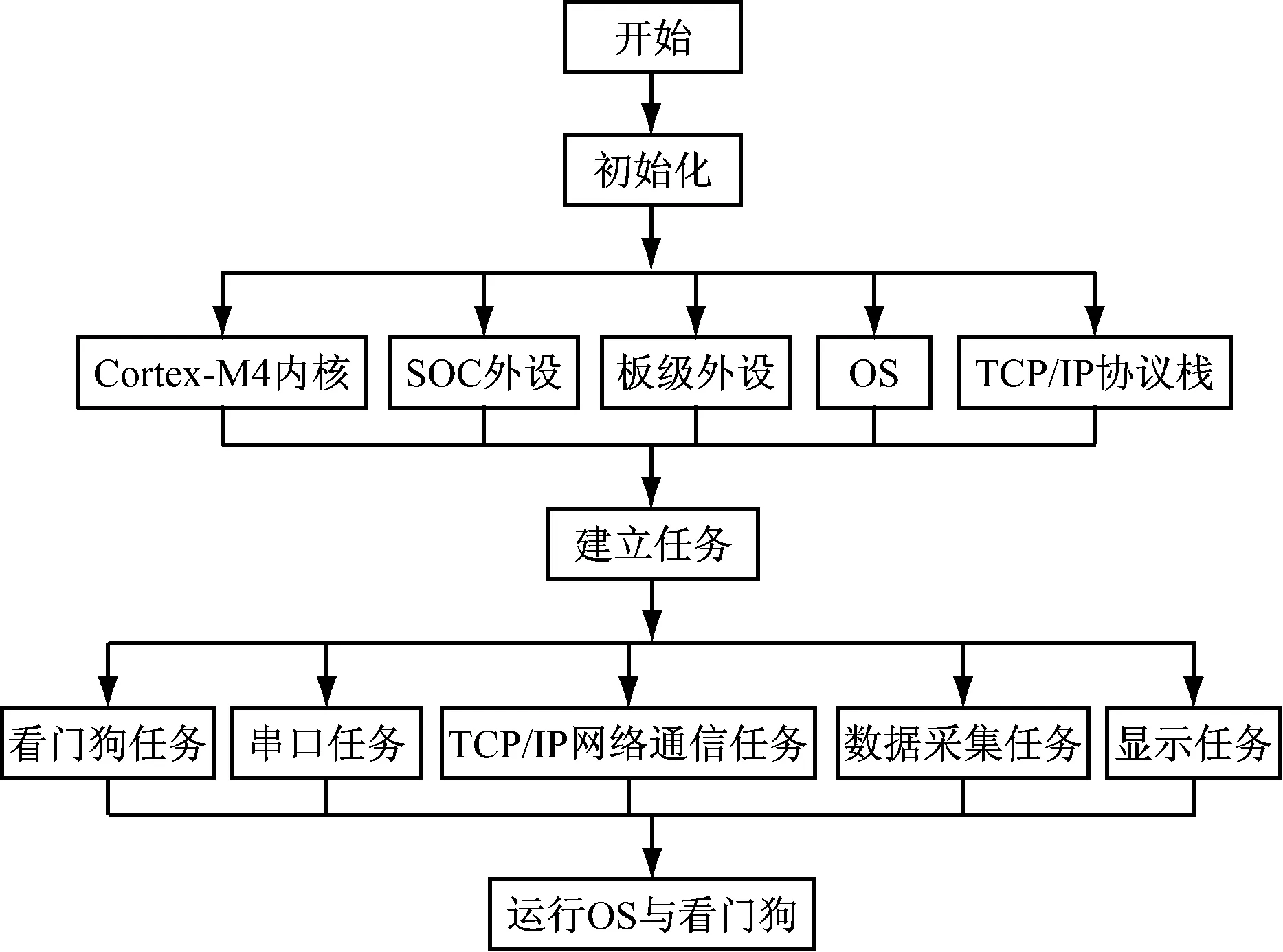

2.2软件架构

LED交通屏控制器软件部分示意图见图3,采用层次化、模块化设计。其根据显示数据流的方向分为“应用层”“驱动层”和“输出层”等3个层次。

图3 LED交通屏控制器软件部分示意图

(1) “应用层”根据显示效果生成“原始显示数据”;此外,对来自“驱动层”的“输入错误数据”进行相应处理并生成LED显示屏故障检测结果。

(2) “驱动层”将来自“应用层”的“原始显示数据”编码为符合驱动芯片时序的数据,即生成 “输出显示数据”;此外,将从FPGA中获取到的LED显示屏错误回收数据生成“原始错误数据”。

(3) “输出层”将来自“驱动层”的“输出显示数据”通过FPGA发送给LED显示屏;此外,将来自“输出层”的“原始错误数据”解码为符合内存分布的数据,即生成“输入错误数据”。

程序主框图见图4。

图4 程序主框图

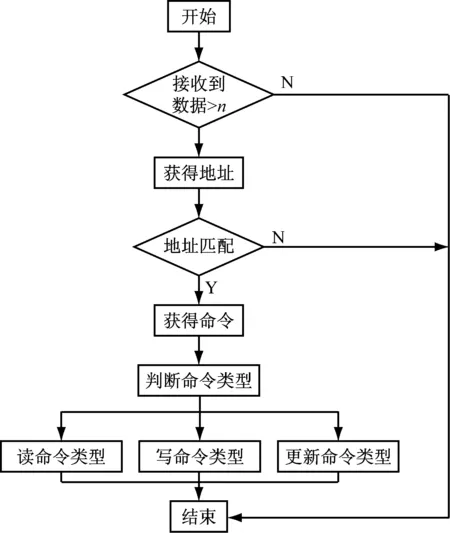

当LED交通屏控制器接收到数据并放置堆栈中时,下一步就需要对堆栈中的数据进行分析重组。例如:对接收到的数据进行数学计算,判断发送来的数据是不是给本显示屏的数据,分析出是何种命令,根据具体的命令对接收到的数据进行结构组建,以便能够有序地向显示屏驱动电路发送数据和控制信号。具体的数据解析流程见图5。

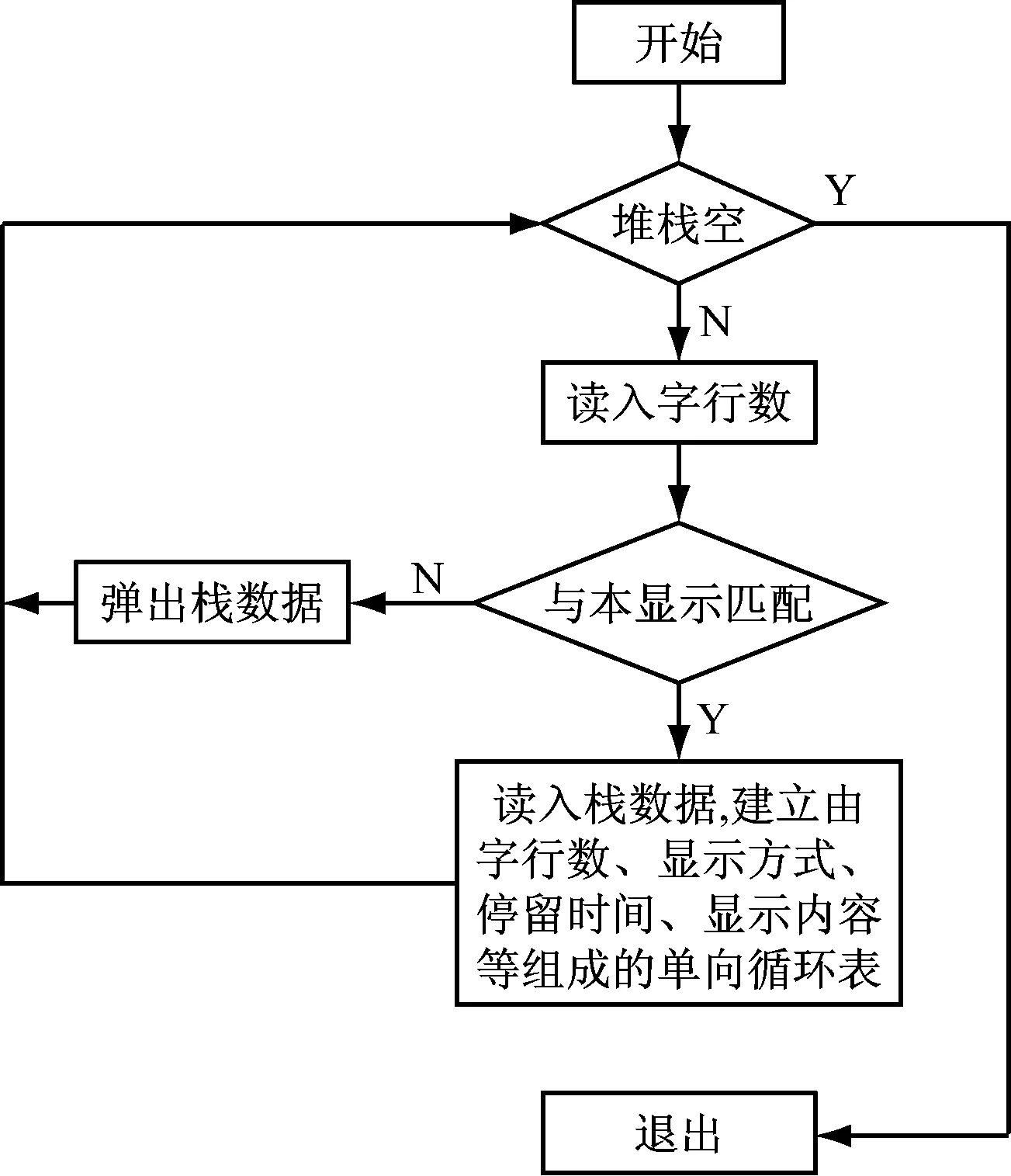

当程序对命令的类型作出判别后,须对不同的命令采用不同的处理方法。以写命令为例:程序首先判断发送来的数据的大小和本显示屏的大小是否相符,只有在相符时程序才把与显示相关的参数放到预先设置的结构体中,并建立以此种结构体为节点的单向循环链表,每个节点就是显示屏内容的依据,其他的相关命令与此类似。写命令类型处理流程见图6。

图5 具体数据解析流程

图6 写命令类型处理流程图

3 LED交通屏的交通路况显示控制

3.1道路交通状况说明

LED交通屏不仅能够显示道路文字指示,而且可以根据中心发送的指令显示当前路段的通行状态,从而方便道路使用者选择最佳的线路。

3.2交通屏与道路交通路况交互的设计

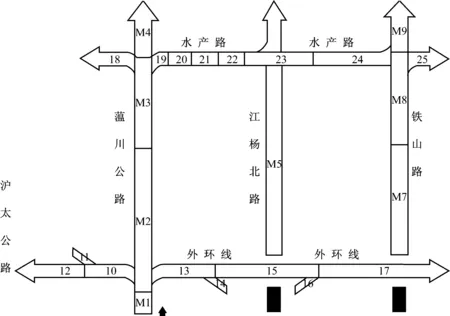

在LED交通屏正式使用之前,需将交通道路显示图与显示分段数据(见图7)烧录至控制器。

图7 交通道路显示图与显示分段数据

3.2.1烧录协议

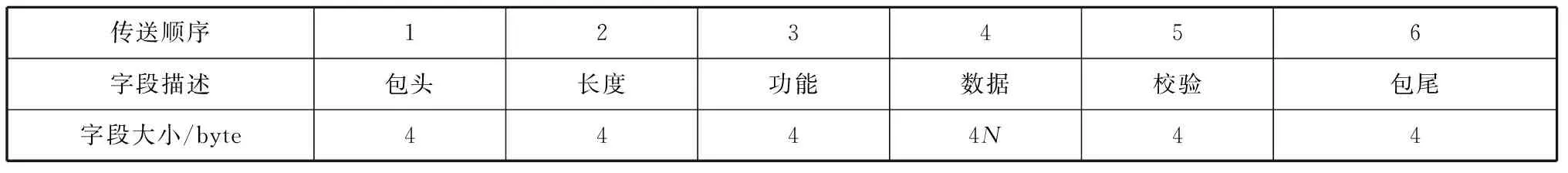

表4为烧录软件与LED交通屏控制器之间交互的简易通讯协议。

表4 烧录软件与LED交通屏控制器交互简易通讯协议

(1) 包头:包头字段标记1个数据包的开始。

(2) 长度:长度字段指功能字段字节长度与数据字段字节长度之和。

(3) 功能:功能字段标记当前数据包的功能,不同功能的数据包中的有效数据代表的意义不同(0x00000001表示清除所有图片光带信息数据;0x00000002表示清除某个图片光带信息数据;0x00000003表示写入某个图片光带信息数据;0x00000004表示读出某个图片光带信息数据)。

(4) 数据:数据字段指要传送的有用数据。

(5) 校验:校验字段用来判断数据包是否完整有效,算法采用CRC32,校验的数据包括长度字段。

(6) 包尾:包尾字段标记一个数据包的结束。

3.2.2软件界面

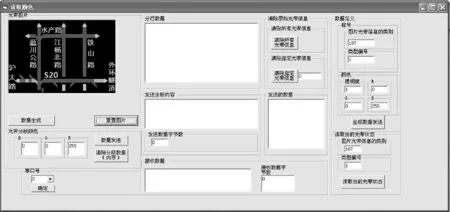

烧录软件界面见图8。首先根据实际交通道路显示图制作同比例像素点阵大小的图片;其次用不同颜色标记实际不同路段,并把各路段颜色记录在表格中;最后在软件界面填写对应参数,对各路段进行数据烧录。

图8 软件界面

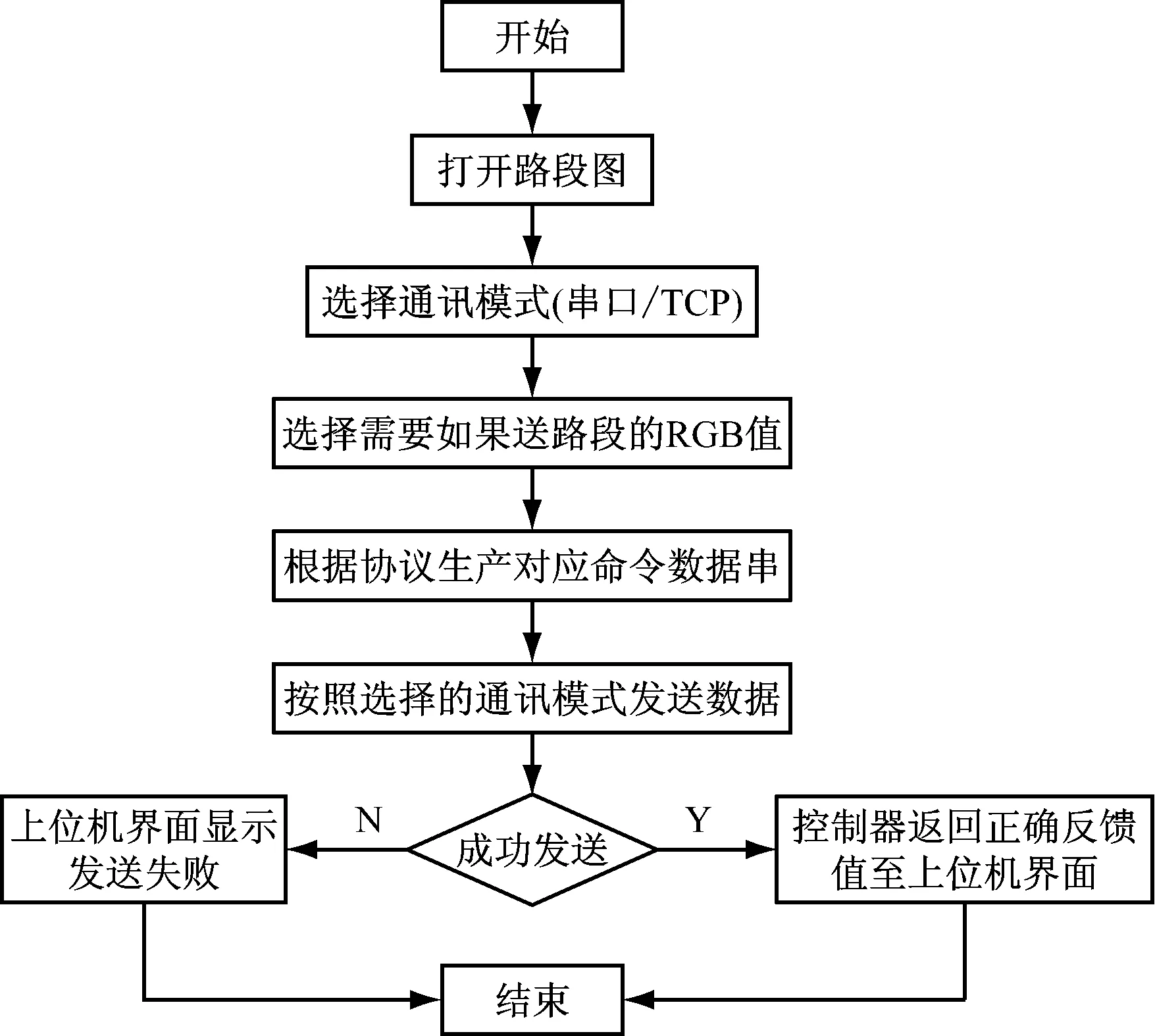

图9

上位机程序框图见图9。

4 结 语

研究和设计了以Cortex-M4系列中工业级芯片为主处理器、以Cyclone IV系列工业级芯片为协处理器的LED交通显示屏控制器。具体分析了该控制器的控制平台选择、硬件架构、软件实现方式和交通路况显示。

经相关行业检测部门检测,该控制器性能优异、生产成本低、实际运行稳定,运用该控制器是一种可行、有效的LED交通显示屏控制方案。由该控制器控制的LED交通显示屏相比其他常规交通屏控制器控制的LED交通显示屏有较大的性能提升,不仅满足目前的实际使用,而且有助于行业产品性能的普遍提升,可为全国智慧城市、智能交通提供优质的产品服务。

[1]吴厚航. 深入浅出玩转FPGA[M]. 北京:北京航空航天大学出版社,2010.

[2]奚海蛟,童强,林庆峰. ARM Cortex-M4体系结构与外设接口实战开发[M]. 北京: 电子工业出版社,2014.

[3]陈艳华,候安华,刘盼盼. 基于ARM 的嵌入式系统开发与实例[M]. 北京: 人民邮电出版社,2008.

[4]张燕,蔡伯根.城市交通信息发布系统的设计与实现[J].北京交通大学学报,2007,31(5):53-57.

Design of LED Traffic Display Controller

JIN Xing,JIA Xin,LIU Jun

(ChinaShippingNetworkTechnologyCo.,Ltd,ShangHai200135,China)

A multi-function controller for the LED traffic electronic display of traffic monitoring systems for the highway and the urban elevated/ surface road is designed with a Cortex-M4 chip and a Cyclone IV chip. The architecture of the controller and the implementation of the strategy for traffic flow control are introduced.

smart city; ITS; ARM; FPGA; traffic condition display control

2015-09-10

金星(1987—),男,江苏扬州人,工程师。主要研究方向为嵌入式控制。

1674-5949(2016)01-062-07

TN873; U495

A