一种基于光纤数据传输的多板卡软件程序烧写技术

刘 翔 袁子乔 张远安

(西安电子工程研究所西安710100)

信号数据处理

一种基于光纤数据传输的多板卡软件程序烧写技术

刘 翔 袁子乔 张远安

(西安电子工程研究所西安710100)

大型相控阵雷达信号处理中,雷达前端AD采样板数量较多,AD采样板内FPGA和DSP软件程序需要修改和更新时,需要对每块AD采样板进行程序烧写,增加了系统调试时间和调试复杂度。本文介绍了利用多根光纤将需要更新的FPGA和DSP程序上传至前端AD采样板,在板卡内完成程序烧写,较大程度节省了调试时间和简化了调试复杂度。

光纤数据传输;多板卡;软件程序烧写

0 引 言

随着大型相控阵雷达的发展和上千阵元雷达的出现[1],在雷达信号处理中的数字接收单元的板卡数量不断增加,板卡结构相同并使用相同的FPGA和DSP软件程序,在传统的雷达调试中,AD采样板的软件程序经常需要修改和更新,当软件程序修改和更新时,需要对多块板卡逐块进行程序烧写,通常烧写一块板卡的FPGA程序需要十几到二十分钟,烧写DSP程序需要5分钟左右,因此对多板卡进行软件程序更新时,需要更长的程序烧写时间,增加了调试难度和复杂度。

本文介绍了一种基于光纤数据传输实现的多板卡软件程序烧写技术,多块AD采样板通过光纤对接光纤处理板,光纤处理板通过光纤将需要更新的FPGA和DSP程序同时传递给多块AD采样板,AD采样板将上传的程序烧写至FPGA或DSP外挂的FLASH中[2-3],实现同时对多块板卡FPGA和DSP软件程序的烧写,较大程度减少了调试时间和简化了调试复杂度。

1 多板卡软件程序烧写系统设计

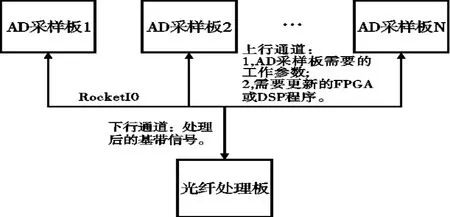

图1为多板卡软件程序烧写的系统框图。在雷达信号处理前端设计中,由多块AD采样板和光纤处理板组成,AD采样板对接收的中频回波信号进行AD采样、数字下变频、通道校正处理,将处理后的数据通过光纤下传至光纤处理板,在光纤处理板中完成数字波束形成、脉冲压缩、目标检测等功能。

多板卡软件程序烧写系统的设计基于原有工程架构,在实现雷达功能的前提下,增加此程序烧写功能。当AD采样板需要进行程序更新时,光纤处理板将新的程序通过多根光纤同时发送至多块AD采样板,每块AD采样板利用板上自有程序,将FPGA或DSP程序写入对应的FLASH中,完成程序更新。

图1 多板卡FPGA程序远程烧写的系统框图

图2为AD采样板程序更新的数据流。在光纤处理板内,利用DSP将需要更新的程序读至SDRAM中,DSP利用EMIF接口将数据传给光纤处理板的FPGA中,FPGA利用光纤发送至AD采样板FPGA缓存中,AD采样板DSP将更新的数据读至外挂的SDRAM中,当需要更新的数据全部缓存至SDRAM中时,DSP开始将数据分块写入DSP外挂的39VF040存储器中或通过FPGA将FPGA更新程序写入XCF128X存储器中,完成写操作后进行校验,正确无误后,系统重新上电,新的程序即可工作。

2 多板卡软件程序烧写实现过程

2.1 RocketIO简介

图2 AD采样板在线程序更新数据流

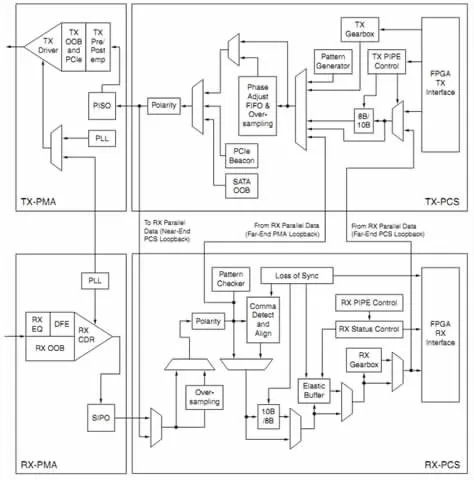

RocketIO是Xilinx在Virtex2 pro以上系列中集成的专有高速串行收发器。典型的RocketIO收发器结构[4]如下图所示,由物理编码层(PCS)和物理媒介层(PMA)构成。PCS主要由周期冗余检测CRC(CRC-Cycle Redundancy Check)、8B/10B编码器、发送FIFO、8B/10B解码器、用于实现通道绑定和时钟修正的弹性缓冲器等核心部分构成。PMA主要包括串并转换器、差分接收器、发送时钟生成电路、接收时钟恢复电路等。发送端按照一定的计算规则产生的CRC校验码插入到预发送的并行数据中,经过8B/10B编码(8B/10B编码模块可根据需要选择),写入发送FIFO,然后将其转换成差分数据发送出去。

接收端通过接收器接收串行差分数据,在时钟数据恢复(CDR)电路的作用下,从串行数据流中恢复出时钟信号,该时钟信号用于串并转换,在comma检测和对齐模块的作用下,将数据对齐并进行串并转换,输出的并行数据经过8B/10B解码(可根据需要选择,与发送端选择一致),依据需要用弹性缓冲器实现通道绑定和时钟修正,经过CRC模块校验后并行输出。

图3 V6 FPGA GTX收发器原理框图

2.2 FPGA程序烧写实现

下面详细介绍FPGA程序的烧写实现过程。

步骤一:

当AD采样板FPGA程序需要更新时,使用Xilinx自带工具IMPACT[5]将新生成的.bit文件转化为能够烧入 Flash的.bin文件,此文件大小为0x53638C*8bit(根据选取FPGA型号的不同,此文件大小会有不同)。

步骤二:

在光纤处理板中,首先利用DSP将此bin文件数据从电脑上打开并以二进制形式存入外挂SDRAM中。然后DSP需要将此bin文件数据通过EMIF接口写入FPGA。由于bin文件较大,FPGA内部FIFO容量有限,需要将bin文件分成多块,每块大小为0x200*32bit,分多次写入FPGA的FIFO中。在单次传数中,FPGA收到上传的bin文件数据将其缓存在FIFO中。上述操作过程均在光纤处理板中完成。

步骤三:

1块光纤处理板上FPGA通过多路Rocket IO与多块AD采样板上FPGA相连,此时光纤处理板将FPGA收到的bin文件通过多路Rocket IO传至多块AD采样板FPGA内。AD采样板FPGA收到数据后缓存至其FIFO中,板上DSP通过EDMA接口将FPGA FIFO中的数据读出,并存入其SDRAM的相应地址上。经过分块多次上传bin文件,可以将整个bin文件从光纤处理板中DSP的SDRAM中传递到多块AD采样板DSP的SDRAM中,此时AD采样板会通过bin文件的起始和结束标志判断收到的数据是否正确,正确则执行步骤四,不正确则告知光纤处理板重新传数,重复步骤二、三。

步骤四:

AD采样板FPGA专用FLASH芯片Xcf128x,容量为128Mbit,共有128个Block存储块(每块大小为1Mbit),对FLASH进行读写操作时均以Block为单位进行操作。存入此 bin文件,需要42个Block。DSP将SDRAM中的bin文件分成42块,通过EMIF接口写入FPGA中的相应地址。FPGA与FLASH通过异步接口相连,我们将DSP和FPGA接口的读写使能、数据和地址,与 FPGA和FLASH接口的相应信号对接起来,相当于DSP直接读写FPGA外挂的FLASH。对FLASH的每个Block进行解锁,擦除,将相应的bin文件写到对应地址的Block上,讲写入的数据读出进行校验,当操作完42个Block,且读出数据与写入数据一致时,即完成了对AD采样板FPGA外挂FLASH中bin文件的更新。由于此过程是在多块AD采样板上同时进行的,因此1块光纤处理板通过多路Rocket IO完成多块AD采样板FPGA程序的更新,整个更新过程大约需要10分钟。

步骤五:

将整个系统关电,重新加电后,多块AD采样板即会将更新后的FPGA程序从FLASH中加载到FPGA。

2.3 DSP程序烧写实现

当AD采样板DSP程序需要更新时,DSP程序编译完成,根据程序占用的大小,利用rom.bat执行程序生成需要烧写的.bix文件,以此项目为例,生成boot1.bix和boot2.bix[6]文件,文件大小为都为64K*8bit。与烧写FPGA程序类似,将其步骤介绍如下。

步骤一:

在光纤处理板中将boot1.bix、boot2.bix文件读入DSP中,数据全部缓存至DSP外挂的SDRAM中。然后将文件分块,每块大小为0x200*32bit,通过FPGA的光纤上传至AD采样板上的FPGA FIFO的缓存中。

步骤二:

AD采样板上的DSP通过EMIF接口将缓存至FPGA FIFO中的数据读入DSP中,并存入AD采样板DSP外挂的SDRAM中,经过多次传数后,数据全部缓存至SDRAM。此时AD采样板会通过bix文件的起始和结束标志判断收到的数据是否正确,正确则执行步骤三,不正确则告知光纤处理板重新传数,重复步骤二。

步骤三:

利用DSP直接操作外挂的FLASH 39VF040,对扇区进行擦除,再将程序写入相应位置,可以较快速的完成程序烧写。此烧写过程耗时约5分钟。

步骤四:系统重新上电,新的程序即可正常工作。

3 结束语

本文介绍了一种基于光纤数据传输实现的多板卡软件程序烧写技术,多块AD采样板通过光纤对接光纤处理板,光纤处理板通过光纤将需要更新的FPGA或DSP软件程序同时传递给多块AD采样板,AD采样板将上传的程序烧写至FPGA外挂的FLASH中或DSP外挂的FLASH中,实现同时对多块板卡软件程序的烧写。

社,2009.

[2]Xilinx Inc.Platform Flash XL High-Density Configuration and Storage Device[M]. USA: Xilinx Inc,2010.

[3]Texas Instruments Inc.TMS320C6000 DSP Peripherals Overview[M].USA:Texas Instruments Inc,2009.

[4]Xilinx Inc.Virtex-6 FPGA GTX Transceivers[M].USA:Xilinx Inc,2010.

[5]Xilinx Inc.Platform Flash XL Configuration and Storage Device[M].USA:Xilinx Inc,2009.

[6]Texas Instruments Inc.TMS320C6414,TMS320C6415,TMS320C6416 FIXED-POINT DIGITAL SIGNAL PROCESSORS [M]. USA: Texas Instruments Inc,2005.

[1]张广义.相控阵雷达原理[M].北京:国防工业出版

A Multi-board Software Program Writing Technique Based on Optical-fiber Data Transfer

Liu Xiang,Yuan Ziqiao,Zhang Yuanan

(Xi’an Electronic Engineering Research Institute,Xi’an 710100)

In large phased array radar signal processing,there is large number of radar front-end AD sampling board.When FPGA and DSP software programs need to be modified and updated,program on each AD sample board needs to be written,this will increase debugging time and complexity of system debugging.A technique of using multiple pieces of optical fiber to upload the FPGA and DSP program needed to be upgraded to front-end AD sampling board,on which the program writing is accomplished.Using this technique can save debugging time and simplify the debugging complexity greatly.

optical-fiber data transfer;multi-board;software program writing

TN952

A

1008-8652(2016)04-047-04

2016-03-08

刘 翔(1987-),男,硕士研究生。主要研究方向为阵列信号处理。