基于FPGA+TCAM架构的网络分流系统的设计与实现

鲁佳琪,黄芝平,刘纯武,刘德胜,陈 实

(国防科学技术大学 机电工程与自动化学院,湖南 长沙 410073)

基于FPGA+TCAM架构的网络分流系统的设计与实现

鲁佳琪,黄芝平,刘纯武,刘德胜,陈实

(国防科学技术大学 机电工程与自动化学院,湖南 长沙 410073)

网络流量分类技术为网络服务提供有力保障,在网络行为分析和网络监管方面发挥重要作用。设计并实现了一种基于FPGA+TCAM架构的网络分流系统,接入高速网络信号,恢复数据流信息,并对其进行分流管理。解决了传统网络分流系统接入速率不高,分流效果差的问题。最后对系统平台进行了测试,测试结果表明,该系统具备在高速网络环境下数据流实时分流处理的能力。

网络流量;分流;三态内容可寻址寄存器;现场可编程门阵列

0 引言

网络流量分类技术是指将混合有各种应用的流量,按其相关特性进行分类的技术。网络流量分类一直是学术界和产业界关注的重点之一。对学术界来说,网络流量分类是高性能网络协议和应用设计的基础;对运营商来说,网络流量分类是网络运营管理、网络发展规划、网络流量调度和高效能业务前瞻的依据[1]。因此,进行网络流量分类相关领域的研究具有重要的理论和现实意义。但是,传统分流设备由于不能适应高速网络环境,导致处理效率和准确率不高。传统设备的缺点一直制约着网络流量分类技术研究的发展。因此,设计并实现高接入速率、高处理效率的分流系统迫在眉睫。

网络流量分类技术分为软件和硬件两种主要实现方式。已有的软件算法包括:(1)键树结构的分类算法:包括分层树和扩展树两种结构。分层树结构查找时的回查操作导致其查找速度变慢;扩展树结构又由于重复复制大量路径致使算法的空间占用量很大。(2)计算几何学点定位算法:利用这种思想演变而来的各种软件算法也是目前相对较好的算法,如BV、HiCuts、RFC以及改进型BV算法(如ABV、AFBV等)等。其利用不同的技术提高了网络流量的处理速度,但是存在占用大量存储空间的缺点[2]。

硬件算法主要以基于三态内容可寻址寄存器(Ternary Content Addressable Memory,TCAM)的硬件算法为主。TCAM具有并行全相联结构,一个时钟周期就可以获得匹配结果[3]。TCAM是由内容可寻址寄存器(Content Addressable Memory,CAM)发展而来。TCAM相比CAM来说,每一个匹配位不仅可以存储“0”或“1”,还可以存储“X”来进行模糊匹配,匹配范围更加广泛,匹配效率也更高。尽管TCAM也存在功耗高、存储量小等缺点,但是通过分页TCAM可以降低TCAM的功耗[4],对TCAM匹配的规则集进行语义等价变换可减少TCAM所需的资源[5],这些研究都弥补了TCAM器件的不足。

根据软硬件算法的优缺点对比,本文系统平台采用TCAM作为数据匹配部分的关键器件。现场可编程门阵列(Field Programmable Gate Array,FPGA)具有并行处理的优势,且算法是在底层硬件上实现,相比多核等处理器减少了程序在操作系统上的运行时间,加快了处理速度。基于以上优点,本文采用FPGA作为整体架构的核心处理器件。最终,设计并实现了基于FPGA+TCAM架构的网络分流系统,解决了传统技术接入速率低、匹配准确性差的缺点,实现了高速网络信号快速准确的分流过滤。

1 系统硬件平台设计

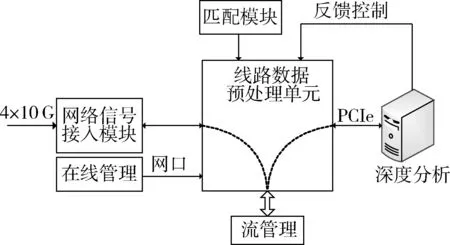

网络流量分类系统的设计关键在于如何适应高速网络信号接入的高速率。其次,网络中的信号是通过数据报文的形式进行传输的,对网络信号进行分类主要是在流的基础上进行,而流指的是在超时约束下,具有相同五元组(源IP,目的IP,源端口号,目的端口号,IP层协议号)信息的一组报文的集合。如何进行数据报文的流恢复和管理也是系统设计的关键之一。再次,互联网新技术、新应用层出不穷,网络协议格式复杂,如何快速地实时更新匹配表项也是系统设计的难点之一。基于以上几个难点将网络分流系统具体分为以下几个模块:高速网络接入模块、数据预处理单元、流管理模块、匹配模块、在线管理和深度分析模块。图1是系统平台的整体功能模块划分。

图1 硬件平台整体功能模块

系统平台通过高速信号接入模块将骨干网的高速光纤信号接入系统平台,首先在预处理单元中对接入的数据进行数据清洗、数据集成、数据变换等预处理操作[1],然后在流管理单元将分片的数据进行流恢复,获得完整的流信息。之后将流送入匹配模块进行匹配条目的对比命中操作,最后将命中的结果送到后端服务器进行更深层次的数据分析和处理。

1.1网络信号接入模块

当前骨干网的传输速率普遍为10 Gb/s,设计的系统平台要兼容10 Gb/s及以下的网络信号速率。因此,该模块采用集成化接口,将10 Gb/s的网络数据接入平台。系统设计有4路接入端口,接入速率高达40 Gb/s,可应对包括10G POS(IP over SDH)、10GE、10G WAN等不同的网络信号格式的收发处理。

1.2预处理单元

互联网的数据规模异常庞大,单单一条10 Gb/s的链路,按全天平均30%的传输负荷,每秒产生的流量数据为375 MB,一天的流量就要超过32 TB。如此海量的数据对获取、存储、查询和实时分析都增加了很大的难度。通过数据预处理可降低后续的分析规模,提高效率。

系统选用FPGA来完成预处理操作,其高速并行处理的特性非常适合系统预处理性能的需求。FPGA还要完成对其他模块的配置和管理工作。系统设计包括高速缓存、管理网口、交互接口等多种不同格式的接口模块,因此,系统选用Altera Stratix V系列FPGA芯片。该芯片拥有专用接口可以满足PCI-Express总线和4路高速接口的接入能力,并且拥有足够数量的管脚进行其他模块的管理操作。

通过编写程序实现数据报文的预处理以及对其他模块的管理操作。其中包括数据报文恢复、提取五元组信息、剔除无关报文;对TCAM表项的更新、寄存器动态配置以及对相应操作的仲裁管理[6];对高速缓存的控制和输入输出调度;通过PCI Express接口与服务器通信完成数据流后续分发处理;通过管理网口对匹配规则进行在线管理和更新。

1.3流管理模块

数据流的完整性对于匹配操作的准确性十分重要,在高速网络中,数据是以分组形式传输,每个IP包内储存部分数据。系统为了还原完整的数据内容就需要进行流管理,包括对数据的分片重组和报文乱序重组。流管理模块缓存处理好的数据流,并建立流表。如果有新报文接入,就提取该报文的五元组信息,用该五元组信息对现有流表进行HASH运算,判断该报文是否属于原缓存中的数据流。如果找到对应的流则将该报文添加到该流内;否则添加新流并更新流表。这些操作都要对数据进行缓存处理。

从系统硬件设计的稳定性方面考虑,接入速率最高为40 Gb/s,高速缓存的容量要满足40 Gb/8=5 GB的存储空间,而且带宽也要超过40 Gb/s。一般情况下缓存芯片位宽为64 bit,双倍速率读写,可获得模块的最低频率为40 Gb/s/(64×2)=480 MHz。因此,从存储容量和最低带宽来考虑,系统设计有两组缓存模块,频率可达533 MHz,其位宽为64 bit,满足最低频率要求。单片缓存模块的容量为4 GB,在内存总量上,两组缓存模块的容量为8 GB,也远大于5 GB的内存容量。根据理论分析,该设计完全满足40 Gb/s速率网络信号的缓存要求。

1.4匹配模块

在完成数据流恢复以及预处理操作之后,将数据流送入匹配模块根据表项进行匹配操作。TCAM内部可存储匹配表项,因此系统只要向TCAM输入搜索的内容,就会将此内容与匹配的表项进行比较,返回所需要的最优项,获得要执行的动作命令地址,反馈到FPGA中。随后FPGA就会根据得到的命令对匹配到的数据流进行转发分类操作,最终实现匹配模块的功能。

在系统硬件的开发中,TCAM的匹配规则将掉电丢失,如果将其存储在FPGA内部,又会占用大量FPGA的内存资源。因此,本文设计了存储匹配规则的Flash模块,实行系统开机自动更新匹配规则,减少配置匹配规则的麻烦。

1.5在线管理和深度处理模块

深度处理功能是将初次匹配成功的数据包转发至后台服务器进行更深层次的数据分类,该功能主要由PCI Express接口完成[7]。为降低PCI Express总线的开发难度,调用FPGA内部专用的资源进行开发,可配置成PCI Express2.0和PCI Express3.0。

PCI Express 2.0使用8b/10b编码,单通道速率达到5 Gb/s,x8模式下,总线速率可以达到5 Gb×8b/10b×8=32 Gb/s。PCI Express 3.0使用128b/130b编码,单通道速率达到8 Gb/s,x8模式下,总线速率可以达到8 Gb×128b/130b×8=63.02 Gb/s,除去数据包的开销等冗余字节,可以完成4路万兆数据的线速传输。

在线管理功能通过一个通信网口实现。平台的配置和管理命令信息通过网口接入到系统平台中,实现分流系统的在线配置和管理。

2 基于TCAM+FPGA的字符串匹配模块设计

数据流的匹配功能是系统设计的关键,本节进行更为深入的分析和研究。

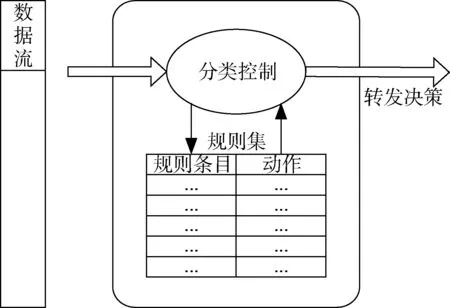

2.1硬件匹配原理

基于TCAM的流分类技术的基本处理流程如图2所示。可简单地理解为将流的标志信息输送进匹配转发引擎,将其与不同匹配规则进行逐条匹配对比,如果命中规则,则返回相对应的执行动作,分类控制器根据返回的动作对该数据流进行转发或者执行其他操作。匹配操作一般所涉及的方面为数据包头信息,即五元组信息(源地址、目的地址、源端口、目的端口、协议类型)。

图2 数据包处理流程

2.2字符串匹配模块设计

整个系统的匹配部分由FPGA与TCAM共同配合完成,过滤的规则包括五元组信息以及指定位置的应用层载荷信息等。硬件采用Broadcom公司生产的Netlogic系列芯片以及Altera公司的Stratix V系列芯片完成整体系统的构架设计。

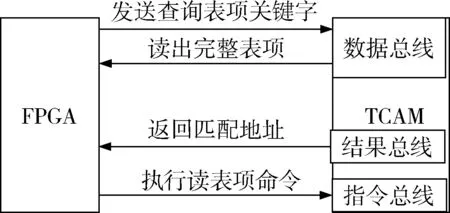

根据TCAM和FPGA的结构以及各总线完成的功能可以得到如图3所示的硬件连接基本框图。其中数据总线负责匹配数据和表项的传输以及相关寄存器的配置;指令总线负责输入指令编码;结果总线负责输出匹配结果,包括设备ID、最高优先级匹配索引等一系列信息。这些总线的管脚都连接到FPGA的通用I/O管脚上并进行等长布线。

图3 FPGA与TCAM系统模块框图

由于系统接入的速率较高,所以系统设计中要采用有效的措施提高网络数据流的匹配过滤效率。因此,在算法中将匹配规则分为两个部分进行匹配,即协议描述部分和报文描述部分(协议描述部分完成数据流五元组信息匹配工作,报文描述部分完成数据流应用层载荷信息匹配工作),这两部分的匹配表项分块存储在TCAM中,以匹配表项的第一个比特位进行区分,“0”代表数据流将进行协议描述表项的匹配,“1”表示数据流将进行报文描述表项的匹配。

具体操作流程如下:首先由TCAM进行协议描述部分的信息匹配,将数据流的五元组信息传送至TCAM芯片进行匹配操作,如果命中TCAM中的规则,表明已经确定数据流的协议特征,然后将代表协议特征的协议动作地址(Protocol Action ID,PActID)结果返回至FPGA中,如果关心该数据流中的应用载荷信息,则添加报文描述标志位进行二次匹配,否则直接根据PActID的处理命令进行处理。在进行报文描述的二次匹配时,将对特殊报文的应用层关键信息进行检测,以获得更为准确的数据流信息,从而将该重要数据流分配至专用后端处理设备进行精准的分类分析。

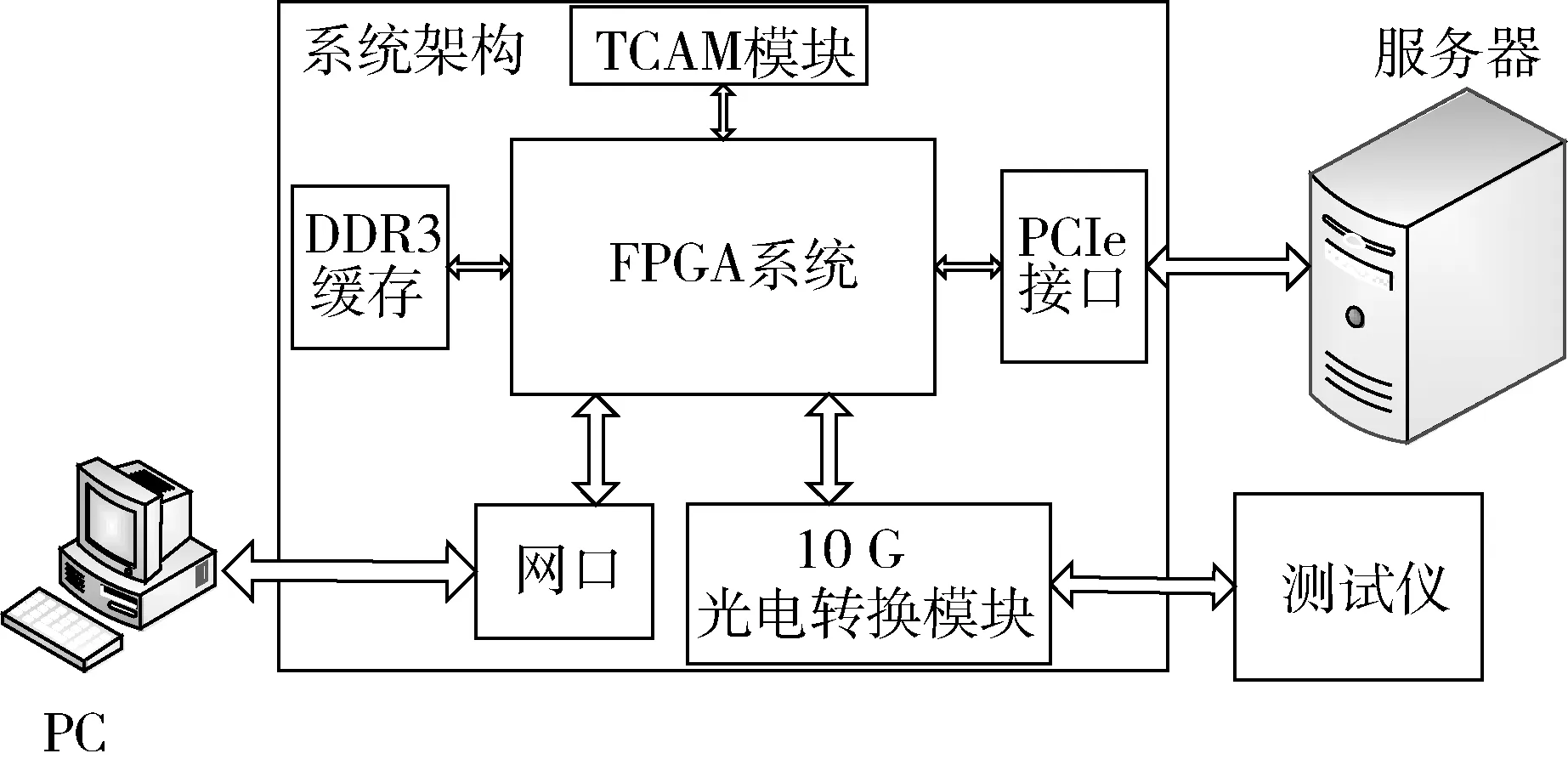

3 硬件平台测试

根据上文的设计和分析,实现了基于FPGA+TCAM架构的网络分流系统。其中包括40 Gb/s高速网络信号接口、一个管理系统的通信网口、8 GB缓存、TCAM匹配模块、PCI Express转发处理接口以及必要的时钟芯片、管理接口和电源模块。

关于该系统的测试和评价指标主要包括两个方面,即硬件的捕获效率和软件的处理分析速度。其评价因素包括以下几项[8]:

(1)系统的吞吐率:分流系统在不丢包的情况下,所能实时处理的网络数据最大带宽,即系统的吞吐率。

(2)系统的漏报率(False Negative,FN):系统在一定时间内线速处理捕获的数据,但由于系统繁忙而丢失数据,即系统会产生漏报。若流A在系统繁忙时,没有被系统识别为流A,那么就存在漏报。漏报率的定义就是没有被识别出的流A占整个流量的百分比,即:

(1)

(3)系统的更新性能:在数据流分类过程中,规则的定义和更新是系统分类处理的重要环节,过滤规则的定义要准确,更新过程要迅速。

根据以上测试评价因素,设计了如图4所示的硬件测试方案。系统平台接收来自VePAL TX300e测试仪发出的10G SDH信号,通过接收模块接收测试仪发出的网络数据,之后进行一系列的匹配分类操作,通过PCI Express接口将匹配的数据流转发至服务器进行更为深入的分析。系统测试主要对吞吐率、漏报率、误报率(体现匹配规则的设置合理性)进行测试,通过测试得到系统平台的处理性能[6]。

图4 系统硬件测试图

硬件测试结果表明,网络分流系统满足总带宽40 Gb/s的吞吐量,漏报率和误报率在系统可承受范围之内,总体性能达到设计要求。

4 结论

本文设计并实现了一种基于FPGA+TCAM架构的网络分流系统,该分流设备通过测试可以满足吞吐率等性能评价指标。该平台的研制弥补了传统分流过滤系统接入带宽低、处理效率低等缺点。下一步的研究方向是通过对分类规则的统计分析,得到匹配规则的最优设置,实现匹配条目的压缩、分割,以及通过对多报文快速并行处理来提升系统平台的整体性能。

[1] 汪立东,钱丽萍.网络流量分类方法与实践[M].北京:人民邮电出版社,2013.

[2] 王勇,周晴伦,林宁,等.IP流分类器的设计与实现[J].电子科技大学学报,2007,36(6): 1362-1365.

[3] 王建东,祝超,谢应科,等.基于FPGA的万兆流量并行实时处理系统研究[J].计算机研究与发展,2009,46(2):177-185.

[4] RAVIKUMAR V C, MAHAPATRA R N, BHUYAN L N. EaseCAM:an energy and storage efficient TCAM-based router architecture for IP lookup[J].IEEE Transactions on Computer,2005,54(5): 521-533.

[5] Dong Qunfeng, BANERJEE S, Wang Jia, et al. Packet classifiers in ternary CAMs can be smaller[C].Proceedings of the Joint International Conference on Measurement and Modeling of Computer Systems, SIGMETRICS/Performance 2006, Saint Malo, France, 2006: 26-30.

[6] 陈世文,黄万伟,曹建业.一种深度包检测引擎的FPGA硬件实现[J].测控技术,2014,33(6): 100-109.

[7] 李木国,黄影,刘于之,等.基于FPGA的PCIe总线接口的DMA传输设计[J].计算机测量与控制,2013,21(1):233-235,249.

[8] 陈曙晖,苏金树.基于内容分析的协议识别技术[J].国防科学技术大学学报,2008,30(4):82-87.

Design and implementation of flow distribution system based on FPGA and TCAM

Lu Jiaqi,Huang Zhiping,Liu Chunwu,Liu Desheng,Chen Shi

(College of Mechatronics Engineering and Automation, National University of Defense Technology, Changsha 410073, China)

The network traffic classification technology provides effective protection for the network services, and plays an important role on the network behavior analysis and network monitoring. We designed and implemented a network distribution system based on Field Programmable Gate Array (FPGA)and Ternary Content Addressable Memory (TCAM), the system accesses the high-speed network signal, recovers and manages the flow information. The system solved problems of the traditional system accessing low rate and poor distributing effective. Finally, the platform has been tested, the results show that the system platform has the ability that process the high-speed network traffic in real-time.

network traffic; flow distribution; ternary content addressable memory; field programmable gate array

TP393; TP302

A

10.19358/j.issn.1674- 7720.2016.15.019

2016-04-11)

鲁佳琪(1990-),通信作者,男,在读硕士研究生,主要研究方向:网络信号处理。E-mail:2319835109@qq.com。

黄芝平(1965-),男,博士,教授,主要研究方向:网电空间测控。

刘纯武(1963-),男,硕士,副教授,主要研究方向:网电空间测控。

引用格式:鲁佳琪,黄芝平,刘纯武,等. 基于FPGA+TCAM架构的网络分流系统的设计与实现[J].微型机与应用,2016,35(15):65-68,71.