基于AD9129的宽带信号源设计

白 玉,杨斌斌,杨承志,王 龙

(1. 沈阳航空航天大学 电子信息学院,辽宁 沈阳 110136;2.空军航空大学 信息对抗系,吉林 长春 130022)

基于AD9129的宽带信号源设计

白玉1,杨斌斌1,杨承志2,王龙2

(1. 沈阳航空航天大学 电子信息学院,辽宁 沈阳 110136;2.空军航空大学 信息对抗系,吉林 长春 130022)

针对电子战中雷达对高抗干扰性和高分辨率的需求,设计了具有大带宽、高频率的宽带雷达信号源。以FPGA为核心,采用面积换速度的思想,在FPGA中设计了多个信号生成单元,以这些单元产生多路参数相关的信号,通过多路并串转换合成一路高频信号,结合一片采样率高达2.85GS/s的高速D/A芯片进行数模转换,完成了宽带信号源的设计。通过MATLAB仿真,验证了该方法的有效性,最后利用频谱仪测试了信号源的性能指标,实测表明该信号源输出频率范围介于DC~1 000MHz,整体设计符合雷达应用需求。

FPGA;面积换速度;AD9129;宽带信号源

0 引言

伴随着电子战的发展,不仅要求现代雷达要具有良好的目标识别与超近程的探测能力,还要求其具备极高的距离分辨力和很强的抗干扰性能,这就要求雷达的发射信号具备大带宽。近年来由于匹配滤波技术和脉冲压缩技术的发展,如脉内宽带线性调频信号(WidebandLinearFrequencyModulationSignal,WLFM)在雷达系统中得到了广泛使用,它正好符合雷达距离分辨力和大探测范围的需求。

用数字方法产生宽带线性调频信号,无论在频率、幅度以及信号的信噪比等方面均优于模拟方法,且具有精度高、外围电路简单等优点。目前使用数字方式产生信号主要通过直接数字频率合成(DirectDigitalFrequencySynthesis,DDS)[1]法来实现。DDS虽然受限于FPGA的时钟频率,但其具有很强的灵活性。近年来,由于FPGA的工作频率随着集成电路的发展不断提高,越来越多的设计开始采用这种方法。例如参考文献[2]、[3]采用DDS的思想分别介绍了使用可编程逻辑器件CPLD和FPGA控制DDS芯片来产生线性调频信号。参考文献[4]利用FPGA提供的知识产权核资源,在FPGA中直接调用多个DDS核来产生波形。

上述这些设计,普遍具有花费大、设计周期长、可移植性差等问题。本文在上述文献的基础上,提出基于FPGA的DDS优化设计,通过FPGA设计了多个信号生成单元。使用多个信号单元来产生多路特定参数相关的信号,再通过并串转换技术合成为一路信号,最后借助于高速D/A芯片AD9129完成数模转换,完成宽带信号源的设计。

1 系统原理介绍

1.1工作原理

传统DDS芯片受器件工作时钟影响,导致DDS直接输出的频率上限较低,产生的信号带宽很有限。本设计利用FPGA丰富的片上资源,在FPGA中设计了多个信号生成单元,在用其输出多路调制样式各异信号的同时,用它配置AD9129来产生宽带雷达信号。AD9129实时采样率为2.85GS/s,可配置为双端口传输数据,且每个端口可使用双倍时钟速率(DoubleDataRate,DDR)来采集数据,这样每个通道的数据采样时钟便降为D/A芯片工作时钟的1/4,即700MHz左右,但在700MHz时钟下,FPGA并不能严格保证其内部路逻辑的稳定,所以采用面积换速度的方法和流水线设计的思想,在FPGA中生成8个信号生成单元,这样每个单元的工作频率便降低到350MHz,8个单元的信号通过并串转换技术合成为两路信号,D/A芯片通过两个通道采集数据后,再将其合成为一路高频信号。具体过程如图1所示。

由图1可见,在FPGA中生成了两个信号源产生模块,每个模块含4个信号生成单元,这些单元均工作在350MHz的频率下,利用FPGA提供的并串转换(OSERDES)资源进行并串转换,可将8路信号合成为2路并行的信号,2路信号经过单端转差分(OBUFDS)后转化为2对频率均为700MHz的差分信号。AD9129在700MHz的数据输入时钟DCI的驱动下,分别从P0_D和P1_D两个端口使用DDR模式来采集FPGA传送过来的两对差分信号,采样后的信号在外部时钟提供的2.8GHz时钟ADCCLK的驱动下,最终将锁存器中的数据转换为一路模拟信号进行输出。

1.2基于优化设计的信号生成单元

本文在FPGA中设计了多个信号生成单元,这些单元能够在上位机的控制下,输出特定参数的正弦波、锯齿波等。与直接调用FPGA中的DDS核相比,本方案的信号生成单元占用更少的资源,拥有更高的执行效率。其工作原理如图2所示。

k1=k2=ki=8ki∈{0,1,2...7}

图2 信号生成单元的工作原理

(1)

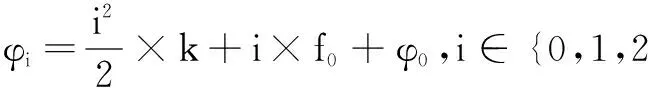

设每路信号生成单元的初始频率和初始相位分别为fi和φi,则fi和φi分别为:

fi=k×i+f0,i∈{0,1,2...7}

(2)

(3)

设计中,FPGA调用的8个信号生成单元的调频斜率、初始频率和初始相位分别根据式(1)~(3)进行配置。

2 系统方案设计

2.1DAC芯片介绍

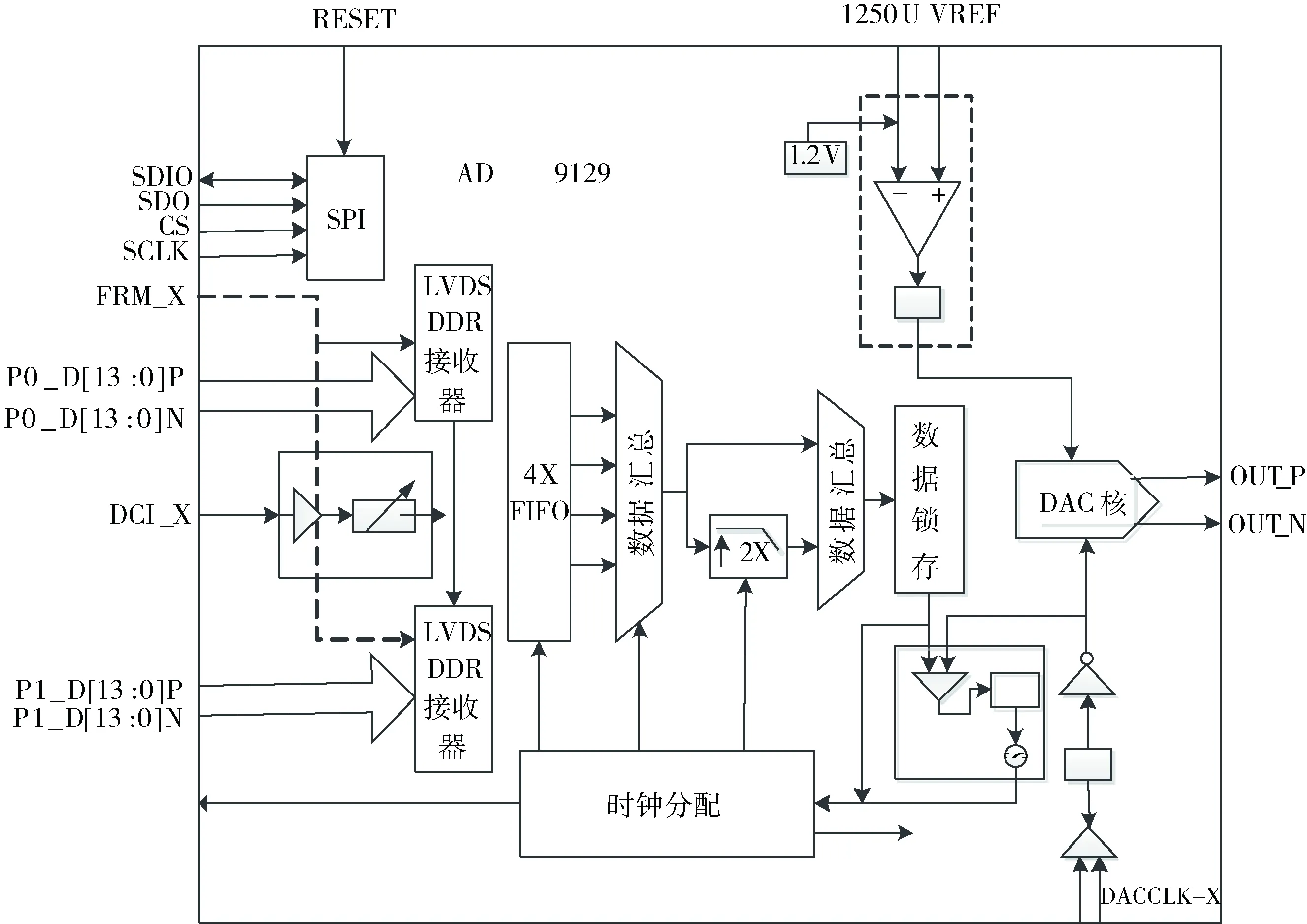

本文选用的D/A芯片AD9129是一块高性能的具有14位DAC量化的数模转换芯片,其具有双端口接口和双倍数据速率,以及低压差分信号接口,可支持2.85GS/s的最大转换速率[5]。其结构如图3所示。

AD9129芯片上的时钟全部是差分时钟信号,共有3对,分别为:D/A芯片的输入时钟DACCLK、数据输入时钟DCI、输出时钟DCO。根据配置信息的不同,AD9129可工作在不同的工作方式下,本文通过SPI串行接口向芯片内部寄存器写入配置信息,将AD9129配置为双端口传输数据,且每个端口均采用DDR模式。这样AD9129的数据时钟的频率就降为芯片时钟的1/4,降低时钟的传输频率就意味着可以提高时钟的质量,也可以提高数据传输的正确率。

图1 系统工作原理

图3 AD9129的原理结构

2.2软件设计

图4 上位机软件配置界面

在本设计中,使用上位机软件对FPGA进行参数配置,上位机软件在QtCreator5.5环境中编程实现,其通过网口与FPGA进行通信,当启动软件后,软件将自动接管系统控制权,在软件上对相应的参数进行配置后,点击发送按键即可在DAC输出端得到所需要的WLFM信号。其输入界面如图4所示。

3 验证与测试

3.1MATLAB仿真验证

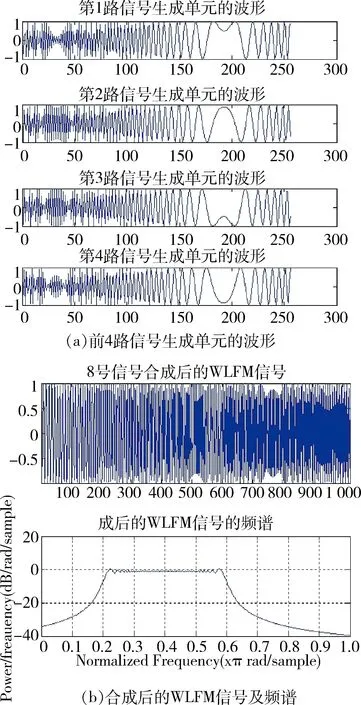

本设计提出了在FPGA中生成多个信号生成单元来产生WLFM信号。为了验证方案的可行性,使用MATLAB对该方案进行了仿真验证。通过计算及仿真,得到每个信号生成单元的配置参数,具体的仿真结果如图5所示。

图5 仿真结果

图5(a)是仿真得到的前4路信号生成单元的输出波形,图5(b)是将8路信号合成后的WLFM信号的输出波形及频谱。经对比,合成后的信号与直接使用WLFM信号公式得到的数据完全相同。

3.2系统测试与分析

本文对设计后的系统进行了成果验证,当设置起始频率为150MHz,终止频率为1 050MHz,初始相位为0Rad,重复周期为100μs,脉冲宽度为100μs时,实测得到WLFM信号的频谱如图6所示。

图6 实测WLFM信号的频谱

在未滤波的情况下,从实验截图可看出,输出信号的频谱在1GHz左右,带内平坦度约为3dB。实测观察到信号源输出频率范围介于DC~1 400MHz。可见,本设计实现的宽带信号源达到了设计指标要求,满足实际工程需求。

4 结束语

本文针对目前雷达发射信号带宽较窄与频率较低的问题,利用目前最具性价比的FPGA和高速D/A芯片,设

计了带宽与频率分别可达1GHz和1 400MHz的宽带信号源。使用上位机软件配置FPGA的参数,利用FPGA产生信号,通过高速D/A进行数模转换,完成了上述信号源的设计。仿真验证表明,该设计对输出信号的带宽与频率均有较大的提升,为提高雷达发射信号的性能提供了新的思路,该方案已成功应用于某战场电磁环境产生器设计的实践中。

[1]LEEPS,LEECS,JUHL.DevelopmentofFPGA-baseddigitalsignalprocessingsystemforradiationspectroscopy[J].RadiationMeasurements, 2013,48(1):12-17.

[2] 彭昭,胡进峰. 基于FPGA的直接数字频率合成器的优化设计[J].电子世界, 2012,16(18):108-120.

[3] 柳春,甘泉. 基于FPGA的雷达信号源设计[J].电子技术应用,2013,39(11):47-49.

[4] 唐大伟,吴琼之. 基于高速D/AAD9739 2.5GSPS的宽带信号源[J].电子设计工程,2013,21(20):45-47.

[5]ADICorporation.AD9129datasheet[EB/OL].(2013-03-21)[2016-02-25].http://www.analog.com.

The design of wideband radar signal source based on AD9129

BaiYu1,YangBinbin1,YangChengzhi2,WangLong2

(1.SchoolofElectronicandInformation,ShenyangAerospaceUniversity,Shenyang110136,China;2.DepartmentofElectronicCountermeasures,AviationUniversityofAirForce,Changchun130022,China)

Aimingatthehighrequirementofradartothedistinguishabilityandanti-interferenceperformanceintheelectronicwarfare,alargebandwidthandhighfrequencysignalsourceisdesigned.Withtheprincipleofsacrificeareaforspeed,severalsignalgeneratingunitsaregeneratedinFPGAwhichisusedasthecoredevice.Withthoseunits,multi-channelsofrelatedsignalaregenerated,thosechannelsofsignalaresynthesizedtoonechannelthroughparalleltoserialconversion,combinedwithahighspeedD/Achipwhichsamplingrateisupto2.85GS/sfordigitaltoanalogconversion,thedesignisfinished.Then,theeffectivenessoftheproposedmethodisverifiedbyMATLABsimulation.Atlast,withthespectrumanalyzer,theperformanceofthesignalsourceistested,theresultsindicatethattheoutputfrequencyofthesignalsourcerangefromDCto1 000MHz,whichindicatethedesigncanmeettheapplicationsrequirementsofradar.

FPGA;areaforspeed;AD9129;widebandsignalsource

TN741ADOI: 10.19358/j.issn.1674- 7720.2016.15.009

2016-03-02)

白玉(1969-),女,硕士,副教授,主要研究方向:嵌入式系统。

杨斌斌(1991-),男,硕士研究生,主要研究方向:嵌入式系统。

杨承志(1974-),男,博士,教授,主要研究方向:电子对抗。

引用格式:白玉,杨斌斌,杨承志,等. 基于AD9129的宽带信号源设计[J].微型机与应用,2016,35(15):31-33,41.