基于FPGA的电子直线加速器低电平系统前馈功能的实现

李 松 张俊强 张 猛 赵明华(中国科学院上海应用物理研究所 嘉定园区 上海 20800)2(中国科学院大学 北京 00049)

基于FPGA的电子直线加速器低电平系统前馈功能的实现

李 松1,2张俊强1张 猛1赵明华1

1(中国科学院上海应用物理研究所 嘉定园区上海 201800)2(中国科学院大学北京 100049)

用于驱动光中子源装置(TMSR Photo-Neutron Source Phase1, TDSN1)的15MeV直线加速器,由于腔体中瞬态束流负载效应的存在使得束团在经过腔体后头部的能量过高,会导致束流能散变大,降低了束流的传输效率。“数字前馈补偿”方法在原有的数字低电平控制系统的现场可编程逻辑门阵列(Field Programmable Gate Array, FPGA)中加入前馈模块,通过直接削弱输入腔体的射频场的头部场强来达到降低束团头部能量的目的。实际数据表明,低电平系统前馈功能工作稳定,束流能散降低,束流的传输效率显著变高,克服了传统束流补偿法不能在大束团、高流强模式下工作的缺陷。

现场可编程逻辑门阵列,先进先出电路,串行转换,前馈控制,低电平,直线加速器

在 15MeV 直线加速器(Linear Accelerator,LINAC)中[1],束流负载效应使得直线加速器腔体中束团的头部能量变大,能散也变大,束流电流的传输效率变低[2]。传统的束流负载补偿的方法是在微波场尚未完全建立的时候提前注入束流,此时,束流负载效应造成的微波场的损耗可以通过微波场能量的提高而得到一定程度的弥补[3]。但是传统方法的局限性在于,对于电子束能散较高的情况下,不能做到完全清除大束团高流强模式下的束流负载效应[4-7]。

由于现代数字电子技术的发展,我们采用现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)数字算法的前馈控制来减少束流负载的影响[8]。前馈控制利用输入信号的直接作用构成开环控制系统,控制周期更短,并且只要输出量的较大波动量是可测和可控的,我们可以利用外扰动量直接控制输出,其补偿精度较传统方法有很大提升。本文使用的FPGA是Xilinx公司Virtex-6系列的X6-400M,在现有模块的基础上自行添加了前馈模块,将前馈数据叠加到原始射频场的波形数据中,实现对输入射频场波形的直接调控[9-10]。

1 加速器低电平系统简介

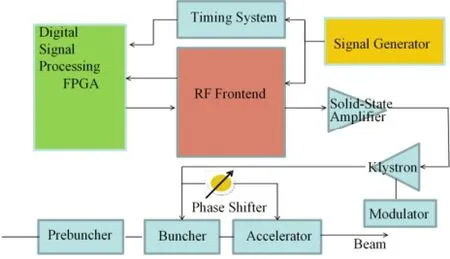

为了保证15MeV 电子加速器可以更好地驱动光中子源装置(TMSR Photo-Neutron Source Phase 1,TPNS1),我们开发了基于FPGA的数字化低电平控制系统。直线加速器和低电平系统一起构成直线加速器微波系统,如图1所示。其中低电平系统主要包括一个信号发生器、定时系统、射频(Radio Frequency, RF)前端和基于 FPGA的数字信号处理系统。在微波系统中前馈信号从FPGA中输出,经过数模转换(Digital to Analog Converter, DAC)成模拟信号并送到RF前端进行滤波,然后经过固态放大器和速调管放大到所需的功率,最后馈入到直线加速器的加速段中,从而实现对射频场波形和场强的直接调控。

图1 直线加速器微波系统Fig.1 Microwave system of electron LINAC.

2 FPGA数字前馈控制的设计

由束流负载理论可知,在束流注入时间固定的前提下,通过腔体的束团因束流负载效应造成的能量增益是一定的,所以前馈的数据可以设计为一系列时不变的值。我们将前馈数据写入到只读存储器(Read Only Memory, ROM)的初始化文件COE中,然后从底层ROM中直接将前馈数据引入到前馈模块中进行串行转换和叠加运算,最终得到调整后的射频场波形的数据。为达到这个目的,在FPGA分别设计了前馈数据生成模块和前馈模块两个部分。

2.1前馈模块的设计

前馈模块的主要作用是将 16位的前馈数据串行转换成64位,再将其与原波形的64位数据相叠加。前馈模块主要添加在原 FPGA顶层模块的ii_dac5682z_intf_top模块中,ii_dac5682z_intf_top原模块的结构如图2所示。

图2 ii_dac5682z_intf_top结构框图Fig.2 Block diagram of ii_dac5682z_intf_top.

在原模块中,上层数据经过VITA deframer模块解包后,经过一个二选一选择器,进入ii_offgain模块,该模块的作用是应用补偿误差和校正因子对采样数据进行优化,512×72的FIFO (First In First Out)(后改为512×64)主要起一个数据缓冲的作用。最后为了做到多卡同步,知识产权核(Intellectual Property Core, IP核)物理层(Physical Layer, PHY)使用ii_dac_lat_cal与ii_dac_bitslip模块校准输出定时来使得DAC的模拟输出对齐。

经过对ii_dac5682z_intf内各模块代码的解读,决定将前馈模块加在ii_offgain模块和512×64FIFO之间,如图3所示,发现ii_offgain模块的输出数据是16位的,而afifo输入端口是64位的,所以前馈模块必须要具备从16位到64位的串行转换的功能。此外,采用异步FIFO而不是双口随机存取存储器(Random-Access Memory, RAM)作为串行转换的桥梁。保证了串行转换的效率(经过仿真测试双口RAM输出数据的效率低于异步FIFO),并且FIFO作为一个具有存储功能的器件也让我们可以对上层来的前馈数据进行存储控制。

图3 添加前馈模块后ii_dac5682z_intf的结构图Fig.3 Block diagram of ii_dac5682z_intf module after adding feed-forward module.

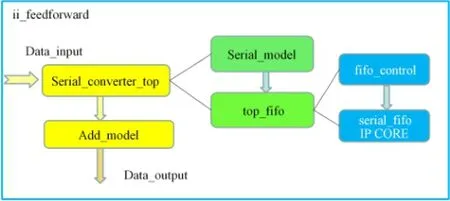

将设计的前馈模块命名为ii_feedforward,其内部构造如图4所示,主要由串行转换模块和前馈数据添加模块组成。其中串行转换模块又分为串行变换模块和FIFO模块,因为FIFO的IP核并不能直接使用,所以我们写了一个FIFO的控制程序和IP核一起封装成FIFO模块使用。模块设计好后用Isim对其进行仿真测试,结果如图5所示。

图4 ii_feedforward前馈模块的内部构造图Fig.4 Internal structure of ii_feedforward module.

图 5 Switch信号打开(a)和关闭(b)后各信号的仿真波形Fig.5 Simulation waveform after switch on (a) and switch off (b).

用switch信号作为前馈功能的开关,可以观察到 switch信号打开后(低变高),前馈模块开始工作,经过4个时钟周期的延迟,串行转换发生数据从16位变为64位,又经过一个时钟周期前馈数据添加到了原始数据之上。之所以前面会发生约5个时钟周期的延迟,是因为FIFO的数据写入过程需要5个时钟周期,详情参考X6-400M数据手册。

和开启时不同,一旦switch关闭,数据立马恢复成为原始数据。从仿真的结果来看,数据馈入的功能正常,但是后续试验表明仅做到这一步还不足以使得前馈功能正常工作,将在后面继续讨论。

2.2前馈数据输入模块的设计

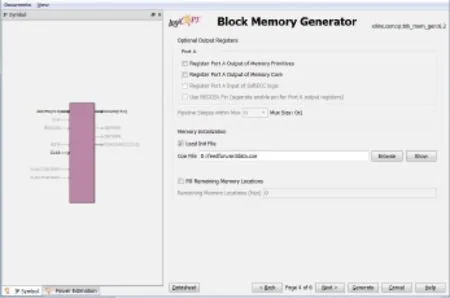

前馈数据是利用ROM的初始化文件COE,通过在COE中写入初始数据,并对其进行调用,来完成前馈数据的导出。该模块要达到的目的是,每当触发信号有效,就可以从ROM中输出想要的数据。要完成这个目的,需要对ROM的IP核进行设定。选择单口ROM,并根据数据的需求设定ROM的宽度和深度,图6在IP核中将事先写好的COE文件载入。COE文件里主要是一系列所需的大串数据,这些数据一般用MATLAB生成,写入到一个TXT文件中去,然后将 TXT文件里的格式保存为符合COE标准的格式即可生成COE文件。

图6 IP core中COE文件的载入界面Fig.6 Loading interface of COE file in IP core.

IP核生成后并不能直接使用,需要对它进行封装,操作方法类似之前的FIFO的IP核,并根据要求设计一个0-2047位的地址生成模块,为ROM的IP核分配地址。这样ROM里的初始化文件就能顺利导出了,图7为前馈数据生成模块的内部构造图。在第一次前馈功能测试中,在COE文件中一共写入了2048个前馈数据(因为前馈模块中FIFO的深度为2048),第0-500和1548-2047的数据值为0,第 501-700和 1301-1547的数据值为-5000,第701-900和 1101-1300的数据值为-8000,第901-1100的数据值最大,为-10000,体现在波形上是一个左右对称的阶梯状的凹陷。

图7 前馈数据生成模块内部构造图Fig.7 Internal structure of feed-forward data generation module.

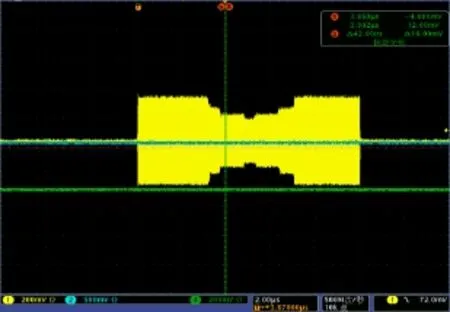

用信号发生器输入一系列正弦波到FPGA板卡中,并从512×64 FIFO中引出数据送到示波器中进行观察。没有前馈作用时,从图8中看到的是一整个矩形,它是由一系列同幅值的正弦波组成的。加入上文所说的前馈数据后,原本完整的矩形变成了图8中所示的情况,且其凹陷的幅度和前馈的设定值正好成比例,这一点再次说明前馈功能确实在正常工作。但是仅做到这些还不够,虽然得到了正确的波形,但是它并没有和预先试想的一样固定下来。随着串行转换的不断进行,波形是不断移动的,而我们施加到腔体射频场的前馈波形在没有人为调节的情况下必须是固定在我们需要的位置。为解决这个问题,专门设计一个特殊的触发信号来固定波形。

图8 从512×64 FIFO中引出的前馈数据的波形Fig.8 Feed-forward waveform take from 512×64 FIFO.

2.3触发信号的设计及优化

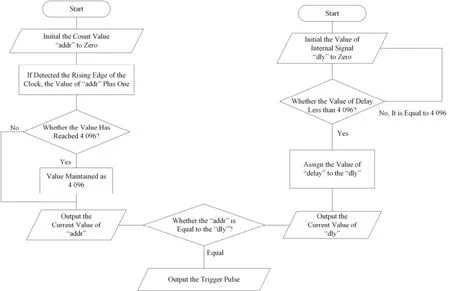

具体的程序设计思路如图9所示,其算法思想是一方面设计一个计数器,其中的计数信号(图 9 中 addr)在没有遇到外部触发的情况下让其从0-4096不断地增加,增长到4096后保持不变,有触发过来则将地址归零,重新计数;另一方面准备一个中间信号dly,在外部延迟delay没有到达4096时将外部的延迟值delay幅值给它,如果达到这个值就将其归零。简单来说两边都在各自进行循环计数的操作,然后在第三个process程序中将addr的值与外部延迟的值dly相比较,如果两者相等就让trig_o信号输出一个脉冲,前馈的波形只有检测到该脉冲后才能输出,这样就达到了固定波形的目的。

图9 触发信号程序的设计流程图Fig.9 Design flow chart of trigger signal.

除此之外,还对原ADC触发信号进行了优化。原 adc0_trigger信号高电平比较长,使得下一级模块对其进行检测带来了困难,为此设计了一路使得信号高电平部分变窄的程序。其功能如图10所示。

图10 对触发信号的优化Fig.10 Optimization of trigger signal.

根据VHDL编程的特点,只有在每个时钟的上升沿到来时赋值语句才会更新。而原 adc0_trigger高电平的长度等于好几个系统时钟周期。利用好这一点,我们设计了触发信号的优化程序。在程序中将a、b两者的值作为一个元素考虑,当触发没有到来时让a、b的值都为零,即(0,0)。当检测到原触发的上升沿时,将a的值赋为1,而将a之前的值0赋给 b即此时(a,b)为(1,0),之后的一小段时间里adc0_trigger始终处于高电平的状态,同样地很容易知道此时(a,b)为(1,1),当下降沿到来后再变为(0,1),最后变成(0,0)。在这个变化过程中,只有在(a,b)为(1,0)时,将信号c输出为高电平,这样就达到了使得触发信号变窄的目的。

完成了触发信号的设计及优化之后,再次进行前馈功能的测试,这一次波形依然满足要求(参考图8),其固定的位置满足前馈数据的数值分布而且没有移动,至此前馈模块的设计基本完成。

3 实际束团能量及电流波形的测量

为了验证前馈的真实有效性,直线加速器两个45°二极铁的中间安装了钇铝石榴石(Yttrium Aluminum Garnet, YAG)靶观察束团的能量分布[11]。因为靶的大小限制无法一次性看清整个束团的能量分布,通过调整二极铁电流强度来改变靶上观察到的束团中心能量,图11是15MeV电子直线加速器束流诊断系统的示意图。

图11 加速器束流诊断系统的示意图Fig.11 Beam diagnostics system of electron LINAC.

如图11所示,在加速器电子枪的后方、加速段的后方和经过偏转磁铁后的位置分别加装了积分式束流变压器(Integrating Current Transformer, ICT)去对该位置的束流积分电流进行测量[12]。由此,可以得到在该位置的束流电流的波形,进而对束流的传输效率进行初步分析。在图12中,最下面一条线表示的是刚从电子枪输出的束流电流波形,中间的线代表的是经过加速段后的束流电流波形,而最上面的线代表的是经过偏转磁铁后的电流波形。可以看见在未加前馈时,尽管从电子枪出射到经过加速管出来的电流的传输效率都很高,但是由于瞬态束流负载效应使得束团的头部能量大、能散高,在经过偏转磁铁时束团头部较长打在外侧真空壁上,而造成最终输出的电流值有很大一部分的损失。

图12 添加前馈前(a)和添加前馈后(b)三个ICT所测得的束流电流的波形Fig.12 Integral beam current waveform before (a) and after (b)feed-forward function turned on.

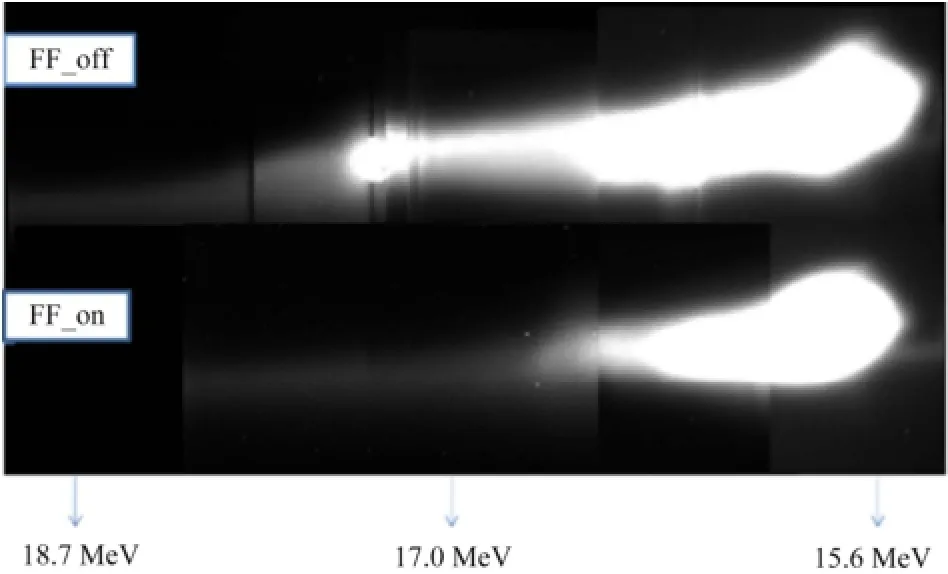

为了削减束团的头部能量,采用前馈的方法衰减射频场前端的场强幅值。考虑到实际情况,将前馈表的值设计为512个-5000和1536个0,一共2048个数的阶梯样式(前馈表的大小由前馈模块中存储器的深度决定),再辅以RF调试(适当调节波形的相位和前馈的延迟,使前馈凹陷对应在射频场前端),将射频场的输入波形完成从左边向右边的转换。之后可以看到经过偏转磁铁后束流的传输效率有了大幅度的提升。在此基础上,我们还测量了在前后两种状态下束团能量的分布,如图13所示。

图13 两种状态下束团能量的测量Fig.13 Beam energy measurement before and after the feed-forward function turned on.

在图13中,可以清楚地看到未添加前馈时束团头部的能量很高,一直延伸到了18.7MeV,且能散很高。添加前馈后,束团头部的能量(18.7-17.0MeV)明显降低,能散减少。图12、13的结果证明前馈功能工作正常,束团头部能量得到很好的削减,从中间的线到最上面线的电流传输效率已经接近理想值,工作状态稳定,至此前馈控制的目的基本完成。

4 结语

利用数字低电平前馈技术,在电子加速器低电平控制系统的FPGA中设计了前馈模块。该模块以FIFO作为串行转换的桥梁,通过将前馈的波形数据叠加到原始射频场的波形数据之上,来削减射频场头部的场强,让经过腔体的束团的头部能量减少,解决了束流经过腔体时因束流负载效应而造成的一系列问题。实验结果表明,前馈模块工作良好,束团能散减小,束流电流传输效率明显上升。

1王宏伟, 陈金根, 蔡翔舟, 等. 电子直线加速器驱动的光中子源装置的研制[J]. 核技术, 2014, 37(10):100522. DOI:10.11889/j.0253-3219.2014.hjs.37.100522

WANG Hongwei, CHEN Jingen, CAI Xiangzhou, et al. Development of photo-neutron driven by electron LINAC[J]. Nuclear Techniques, 2014, 37(10):100522. DOI:10.11889/j.0253-3219.2014.hjs.37.100522

2Yuan Y S, Li K W, Wang N, et al. Study of the beam loading effect in the CSNS/RCS[J]. Chinese Physics C,2015, 39(4):047003. DOI:10.1088/1674-1137/39/4/ 047003

3Li D Z, Wang Y S, Li Y G, et al. Beam-loading compensation for RF gun by feed-forward control system[J]. International Journal of Infrared and Millimeter Waves, 2001, 22(8):1163-1166

4Kim S H, Yang H R, Son Y G, et al. Transient beam loadingcompensationinL-bandtraveling-wave accelerating structure with intense electron beam[C]. Proceedings of Linear Accelerator Conference, Tsukuba,Japan, 2010:133-135

5Masunov E S, Polozov S M, Rashchikov V I, et al. Beam loading effect simulation in Linacs[C]. Proceedings of HB2010, Morschach, Switzerland, 2010:123-125

6Leiss J E. Beam loading in linear accelerators[C]. Proceeding of National Particle Accelerator Conference,Washington D C, USA, 1965:566-579

7MacLachlan J A, Mills F E, Owens T. Feed-forward compensation for transient beam loading of the 805 MHz debuncher for the fermilab linac upgrade[C]. Proceedings of the Linear Accelerator Conference, Albuquerque, New Mexico, USA, 1990:303-305

8赵玉彬. 高频低电平控制和高频直接反馈[D]. 上海:中国科学院上海应用物理研究所, 2008

ZHAO Yubin. A dissertation submitted in partial satisfaction of the requirements[D]. Shanghai:Shanghai Institute of Applied Physics, Chinese Academy of Sciences, 2008

9陈刚, 张京, 唐建, 等. 一种基于FPGA的PCIe总线及其 DMA的设计方法[J]. 兵工自动化, 2014, 33(5):75-77

CHEN Gang, ZHANG Jing, TANG Jian, et al. A design of PCIe bus and DMA based on FPGA[J]. Ordnance Industry Automation, 2014, 33(5):75-77

10Tamura F, Schnase A, Nomura M, et al. Development of the feedforward system for beam loading compensation in the J-PARC RCS[C]. Proceedings of EPAC 2006,Edinburgh, Scotland, 2006:1319-1321

11 徐慧超, 周建英, 龚培荣, 等. YAG晶体在软X射线荧光靶探测器中的应用[J]. 核技术, 2012, 35(8):587-590

XU Huichao, ZHOU Jianying, GONG Peirong, et al. Application of Ce:YAG as fluorescence screen BPM for soft X-ray beamline at SSRF[J]. Nuclear Techniques,2012, 35(8):587-590

12 薛磊. 基于ICT的加速器束团电荷量监测系统设计[D].北京:清华大学, 2007

XUE Lei. Charge monitor system with ICT for accelerator bunch[D]. Beijing:Tsinghua University, 2007

Implementation of FPGA-based feedforward function in LLRF system for electron LINAC

LI Song1,2ZHANG Junqiang1ZHANG Meng1ZHAO Minghua1

1(Shanghai Institute of Applied Physics, Chinese Academy of Sciences, Jiading Campus, Shanghai 201800, China)

2(University of Chinese Academy of Sciences, Beijing 100049, China)

Background: Due to the existence of transient beam loading effect in cavity, the energy of the bunch head is higher than the other part in 15-MeV linear accelerator (LINAC) designed for thorium molten salt reactor (TMSR)photo-neutron source. This uneven distribution of energy leads to high energy spread, thus depresses transmission efficiency of beam. Purpose: This study aims to develop a digital feedforward compensation to reduce the influence of beam loading effect and decrease energy spread of the beam. Methods: The Field Programmable Gate Array (FPGA) programming language VHDL (Very-High-Speed Integrated Circuit Hardware Description Language) was used to design the feedforward module. This module was added to the original FPGA modules of low level radio frequency (LLRF) control system to cut down the intensity of head of radio frequency (RF) field. Results: The experimental test shows that the feedforward function of LLRF control system suppressed the energy spread to an ideal level and the transmission efficiency of the beam current had also been significantly improved. Conclusion: The digital feedforward method overcomes the deflection of traditional beam compensation method which malfunctions in the situation of big bunch and high beam current.

FPGA, First in first out (FIFO), Serial conversion, Feed-forward control, Low-level radio frequency,LINAC

LI Song, male, born in 1989, graduated from Yangtze University in 2013, master student, focusing on the design and upgrade of low-level radio frequency control system of LINAC

TL53

10.11889/j.0253-3219.2016.hjs.39.070402

中国科学院战略性先导科技专项(No.XDA02010100)资助

李松,男,1989年出生,2013年毕业于长江大学,现为硕士研究生,研究领域为加速器低电平控制系统的设计与升级

赵明华,E-mail:zhaominghua@sinap.ac.cn

Supported by Strategic Pilot Science and Technology Project of Chinese Academy of Sciences (No.XDA02010100)

ZHAO Minghua, E-mail:zhaominghua@sinap.ac.cn

2016-01-28,

2016-03-02