基于USB和FPFA的四通道数据采集卡的设计

武 刚,杨 录,张艳花

(中北大学 信息与通信工程学院 电子测试技术国家重点实验室,山西 太原 030051)

基于USB和FPFA的四通道数据采集卡的设计

武刚,杨录,张艳花

(中北大学 信息与通信工程学院 电子测试技术国家重点实验室,山西 太原 030051)

摘要:针对传统PCI卡或ISA卡安装复杂、价格昂贵、可扩展性差的缺点,设计了一套基于FPGA和USB2.0的便携式高速数据采集系统。该系统使用异步并行的A/D转换技术实现40 Mbps的采样速率。文章给出了硬件的基本结构和软件固件的设计方法,并对整套系统FPGA时序控制作了重点阐述。该数据采集卡采用SlaveFIFO模式进行数据传输,实验证明该采集系统性能稳定、通用性,特别适用于移动的作业现场。

关键词:数据采集卡;USB2.0;采样速率;固件设计

信息与信号处理技术的水平决定了社会发展的方向,数据采集是数字信号处理的关键,在数字系统中起着决定性的作用。随着实时信号处理、数字图像处理等领域对高速、高精度的数据采集卡的需求日益增大[1],对A/D转换、主控CPU以及CPU与主计算机的接口的工作性能要求也越来越高。相对于传统的MCU,FPGA以其时钟频率高、内部延时小、组成形式灵活等特点在高速数据采集方面具有不可比拟的优势。现在通用的高性能数据采集卡一般采用PCI卡或ISA卡,这些采集卡存在不少缺点,如安装复杂、价格昂贵,受计算机插槽数量、地址、中断资源的限制,可扩展性差[2],容易受PC机箱内高频信号的干扰等缺点。而通用串行总线(USB)的出现则很好的解决了以上问题,它使高传输速度、简易扩展性、方便的即插即用等特点有机结合在一起,使得计算机外围设备的连接更具单一化[3]。本文设计了一款基于FPGA和USB的高速数据采集卡,它既能实现采集卡与PC机的方便连接,又能保证较高的传输速率和合适的性价比[4]。

1数据采集和传输系统方案设计

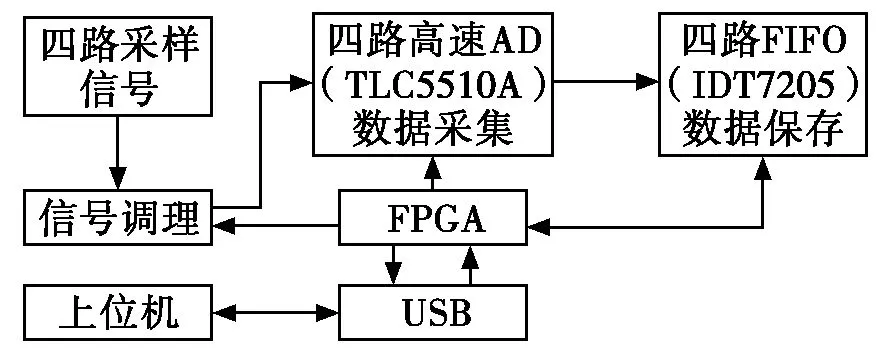

多通道数据采集通常有两种实现方案,可采用多路复用器实现多通道的通道切换,也可以采用多片AD采集芯片对多路信号同时进行采集。而采用多路复用器实现数据采集存在着通道之间串扰的缺点,因此本设计通过四片AD转换器来实现四通道的数据采集来克服以上缺点。本数据采集卡由信号调理模块、高速数据采集模块、FPGA核心控制模块、数据缓冲模块和USB数据传输模块五部分组成。系统结构框图如图1所示。

图1 数据采集与控制框图

系统以FPGA为控制核心来完成四路信号的采集。其外围器件有AD采集芯片TLC5510、数模转换芯片TLC5620、数据存储芯片IDT7205及USB通信芯片CY7C68013A。

信号调理电路由数模转换芯片TLC5620、自动增益控制芯片VCA810和运放AD9618组成,主要作用是向后级提供合适动态范围的信号,通过FPGA控制TLC5620产生合适的电压来控制VCA810的增益,从而达到调理信号的目的。

AD转换器将所要采集的模拟信号转换成数字信号,通过滤波后由FPGA接收、缓存、发送,本系统高速AD转换器的转换率为40 M。

CY7C68013A是cypress公司推出的EZ-USB FX2系列智能USB接口芯片,它其实是一个能和计算机连接的数据端口[5],其作用是将主机所发送的命令序列经USB2.0端口输出,实现对数据采集系统的控制;同时把AD转换器采集的数据以高速的数据序列形式发送到主机。

采集卡工作流程为:PC机通过CY7368013A给数据采集系统下发若干采样控制命令(数据采样深度、开始、停止等),存入FPGA寄存器中,FPGA根据这些命令向AD转换器发出相应控制信号。由于AD采样速度为40 M,为了和USB数据传输速度(20 M)、PC机运行速度相匹配,本设计将AD转换的数字信号存入硬件FIFO缓冲器中,防止数据溢出或丢失。AD转换器在FPGA采样时钟的控制下,把模拟信号转换为数字信号,并将指定通道的数据存入相应的FIFO中,同时查询USB是否空闲,若USB空闲, FPGA的USB接口控制逻辑将指定通道的采样结果,由硬件FIFO送入到USB内部FIFO中。由于固件程序把CY7C68013A设置为自动数据批量传输模式,当USB内部FIFO容量达到固件设置的值时,数据将自动打包上传,无需CY7C68013A中的CPU参与[6],从而保证足够的数据传输速率。采样过程中,PC机依次取走批量数据。本系统设计的四通道采集卡可实现对开始采样时间的控制,实现对采样点数控制,包括1 K、2 K、4 K、8 K的采样深度,也可实现单次采样和连续采样并对其进行存储。

2FPGA数据采集与控制时序框图

开始采样时,PC机通过CY7368013A向数据采集系统下发若干采样控制命令(如数据采样深度、开始、采样延时等),存入FPGA寄存器中,FPGA通过解析这些命令完成相应的时序控制。FPGA接收到开始采样命令后就产生FS触发信号(本采集卡针对实验室超声信号采集设计,因此有超声激发信号FS),经过延时模块延时指定的时间,产生4路40 M频率的时钟采样信号ADCCLK分别控制四路AD采集,同时使能硬件FIFO的写信号Write-FIFO,保证采集的数据实时、有效的存入FIFO中。当完成8K的采集深度(产生8 192个采样时钟)后,系统关闭AD采样时钟ADCCLK信号和FIFO写使能信号Write-FIFO,同时查询USB是否空闲,若USB空闲则使能FIFO读信号Read-FIFO和USB2.0写信号Write-USB,从四个通道硬件FIFO中分别读取512个数据(固件程序将USB内部FIFO设置为2 K)写入USB内部FIFO中。之后数据通过USB自动打包上传到PC机,这样一次数据传输就完成。每个通道传输512个数据,根据解析PC机每通道的采样深度,周期性的使能FIFO读信号Read-FIFO和USB2.0写信号Write-USB,就可以完成要求的数据采样深度。FPGA具体时序控制关系如图2所示。

图2 FPGA数据采集与控制时序框图

3USB2.0固件程序

CY7C68013A是CYPRESS公司开发的第一款集成USB2.0协议的微处理器,包括USB2.0收发器、串行引擎(ISE)、增强型8051内核、16 KB的RAM、4 KB的FIFO存储器、IO接口、数据总线、地址总线、通用可编程接口。在USB协议中定义了4种USB传输类型:控制传输(control)、块传输(bulk)、中断传输(interrupt)和同步传输(isochronous)。这4种传输类型在传输数据量的大小、传输速率的高低以及同步要求有各自的特点[7]。因此,我们在使用USB协议进行数据传输时,必须通过编写USB固件控制USB2.0的传输方式。本采集卡将USB2.0协议设置为块传输,采用SlaveFIFO传输模式,USB内部FIFO设置为四缓冲,缓冲区大小为512字节。主要固件程序如下:

void TD_Init( void )

{

CPUCS = 0x10;

OEA |= 0x03;

SYNCDELAY;

IOA &= 0xFC;

SYNCDELAY;

PINFLAGSAB = 0xE8;

SYNCDELAY;

EP2CFG = 0xA0;

SYNCDELAY;

EP6CFG = 0xE0;

SYNCDELAY;

EP4CFG = 0x02;

SYNCDELAY;

EP8CFG &= 0x02;

SYNCDELAY;

FIFORESET = 0x80;

SYNCDELAY;

FIFORESET = 0x02;

SYNCDELAY;

FIFORESET = 0x04;

SYNCDELAY;

FIFORESET = 0x06;

SYNCDELAY;

FIFORESET = 0x08;

SYNCDELAY;

FIFORESET = 0x00;

SYNCDELAY;

EP2FIFOCFG = 0x00;

SYNCDELAY;

EP2FIFOCFG = 0x10;

SYNCDELAY;

EP6FIFOCFG = 0x0C;

SYNCDELAY;

IFCONFIG = 0x03;

SYNCDELAY;

}

4系统软件设计

系统软件设计流程图如图3所示。

图3 软件设计流程图

开始采样前上位机将采样延时、采样深度、采样方式通过USB2.0传入FPGA控制中心,下位机解析这些命令并选择执行相应的模块,当接收到启动采样命令时,各通道就开始采集、存储数据。当USB空闲时就与PC机进行数据传输,上位机接收到各通道数据后,就绘制各通道波形。图4为采样深度为2 K、采样延时为0us时绘制的波形,其中,通道A信号频率为1 MHz的正弦波,峰峰值为0 V~4 V,通道B为参考地0 V电平,通道C信号频率为500 kHz的正弦波,峰峰值为0 V~4 V,通道D为采集信号悬空时的状态。

5结束语

本文设计了一张基于USB2.0数据传输的四通道数据采集卡,与传统采集卡相比,它既可以进行40 Mbps的高速数

据采集,又可以同时采集四个通道的数据,而且与计算机连接方便,适合户外作业,通过实验证明本采集卡性能稳定,误码率低、通用性强。

图4 上位机绘制波形

[1]高冰.基于FPGA与USB2.0的便携式数据采集系统的设计[J].电子科技大学学报,2010(39):61-64.

[2]梁颖,游磊,匡顺兰,等.基于USB接口数据采集卡的设计与实现[J].计算机测量与控制,2005(4):392-395.

[3]陈辉,李远.基于USB2.0的数据采集卡[J].自动化技术与应用,2008(6):91-94.

[4]沈维聪,陈东龙.基于FPGA软核的高速数据采集系统设计[J].微型机与应用,2011(7):25-28.

[5]李露,段新文.基于FPGA的高速数据采集卡的设计[J].现代电子技术,2012(18):146-148.

[6]黄大勇.基于USB2.0接口的高速数据采集系统的设计[J].现代电子技术,2007(24):69-72.

[7]何光祖.基于USB2.0的多通道超声检测系统[D].太原:中北大学,2013.

收稿日期:2015-12-15

作者简介:武刚(1987- ),男,山西原平人,硕士研究生,主要从事超声检测和信号处理方面的研究。

文章编号:1674- 4578(2016)02- 0021- 03

中图分类号:TP274

文献标识码:A

Design of Four-channel Data Acquisition Card Based on USB and FPGA

Wu Gang, Yang Lu, Zhang Yanhua

(CollegeofInformationandCommunicationEngineering,NorthUniversityofChina,TaiyuanShanxi030051,China)

Abstract:For the complex, expensive, poor scalability drawbacks in installation of PCI or ISA card, the paper designs a portable high-speed data acquisition system based on FPGA and USB2.0. The system uses an asynchronous parallel A/D converter technology to achieve sampling rates of 40 Mbps. This paper presents the basic structure of the hardware and the design method of software firmware, and focuses on the FPGA timing control of entire system. The data acquisition card uses SlaveFIFO mode for data transmission. Experiments show that the acquisition system performance is stable, versatile, especially for moving job site.

Key words:data acquisition card; USB2.0; sampling rate; firmware design