基于FPGA的精密光栅尺图像采集与预处理设计

蔡铁根, 黄明辉, 李成祥, 杨志军

(广东工业大学 机电工程学院,广东 广州 510006)

基于FPGA的精密光栅尺图像采集与预处理设计

蔡铁根, 黄明辉, 李成祥, 杨志军

(广东工业大学 机电工程学院,广东 广州 510006)

摘要:针对目前利用图像的方法来分析精密光栅尺位移采集速度不高的问题,设计了一种以现场可编程门阵列(Field Programmable Gate Array, FPGA)为主控器件对光栅尺进行图像编解码和预处理的系统.系统主要包括SDRAM控制模块、CMOS传感器驱动模块、VGA显示模块以及图像算法模块.整个模块以Altera公司的Cyclone IV系列EP4CE10E22C8N作为主控芯片,Quartus II 15.0软件为开发平台,并经过反复测试实现各个模块功能,最终通过VGA实时显示预处理后的图像,为下一步DSP实现光栅尺位移的测量提供了可靠的预处理数据.

关键词:FPGA; 光栅尺; 图像采集; 图像预处理

目前的机械制造业在涉及到高速高精密的位移测量场合中,大多数采用光栅尺作为位移反馈装置[1-4].光栅是目前应用最广泛的栅式传感器,精度高,但仍有一些缺点,其根本原因在于栅线数难以提高,只能依靠电子细分,从而导致成本、可靠性、抗干扰能力等方面的问题[5].一方面,光栅尺在一定的刻线密度情况下,想要提高分辨力就必须依靠复杂的电子细分,除结构复杂技术封锁外,还对光栅的运动附加了限制,要求运行平稳、相对低速等,可靠性降低;另一方面,如果想提高刻线密度,除工艺变得复杂、成本提高外,还更容易受到生产现场微小粉尘、油污等的污染,抗干扰能力降低[6].针对上述光栅尺存在的问题,文献[6]提出了一种空间均匀分布、时序相互错开的CCD匀速扫描的测量方式,设计了一种基于线阵CCD的静态光场式时栅传感器,文献[7]中提出了一种单道编码方法,采用CCD线阵电荷耦合细分的直线编码器.但是以上方法在高精度测量以及实时性处理方面还不能满足要求.由于光栅尺编码图像的编解码过程是决定光栅尺测量效率的决定因素,高速采集到的图像经过数据总线传输进入后台处理,此类数据中包含了大量的位置信息,必须经过快速、可靠的处理才能得到需要的结果,所以对图像采集的实时性提出了一定的要求.本文针对图像采集的实时性,采用现场可编程门阵列FPGA进行图像的编解码,利用FPGA的并行处理特性实现硬件加速,并通过图像算法得到了更优的图像.

1图像采集硬件系统框图

图像采集的整个系统结构框图如图1所示.图中光栅尺选用的是增量式,栅距为20 μm,为了达到精确细分,必须经过光学放大系统对光栅条纹进行放大,这里采用金相物镜,放大倍数为20倍.整个系统是以Altera FPGA为主控元件,通过SCCB总线协议驱动CMOS传感器去捕获放大后的条纹并进行图像处理,处理后的数据送给SDRAM.FPGA通过仲裁模块对SDRAM进行初始化、读写、刷新等操作,SDRAM将图像处理后的数据再送给VGA,进行图像的实时显示.VGA部分采用视频专用芯片ADV7123[8],将SDRAM传送的数据转换为模拟信号输出到显示设备,得到最终的光栅尺条纹图像.

图1 系统结构框图

2图像采集软件模块设计

2.1摄像头驱动及图像捕获模块

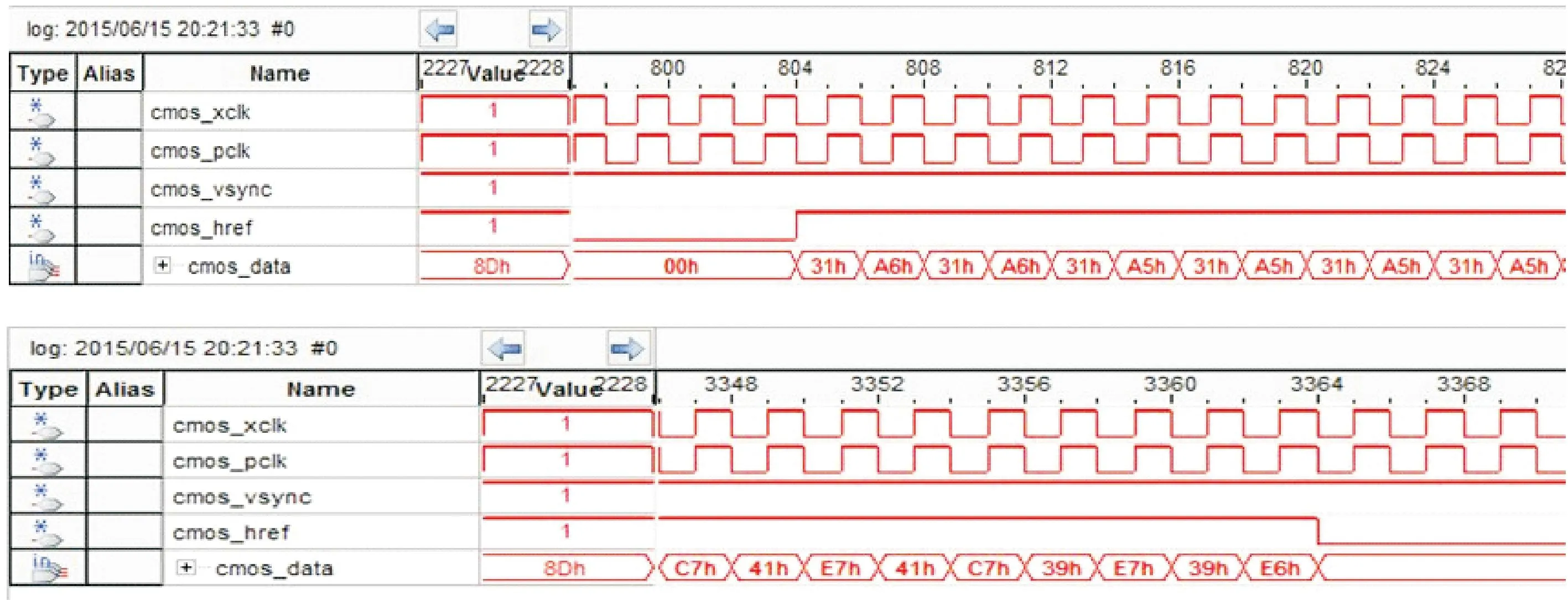

文中所使用CMOS传感器的驱动遵循SCCB协议,需要在FPGA中模拟出SCCB协议并对传感器的寄存器进行初始化配置[9],配置的方式主要是通过FPGA对传感器进行地址和寄存器值的读写.图2是SCCB总线寄存器的写入时序,在第1阶段是写入设备地址,第2阶段写入寄存器地址,第3阶段写入寄存器的值,完成寄存器的写入配置.图3为SCCB总线寄存器的读取时序,第1阶段写入CMOS Sensor的唯一ID地址,ID为0x42; 第2阶段写入需要读取的寄存器地址; 第3阶段读取CMOS Sensor的唯一ID地址,ID为0x43; 第4阶段读取CMOS Sensor发送的指定寄存器的值.通过FPGA对传感器的寄存器配置后,需要将所获得的数据送给图像捕获模块.利用signal tap II抓取捕获后的图像数据如图4所示,当行信号为高电平时开始捕获数据,期间场信号保持高电平.

图2 寄存器写入时序

图3寄存器读取时序

Fig.3Register of reading timing

图4 捕获后的视频数据

2.2图像处理模块

2.2.1图像灰度化处理

系统中FPGA驱动CMOS传感器所输出的视频格式为RGB,由于RGB格式数据量大且光栅条纹是亮暗相间的,只需提取亮度信息就能分辨条纹.为了提高处理数据的实时性,减少数据量传输且增加检测精度,需将视频RGB格式转换成YCbCr格式[10-11],方便FPGA对数据进行实时处理[12],转换公式为

Y=0.299R+0.587G+0.114B,

(1)

Cb=-0.172R-0.339G+0.511B+128,

(2)

Cr=0.511R-0.428G-0.083B+128.

(3)

以上是理论上的变换公式,若是直接在FPGA上面进行处理,会消耗大量FPGA逻辑单元,同时也不能保证对数据进行快速实时处理,所以需要对上述公式进行变换,分别对式⑴、⑵、⑶进行放大256倍然后再右移8位的方式来操作,具体变换公式为

Y=((77R+150G+29B)≫8),

(4)

Cb=((-43R-85G+128B)≫8)+128,

(5)

Cr=((128R-107G-21B)≫8)+128.

(6)

由于视频格式YCbCr中的Y代表图像的亮度

分量,Cb和Cr分别代表色彩和饱和度,所以在数据输出时只输出Y通道的数据即可.

2.2.2中值滤波处理

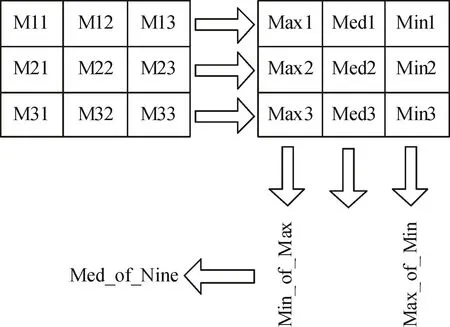

在图像采集和处理过程中会带入各种噪声,而且传感器本身也会产生一定的噪声影响,所以必须对采集后的图像进行降噪处理[13-14].中值滤波处理的结构框图如图5所示,先求出每一行的最大值、中值、最小值,然后再对每一列最大值中求出最小值,在中值中求出中值,在最小值中求出最大值,图6是利用modelsim进行仿真后的中值滤波结果.

图5 中值滤波框图

图6 仿真后的结果

2.3SDRAM仲裁模块

传感器捕获后的数据为640像素×480像素,每个数据单元占用16 bit,那么摄像头传送的数据是将近30万个16 bit,为达到最大数据流的传送,设置SDRAM为顺序读/写模式,同时以全页读/写的方式进行突发读/写操作,并采用SDRAM内部乒乓机制,实现最大视频流的传送,图7为SDRAM模块结构框架.为了保持时钟的全局性,采用外部PLL来生成SDRAM驱动时钟和SDRAM控制时钟,其中两个时钟均为100 MHz,相位差在-3 ns~+1 ns之间.由于数据读入与数据读出来自两个不同的时钟域,RD_FIFO读模块和WR_FIFO写模块用来作为跨时钟域数据缓存模块.SDRAM逻辑控制模块中,实现乒乓操作,达到最大数据流传送.SDRAM命令接口和控制接口在外部PLL的控制下,完成SDRAM初始化、预充电、读写控制,以及刷新等操作,最后将数据送给VGA显示模块[15-17].

2.4VGA控制模块

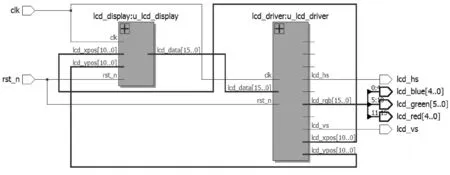

经光学放大系统后采集到的图像,需要实时观

察采集到的条纹是否有失真现象,所以系统采用专用视频编码芯片ADV7123,其能够将图像数据转换成模拟信号,并且最大限度地还原原始信号.所设计的测试ADV7123模块的RTL视图如图8所示.

图7 SDRAM模块结构框图

图8 ADV7123测试模块

3系统调试与验证

整个精密光栅尺图像采集系统如图9所示,增量式光栅尺固定在支架上,数据采集卡主控芯片采用Altera公司的Cyclone IV系列EP4CE10E22C8N,并搭载Quartus II 15.0软件开发平台进行程序的编写,配备金相物镜及CMOS传感器对光栅尺条纹进行放大及图像处理,在直线电机运动控制平台的驱动下,随着镜头的缓慢移动,能保持图像清晰可见、不失真.

图9 光栅图像采集实验平台

4结论

本文以增量式光栅尺作为图像采集对象,以提高图像采集的实时性为前提,设计了精密光栅尺图像采集系统,并对图像进行预处理.文中对系统各个模块的设计与原理进行了详细的说明,并在FPGA上进行实现,得到了放大后的清晰图像.文中的设计方法具有一定的通用性,易于实现,为下一步DSP实施精确位置距离算法方案提供了准确的数据.

参考文献:

[1] KIMURA A, GAO W, KIM W, et al. A sub-nanometric three-axis surface encoder with short-period planar gratings for stage motion measurement[J]. Precision Engineering. 2012, 36(4): 576-585.

[2] SHINNO H, YOSHIOKA H, GOKAN T.A newly developed three-dimensional profile scanner with nanometer spatial resolution[J].CIRP Annals-Manufacturing Technology, 2010, 1(59):525-528.

[3] BUICE E S, OTTEN D, YANG R H. Design evaluation of a single-axis precision controlled positioning stage[J].Precision Engineering, 2010, 4(33):418-424.

[4] LIU C H, JYWE W Y, JENG Y R. Design and control of a long-traveling nano-positioning stage[J].Precision Engineering, 2010, 3(34):497-506.

[5] 彭东林.时栅位移传感器与新型机床动态检测系统[M].北京:科学出版社, 2010.

[6] 付敏.新型光场式时栅位移传感器原理与实验研究[D].重庆:重庆大学机械工程学院, 2014.

[7] 郑洪. 单道编码CCD细分直线编码器的研究[J]. 中国机械工程, 2003,31(3): 21-23.

ZHENG H. Study on single-channel coding CCD linear encoder segments[J]. China Mechanical Engineering, 2003,31(3): 21-23.

[8] 邓春健,王琦,徐秀知,等.基于FPGA和ADV7123的VGA显示接口的设计和应用[J].电子器件,2006,4(29):1325-1328.

DENG C J, WANG Q, XU X Z, et al. Design and application of VGA display interface based on FPGA and ADV7123[J].Chinese Journal of Electron Devices, 2006,4(29):1325-1328.

[9] 应小军,李瑜煜.基于FPGA的CMOS图像传感器驱动电路设计[J].广东工业大学学报, 2015, 32(1):71-74.

YING X J, LI Y Y. Design of drive circuit of CMOS image sensor based on FPGA[J]. Journal of Guangdong University of Technology, 2015, 32(1):71-74.

[10] 向方明,朱遵义,许敬,等. YUV到RGB颜色空间转换算法研究[J].现代电子技术, 2012, 35(22):65-68.

XIANG F M, ZHU Z Y, XU J, et al. Research on algorithms of color space conversion from YUV to RGB[J]. Modern Electronics Technique, 2012, 35(22):65-68.

[11] 宋冠群,段哲民,冯飞.基于FPGA的色度空间转换设计[J].电子测量技术, 2007, 30(1):178-180.

SONG G Q, DUAN Z M, FENG F. Design of color space transform based on FPGA[J]. Electronic Measurement Technology, 2007, 30(1):178-180.

[12] 金晓冬,常青.基于FPGA的RGB到YCbCr色空间转换[J].现代电子技术, 2009,16(18):73-75.

JIN X D, CHANG Q. RGB to YCbCr color space transform based on FPGA[J]. Modern Electronics Technique, 2009,16(18):73-75.

[13] 杨晶,王元庆.实时高速实现改进型中值滤波算法[J].计算机与现代化, 2013,20(8):30-32.

YANG J, WANG Y Q. Implementation of improved median filter algorithm in real-time and high-speed[J]. Computer and Modernization, 2013(8):30-32.

[14] 李飞飞,刘伟宁,王艳华.改进的中值滤波算法及其FPGA快速实现[J].计算机工程, 2009, 35(14):175-177.

LI F F, LIU W N, WANG Y H. Improved median filtering algorithm and its fast implementation in FPGA[J]. Computer Engineering, 2009, 35(14):175-177.

[15] 丁昊杰,刘敬彪,盛庆华.基于CMOS图像传感器的视频采集系统设计[J]. 现代电子技术. 2012, 35(14): 178-181.

DING H J, LIU J B, SHENG Q H. Design of video acquisition system based on CMOS image sensor[J]. Modern Electronics Technique. 2012, 35(14): 178-181.

[16] 邓兴汉,杨恢东.基于FPGA的视频图像采集系统的设计与实现[J]. 微计算机信息. 2010, 26(32): 138-139.

DENG X H, YANG H D. Design and implementation of a video image acquisition module based on FPGA[J]. Control & Automation. 2010, 26(32): 138-139.

[17] 杜玉晓,张浩腾,陈汶育,等.基于FPGA的高速多通道实时同步采集传输系统的设计与实现[J].广东工业大学学报, 2013, 30(3):37-44.

DU Y X, ZHANG H T, CHEN W Y, et al. The design and implementation of high-speed multi-channel and real-time synchronous acquisition transmission system based on FPGA[J]. Journal of Guangdong University of Technology, 2013, 30(3):37-44.

Design of Image Acquisition and Preprocessing of Precise Linear Encoder Based on FPGA

Cai Tie-gen, Huang Ming-hui, Li Cheng-xiang, Yang Zhi-jun

(School of Electromechanical Engineering, Guangdong University of Technology, Guangzhou 510006, China)

Abstract:According to the method of image acquisition for analyzing precision linear encoder displacement with the problem of low acquisition speed, an image and pre-processing system of encoding and decoding is designed in which FPGA is the core device. All modules are accomplished by taking Altera’s Cyclone IV series EP4CE10E22C8N as the main control chip, designed on Quartus II 15.0 which is software development platform. Each module has repeating tests to accomplish the function. The result is real-time displayed on VGA monitor and provides a reliable pretreatment data for next DSP realization of linear encoder displacement measurement.

Key words:field programmable gate array(FPGA); linear encoder; image acquisition; image pre-processing

收稿日期:2015- 06- 17

基金项目:广东省自然科学基金资助项目(408224931073)

作者简介:蔡铁根(1991-),男,硕士研究生,主要研究方向为视频图像处理.通信作者: 杨志军(1977-),男,教授,主要研究方向为机械系统动力学建模仿真与优化、界面动力学、微流固耦合建模. E-mail:yangzj@gdut.edu.cn

doi:10.3969/j.issn.1007- 7162.2016.03.011

中图分类号:TP212

文献标志码:A

文章编号:1007-7162(2016)03- 0060- 05