基于FPGA射频接收机前端AGC系统电路的设计

李 飚,刘春群,黄忠快

(百色学院 信息工程学院,广西 百色 533000)

基于FPGA射频接收机前端AGC系统电路的设计

李飚,刘春群,黄忠快

(百色学院 信息工程学院,广西 百色 533000)

摘要:基于FPGA设计了一射频接收机前端AGC系统电路。根据AGC系统电路工作和控制原理,讨论了系统设计的难点和设计方案,选取了ADL5330、A/D转换器AD5760、Xilinx virtex-6、D/A转换器DAC8760等芯片搭建设计了系统硬件电路。测试结果表明系统电路在900~990 MHz及60 dB输入动态范围内,输出信号功率能够保持在-16.5 dBm附近,且输出功率可调。系统硬件电路具有体积轻小、高灵敏度和稳定性。

关键词:接收机;AGC系统;动态范围;信号功率

0引言

电子系统一般只能处理幅度变化不大的信号,信号过大会造成系统过载,过小又会造成有用信号的丢失,所以,在接收系统中一般要设置AGC系统电路,以使接收机的输出信号保持平稳,使后继设备能正常工作[1]。对于大宽带和高频情况,高性能全数字的AGC系统设计还比较难,基于FPGA仅对AGC系统电路的控制环路进行了数字化设计。

1AGC系统控制原理

1.1基本原理

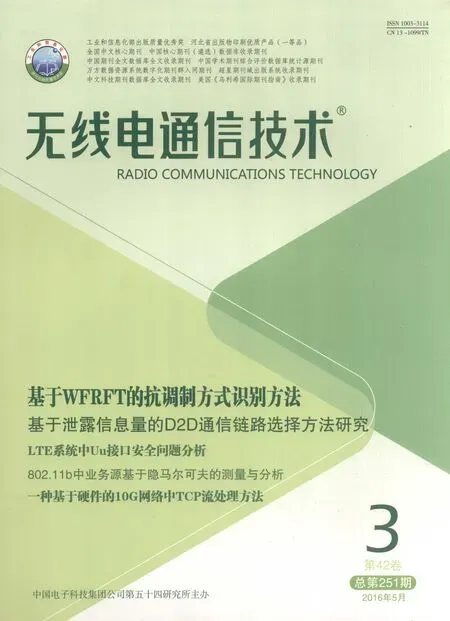

无线通信接收机系统中,AGC系统的结构大都采用闭环延迟式[2],其电路原理框图如图1所示的形式。

图1 闭环延迟式结构AGC系统

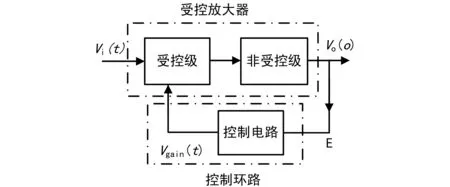

系统可分为控制环路和受控放大器两大模块。图2为延迟式结构AGC系统的静态调节特性示意图。当AGC系统输入信号Vi(t)

图2 静态调节示意图

1.2稳定度分析

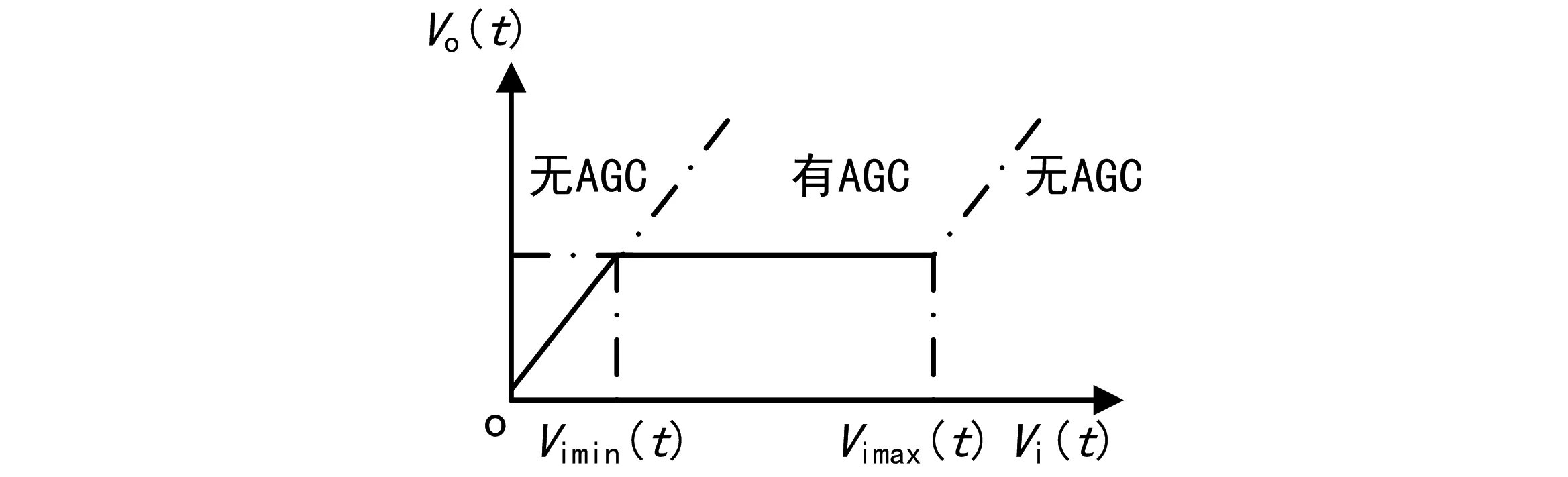

在应用中,对各种闭环AGC系统的系统函数分析,都可以用图3所示的传输函数框图结构来进行理论分析[4]。图中KVGA为可变增益放大器的增益,是单位控制电压变化所引起的增益变化值;KDET为检波器的检波增益,是单位输入功率变化所引起的增益变化值[5]。

图3 简化闭环AGC系统的传递函数框图

在输入端加入幅度为A的阶跃信号,即ε(t)=A,进行拉普拉斯变换,得ε(s)=A/s。设误差信号为E(s),则

(1)

根据终值定理,可求系统环路稳态误差ess信号[6]:

(2)

可见,环路稳态误差与KVGA和KDET有关,设计中要获得较小的环路稳态误差,KVGA和KDET应尽量取较大值。

2系统电路的设计

2.1性能要求

频率范围900~990 MHz;输入信号功率动态范围:-50 dBm~10 dBm;输出信号功率平坦度:≤±3 dB。

2.2存在的难点

2.2.1难点

存在的难点主要有:① 电路匹配问题:要在900~990 MHz的宽频带内实现60 dB动态范围,增益平坦度≤±3 dB,这有一定难度,因此,电路设计必须兼顾噪声和功率增益两方面来设计好阻抗匹配;② 信号耦合:A/D转化器要从AGC系统输出端对输出信号进行定向耦合取样必须采取宽带定向耦合,而市面上的定向耦合器一般都是SMA接头,体积相对较大,不利于系统小型化的设计要求,③ 压控可变增益放大器的选取:首先,要求性能高,要能达到课题指标要求,并留有一定的余量。其次,要保证信号通过AGC系统后不失真,就要求在整个宽频带内要有相同的线性特性;④ 电磁兼容问题:由于工作频段为微波频段,信号在传输过程中以及电磁敏感器件比较容易受到电磁干扰,因此要考虑采取措施来防止和降低电磁干扰;⑤ 从系统稳态误差方面考虑:由式(2)的讨论可知,系统稳态误差与压控可变增益放大器的KVGA值有关。这要求压控可变增益放大器集成芯片要具备尽可能大的KVGA参数。

2.2.2难点解决

匹配问题方面,本设计采用纯电阻阻抗匹配网络和传输线变压器匹配器来实现传输匹配[7];电磁兼容问题方面,采用低相对介电常数和低介质损失因素的高频4层PCB基板[8],同时PCB设计从接地、布局布线、去耦合和旁路、寄生天线等几方面来改善、消除电磁干扰[9,10];信号耦合问题方面,一般耦合器很难在大带宽情况下保持耦合度、隔离度、和方向性的特性一致,而且市面上的定向耦合器一般都是SMA接头,体积相对较大,不利于系统小型化的设计要求。因此,本设计采用二功分器来代替定向耦合器。选取的功分器为0603贴片封装,能够在大于1 GHz频率范围内保持高度特性一致,而且封装可以做得非常小[11];压控可变增益放大器的选取方面,主要从具有宽工作频率范围、高线性度、宽的增益变化范围、以dB为单位实现线性增益控制功能、信号输入方式和体积等角度进行综合选取。

2.3电路设计

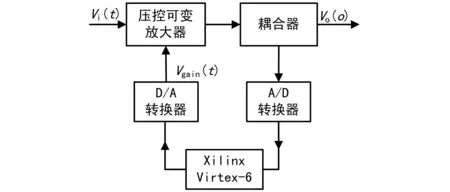

根据设计要求,设计原理框图如图4所示。

图4 设计原理框图

综合考虑设计指标要求和实现难点的分析,压控可变增益放大器选用ADI公司的ADL5330。ADL5330是在宽频带、大动态范围内实现压控增益dB单位线性变化的高性能可变增益放大器,单位控制电压变化所引起的增益变化值为20mV/dB[12],可满足式(2)获得较小的环路稳态误差ess。A/D转换器采用ADI公司的16位单端输出AD5760芯片。FPGA芯片采用Xilinx virtex-6系列芯片。D/A转换器采用TI公司的16位单端输出DAC8760芯片。

2.4系统电路的优点

优点有:① 体积轻小:除了电源转换部分和输入输出接口外,其他元器件全部采用贴片封装元器件;信号耦合采用0603贴片功分器替代;② 高灵敏度和稳定性:大带宽、大动态范围和较好的平坦度都有利于提高系统灵敏度和稳定性。

3系统硬件电路的测试

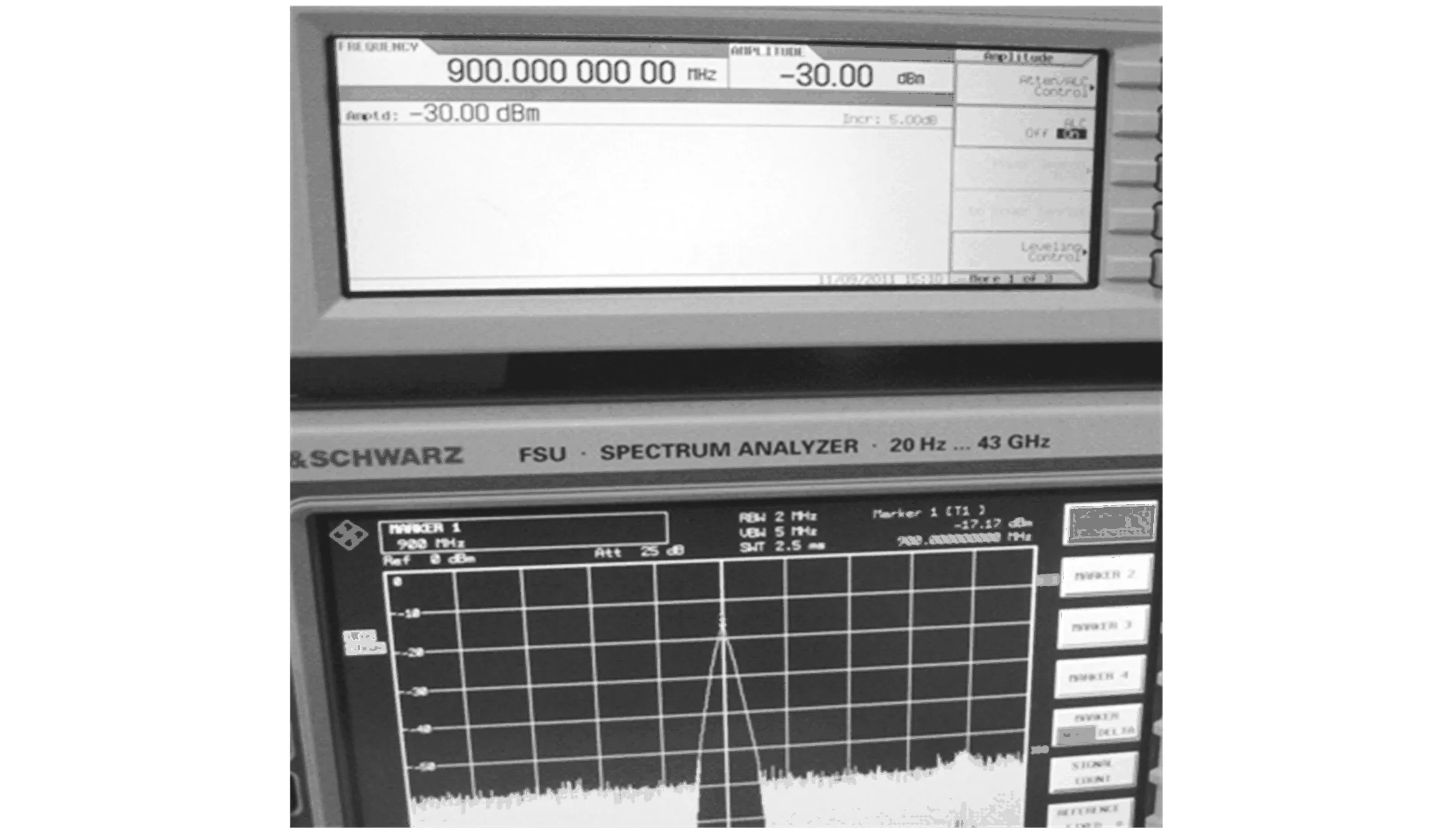

测试方法:由信号发生器Agilent N5183A将信号输入AGC系统电路,然后用Rohde&schwarz fsu43频谱仪观测输出信号频谱和功率。输入信号为900 MHz,功率为-30 dBm时,用频谱仪测得输出信号功率为-17.17 dBm,如图5所示。其他频点的测试结果如表1所示。

图5 输入为900 MHz和-30 dBm时的输出信号功率

输入功率/dBm输出功率/dBm频率900MHz频率945MHz频率990MHz10-15.86-16.00-15.870-15.48-15.69-15.35-10-15.31-15.58-15.36-20-15.66-15.78-15.41-30-17.17-16.57-17.08-40-17.04-16.99-17.35-50-17.21-17.37-17.54

由测试结果可见,AGC系统在900~990 MHz频段和60 dB输入动态范围内输出功率平坦度≤±1.5 dB;输出信号功率可通过调节VEST值来改变,可调范围≥10 dB;控制信号能够较好地对输入信号进行跟踪,从而使输出保持稳定。

4结束语

本AGC系统电路在900~990 MHz及60 dB输入动态范围内,输出信号功率能够保持在-16.5 dBm附近。测试结果表明,系统电路设计符合设计指标要求。但抗噪声性能在设计时没能够加以考虑,故也没有进行测试。因为噪声系数主要是由第一级电路决定,故可考虑在AGC系统输入端串接入一低噪声放大器来改善系统噪声性能。在90 MHz带宽范围内的输出信号平坦度还不够理想,特别是在低输入信号功率点和高频点处平坦度会明显变差,故可以考虑用阻抗匹配和提高电磁兼容性来进一步改善。

参考文献

[1]袁少康.AGC与对数放大器[M].北京:国防工业出版社,1987.

[2]马战刚.大动态高增益雷达接收机设计[D].西安:西安科技大学,2010:30-34.

[3]李飚,段吉海.微波宽带自动增益控制电路的设计[J].桂林电子科技大学学报,2011,31(6):452-455.

[4]张志刚.90dB大动态范围可控AGC系统及其在雷达远程测量平台中的应用[D].上海:上海交通大学,2009:15-19.

[5]张立志,饶龙记,邬江兴.AGC环路方程的一种简化处理方法及环路稳定时间分析[J].通信学报,2005,26(6):94-99.

[6]张立志,饶龙记,邬江兴.自动增益控制环路方程的一种简化处理方法及环路稳定时间分析[J].通信学报,2005,26(6):94-99.

[7]李智群,王志功.射频集成电路与系统[M].北京:科学出版社,2008:10-104.

[8]祝大同.高速、高频PCB用基板材料评价与选择[J].印制电路信息,2003(8):14-31.

[9]姜雪松,王鹰.电磁兼容与PCB设计[M].北京:机械工业出版社,2008:2-24.

[10]黄智伟.印制电路板(PCB)设计技术与实践[M].北京:电子工业出版社,2009:70-99.

[11]ETC Corporation.High Precision Power Splitter PS Series[M].HongKong:ETC Corporation,2009.

[12]Analog Devices Inc.ADL5330 Technical Data Sheet[M].NewYork:Analog Devices Inc,2005.

Design of RF Receiver AGC System Circuit Based on FPGA

LI Biao,LIU Chun-qun,HUANG Zhong-kuai

(School of Information Engineering ,Baise University,Baise Guangxi 533000,China)

Abstract:The purpose of this paper is to design an RF receiver AGC system circuit based on FPGA.According to the operating principle and control theory of AGC system,combining with the requirements of design specifications,using ADL5330,AD5760,Xilinx virtex-6,DAC8760 ICs,the hardware circuit had been designed.The test results are listed below:with 90 MHz bandwidth and 60 dB dynamic range of input signal power,the output signal power has flatness lower than ±1.5dB and adjustable output signal power.

Key words:receiver;AGC system;dynamic range;signal power

中图分类号:TN925+.1

文献标志码:A

文章编号:1003-3114(2016)03-82-3

作者简介:李飚(1978—),男,讲师,主要研究方向:宽带无线通信收发系统。刘春群(1985—),女,讲师,主要研究方向:工业控制及图像处理。

基金项目:百色学院科研基金项目(2013KB08)

收稿日期:2016-01-04

doi:10.3969/j.issn.1003-3114.2016.03.22

引用格式:李飚,刘春群,黄忠快.基于FPGA射频接收机前端AGC系统电路的设计[J].无线电通信技术,2016,42(3):82-84.