电源分配网络设计中一种新型的去耦电容选择方法*

[彭大芹 许海啸]

电源分配网络设计中一种新型的去耦电容选择方法*

[彭大芹 许海啸]

摘要文章对高速电路中电源分配网络的去耦电容选择方法进行了研究。首先对PCB的电源分配网络(Power Delivery Network ,PDN)设计进行了详细研究,详细分析了PDN的结构、模型以及去耦电容选择方法对PDN的重要性。然后对现在常用的去耦电容选择方法进行了分析研究,并提出一种新型的去耦电容选择方法。最后通过仿真软件对这几种去耦电容选择方法进行仿真,通过对仿真结果进行分析、对比,验证本文采用的去耦电容选择方法的可行性与优越性。

关键词:高速电路 去耦电容选择方法 电源分配网络(PDN) 电源完整性 仿真工具Spice

彭大芹

男,重庆邮电大学通信与信息工程学院,正高级工程师,主研互联网、物联网以及车联网方向的终端协议和解决方案等。

许海啸

重庆邮电大学通信与信息工程学院,在读硕士研究生,主研高速电路设计与电源完整性研究。

1 引言

目前,随着超高速集成电路技术的迅猛发展,PCB设计技术也取得了十足进步[1]。众所周知,PCB设计包括信号完整性设计、电源完整性设计、电磁兼容性设计等,随着供电电流的不断增大,供电电压的不断减小,其中的电源完整性设计已经变得越来越重要,尤其是对供电要求苛刻的高速电路系统[2]。电源分配网络(PDN)是移动终端系统中最复杂的互联结构,所有器件都直接或间接的连接到PDN上,这使得PCB的PDN设计已经成为电源完整性设计中最关键的中心一环,可以说,PDN的设计好坏决定了电源完整性设计的好坏,进而影响整个高速电路的供电系统,所以PDN设计已然成为业内关注的焦点[4]。本文首先对PDN的基本结构进行了详细分析,重点分析了去耦电容模块对PDN设计的重要影响。

PDN设计是电源完整性设计的核心之一,一个好的PDN设计必须可以保证负载芯片有一个稳定、持续的电源供给,这是电源完整性的最终设计目的[5]。本文将去耦电容的选择方法作为PDN设计的切入点,通过对现有的去耦电容选择方法进行研究剖析,提出一种新型的去耦电容选择方法,然后基于一款仿真软件Spice,对几种选择方法进行仿真,最后通过仿真结果对比,验证本文提出的新型去耦电容选择方法的可行性及优越性。

2 PDN基本结构

2.1PDN基本结构

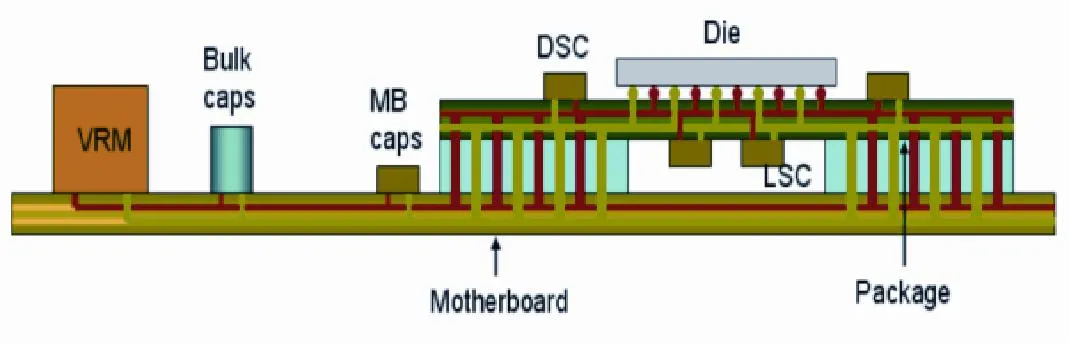

PDN是指从电源输出到最终耗电芯片,电流所经过的所有结构和器件组成的系统。对于典型的PCB系统来说,最基本的PDN包括四大部分:稳压模块(VRM)、印制PCB板、去耦电容器、包含封装的耗电芯片等。基本结构如图1所示。

图1 PDN基本结构

对PDN设计的首要和基本要求是,保持芯片焊盘间恒定的供电电压,并使它能够维持在一个很小的容差范围内,通常在5%以内,从直流到高于1GHz的开关电流带宽范围内,该电压值都必须在其容差范围内保持稳定。减小电源纹波最关键的是降低电流路径上的阻抗值[6]。

其阻抗可由以下公式获得

Z=2⋅π⋅f⋅l

由公式可以看出,回路电感制约着高频率出的阻抗值。所以在进行高速电路PCB设计时,一定要注意减小电流路径上的回路电感值,尤其在高频信号的路径上,只有这样才能时刻满足高速电路电源部分设计的要求。

2.2去耦电容对目标阻抗的影响

图2 电容频率阻抗特性

因此选择去耦电容时,必须充分利用其容性特性,并尽可能在其自谐振频率之前使用,这样可以获得较低阻抗。

PDN的阻抗设计通常需要利用去耦电容的谐振特性,通过电容器的并联组合以获得最低的输入阻抗。同种型号电容器的并联频率响应如图3。

图3 同种电容并联的频率阻抗特性

实际应用中的电容往往都是多个并联使用,因为这样可以大大降低等效的ESR和ESL,增大电容。对于多个(n)同样值的电容来说,并联使用之后,等效电容 C 变为 nC,等效电感 L 变为 L/n,等效 ESR 变为 R/n,但谐振频率不变。可以看出,由于同种型号电容的自谐振频率相同,并联的电容数目越多,其容性、感性区域的阻抗越小,自谐振频率点不变[7]。

在考虑将不同的容值电容并联后,其频率响应如图4。

可以看出,在各自的自谐振频率点之间会引入新的反谐振点,但在该区域之外总的阻抗会减小。去耦电容的并联组合通常用于PDN谐振的抑制。

图4 不同电容并联的频率阻抗特性

3 去耦电容选择方法研究

3.1去耦电容选择方法分析

目前厂商对于PDN设计中的去耦电容没有一个统一、有效的选择方法,大多数厂商的选择只是依照芯片厂商给出的参考设计照葫芦画瓢。经常会出现PDN仿真不过的情况。本论文研究并仿真了一种常用的PDN电容选择方法,并结合去耦电容的谐振频率特性,提出了一种新的电容选择方法,并进行了仿真对比[8]。

大‘V’法是目前常用的PDN电容选择方法,它的出现促进了PDN去耦电容选择方法的研究进程,对PDN目标阻抗仿真起到了极大推进作用。

大‘V’法的基本思想是使用一种电容,通过并联同种电容,产生足够小的阻抗值。它的优点是选择方法简单,简化去耦电容选择过程,可以很快的完成去耦电容的选择。但是大‘V’也存在着不足,并不适用于所用类型的高速电路PDN设计。

本论文采用了一种新的去耦电容选择方法,可以灵活的选择最合适容值和数目的电容。该方法的核心是优先抑制最高阻抗来灵活添加电容。通过检测得出最高阻抗值,并与目标阻抗进行对比,如果超出目标阻抗,则添加对应谐振频率的去耦电容进行阻抗抑制。此种方法可以做到有的放矢,有极强的针对性,可以降低去耦电容的选择数量,节省布板面积。

3.2PDN仿真及仿真结果分析

前面简单分析了常用的两种去耦电容选择方法,接下来我们利用仿真工具Spice对PDN进行频域上的仿真,通过查看它的频率阻抗曲线,比较不同的去耦电容选择方法对PDN阻抗所造成的影响。

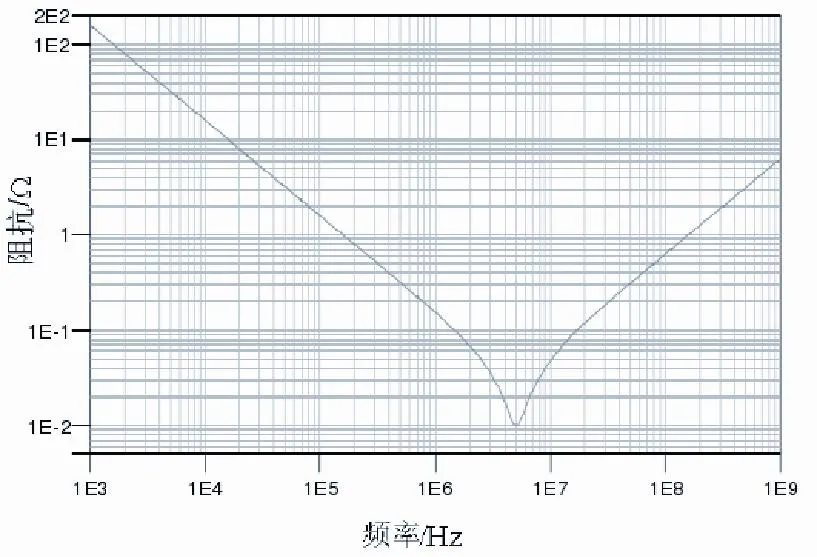

图5是仿真得到的未加去耦电容时的PDN频率阻抗图。由图中可以看出,由于VRM输出电感与电源/地平面间的平面电容发生了并联谐振,在10MHz附近产生了并联谐振峰,使此处的阻抗远远的超出了目标阻抗值。

图5 未加电容的频率阻抗特性

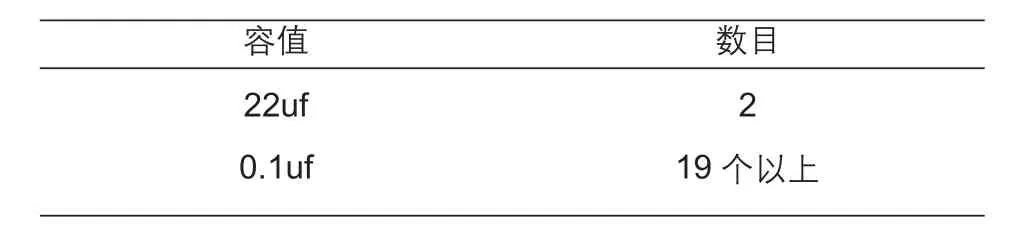

首先我们对大‘V’法进行PDN的频率阻抗仿真,表1是利用大‘V’法选择出的去耦电容类型和数量。

表1 大‘V’法选择的电容

由表1可以看出,大‘V’法只选择了两种容值的电容,除了22uf的滤波电容,另一种就是我们所要选择的去耦电容,并且去耦电容竟然多达19个。

接下来在之前仿真的未加电容的频率阻抗图上添加上利用大‘V’法选择的去耦电容,通过Spice仿真,可以得到图6的新的频率阻抗图。

图6 大‘V’法获得电容的频率阻抗

由图6可以看出,添加了2个22uf滤波电容和19 个0.1uf去耦电容之后,此仿真实例的频率阻抗还是在5MHz左右超出了目标阻抗值,因此可以得到以下结论:大‘V’法可以简化PDN去耦电容选择过程,但是需要大量的去耦电容,对于有限的布板面积来说造成了大量浪费。

接下来我们对本文采用的新型去耦电容方法进行仿真验证,表2是利用新方法选择出的去耦电容类型和数量。

表2 新方法选择的电容

对比表1可以看出,新方法选择出的电容有更多的类型,但是总数目比大‘V’发大大减少,高达8个之多。

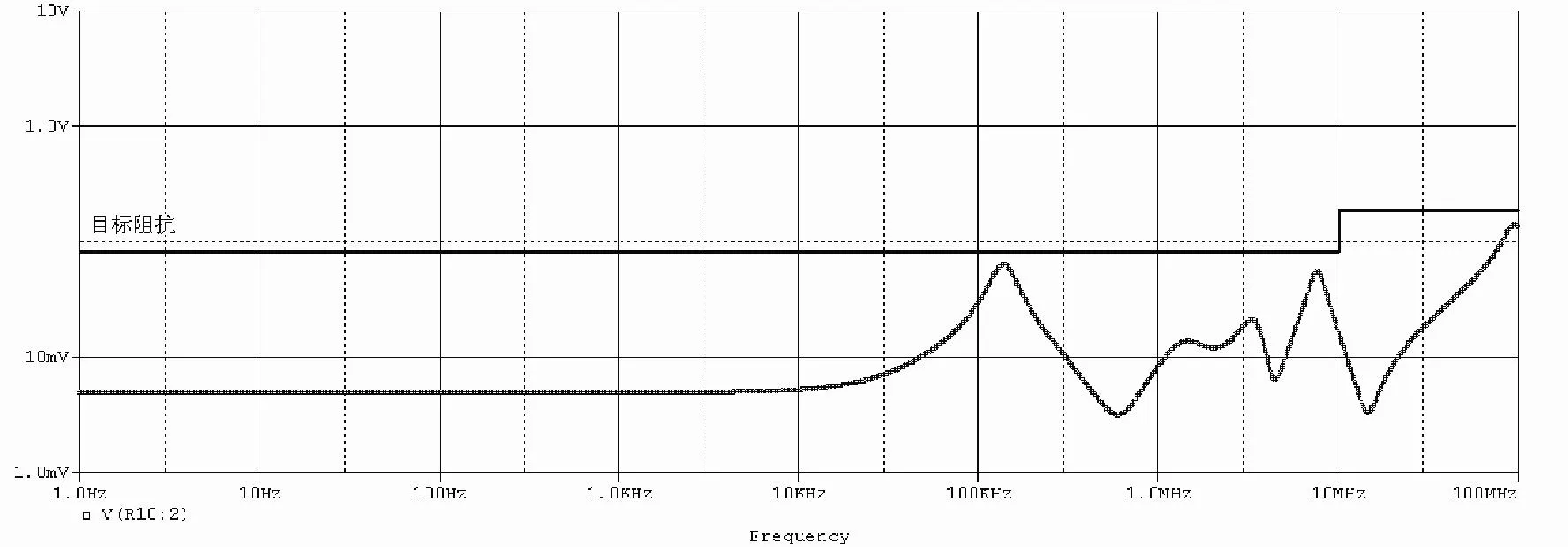

接下来在之前仿真的未见电容的频率阻抗图上添加利用新方法选择的去耦电容,通过Spice仿真,可以得到图7的新的频率阻抗图。

图7 新方法获得电容的频率阻抗特性

由图7可以看出,添加了2个22uf滤波电容和11个不同种类的去耦电容之后,此仿真实例的频率阻抗在各个频率区间都低于超出了目标阻抗值,实现了仿真目的。因此可以得到以下结论:本文提出的新型去耦电容选择方法可以大大节省去耦电容的数量,节省了大量的布板面积,并且可以获得更好的频率阻抗曲线。

参考文献

1唐伟峰.电源分配网络中电容器Spice建模,硕士学位论文.西安电子科技大学,2012

2丁同浩. 高速数字电路电源分配网络设计与噪声抑制分析. 西安电子科技大学博士学位论文,2012

3刘婷婷.电源分配网络及电容器精确建模,硕士学位论文.西安电子科技大学,2011

4陈兰兵,钟章民,肖定如,王辉. Cadence 高速电路设计:Allegro Sigrity SI/PI/EMI 设计指南.电子工业出版社,2014

5Sigrity . 芯片封装电源完整性技术讲座. Sigrity公司,2008

6Madhavan Swaminathan, A.Ege Engin 著, 李玉山,张木水等译. 芯片与系统的电源完整性建模与设计. 北京:电子工业出版社,2009,08

7于争.电源完整性设计详解.网上资料,2009

8Eric Bogatin著,李玉山,刘洋译. 信号完整性与电源完整性分析(第二版).电子工业出版社,2015

DOI:10.3969/j.issn.1006-6403.2016.01.018

基金项目:国家科技重大专项,(NO.2012ZX03001012)

收稿日期:(2015-11-10)