AT24C1024芯片的应用设计

郭洪祥

摘要:数据存储是手持式仪器必备的功能之一且随着电子技术的发展容量要求越来越大。AT24C1024芯片是24C系列E2PROM存储器中存储容量最大的一种,其存储容量为1M位。该芯片具有I2C 2线制串行总线接口,占用单片机引脚较少。本文重点介绍了AT24C1024芯片的内部结构以及芯片的读写时序,结合C8051F060单片机的特点,给出了单片机与存储芯片硬件连接结构。

关键词:C8051F060 AT24C1024 I2C

中图分类号:TP29 文献标志码: B 文章编号:1007-9416(2016)05-0000-00

1 引言

AT24C1024是24C系列E2PROM存储器中存储容量最大的一种, 具有I2C总线接口功能、功耗小、电源电压宽( 2.7~5.5v)、工作电流和静态电流小等特点,其存储容量为1M位。C8051F060单片机是美国Silabs公司生产的系统级芯片,它具有与8051兼容的高速CIP-51内核,指令系统与MCS-51指令集完全兼容,低功耗等优点[1]。

随着电子技术的发展,越来越多的手持设备得到了广泛的应用。因此,人们对设备的功耗和存储空间提出了更高的要求。本文设计的以C8051F060单片机核心的AT24C1024存储芯片应用,具有结构简单、存储速度快、扩充空间方便等优点,现已在多个手持式设备上得到了广泛的应用。

2 AT24C1024芯片介绍

2.1 芯片引脚

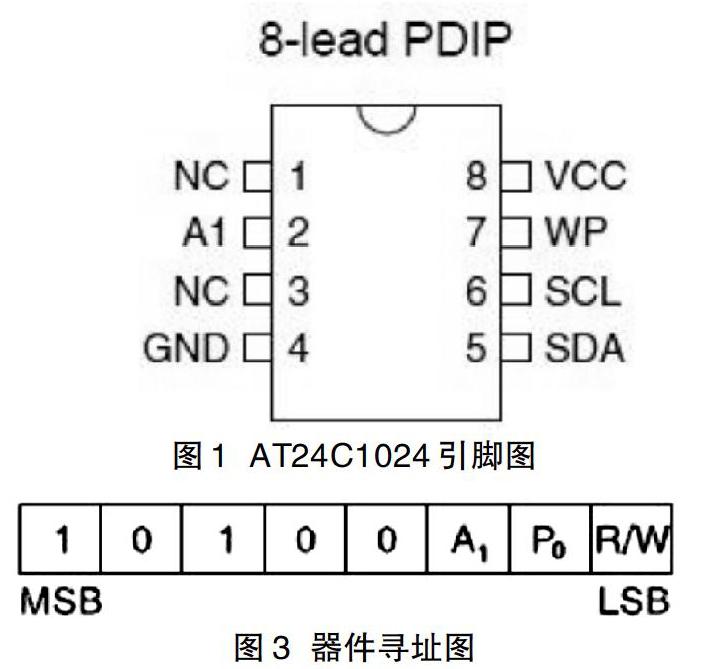

AT24C1024提供1,048,567位的串行可电擦除和可编程只读存储器,它的每8位组成一个字节,共131,072个字节,内部有512页,每页有256个字节。随机访问一个字地址数据需要17位数据的字地址。AT24C1024共有6个有效引脚:VCC、GND、SCL、SDA、A1、WP。其引脚如图1所示[2]。

2.2 器件读操作

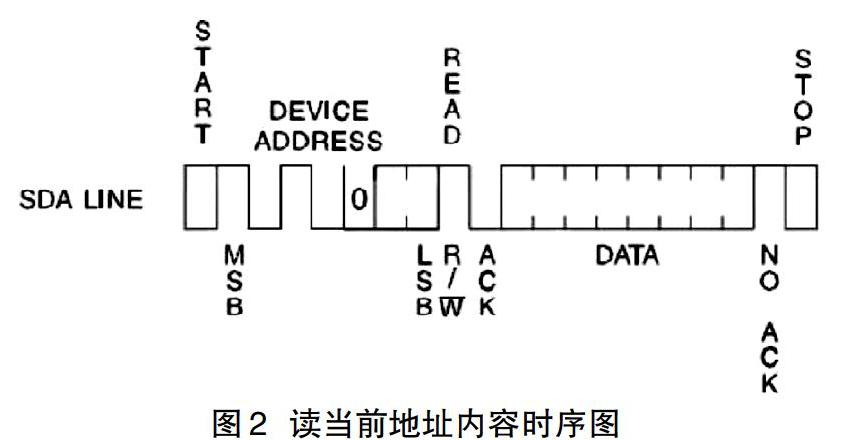

读当前地址内容:AT24C1024的地址计数器内容为最后操作字节的地址加1。即如果上次读/写的操作地址为N,则立即读的地址从N+1开始。AT24C1024接收到地址信号后(R/W 位置1 ),它首先发送一个应答信号,然后发送一个8位字节数据。单片机不需发送应答信号,但要产生一个停止信号。时序图如图2所示。

2.3 器件写操作

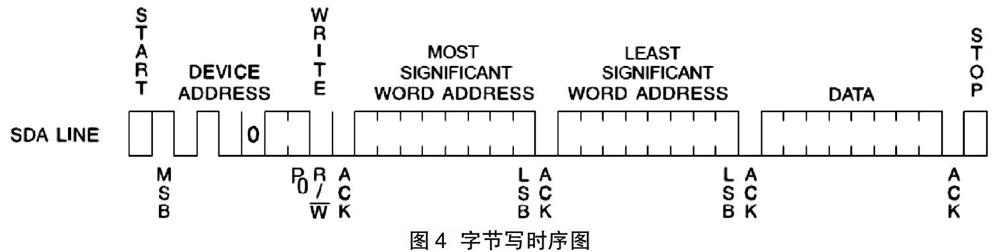

器件寻址:对于AT24C1024来说, 8 位地址的高5 位被固定为10100, A1 为器件引脚的连接信息, 若A1接高电平时, 相应软件中的位为l, A1 接地时,相应位为0。P0为页地址信息, P0为0 时是对前256页操作, 为1时是对后256页操作。R/W表示对从器件的读/写操作,l为读,0为写。时序如图3所示。

字节写:单片机发送两个8 位地址字写入AT24C1024的地址指针,在收到AT24C1024的应答信号后,再发送数据到被寻址的存储单元。时序如图4所示。

页写:页写操作的启动和字节写一样,不同的是在于传送了一字节数据后并不产生停止信号。每发送一个字节数据后AT24C1024产生一个应答位。时序如图5所示。

3 电路设计

硬件设计采用C8051F060芯片作为上位机,其引脚P0.0、P0.1分别与AT24C1024的时序引脚、数据引脚相连。P0.2作为片选引脚与AT24C1024的地址引脚相连。同时为了保证AT24C1024的SCL、SDA能产生可靠的高电平,在其引脚上施加了1K上拉电阻。硬件连接图如图6所示[3]:

4 结语

通过实验表明,该电路设计结构简单,具有良好的可靠性和稳定性,能够对AT24C1024芯片实现良好的数据读取、数据写入等操作,适用于便携式、手持式设备的数据存储。该设计已在实际生产中得到了大量的应用。

参考文献

[1] 张培仁,孙力.基于C语言C8051F系列微控制器原理与应用 [M].北京:清华大学出版社,2007.

[2] AT24C1024数据手册[EB].ATMEL, Rev.1471O–SEEPR–3/07.

[3]张迎新,雷文,姚静波.C8051F系列SOC单片机原理及应用.北京:国防工业出版社,2005.