一种“死时间”少和自动校准容易的Wave Union TDC

许林 周磊

摘要摘要:编码复杂的Wave Union决定了时间数字转换器的“死时间”。如选择合适的发射器延时单元个数,改Wave Union A的单次发射为连续发射就形成了新的Wave Union C(WUC)。采用Wallace树和ROM结构的WUC编码器使用资源少、延时路径短,在Altera的EP3C10E144C8中,时钟频率为400MHz,延时链长度为80的情况下,仅使用了166个逻辑单元,编码时间为2.089ns。WUC实时自动校准避免了全延时链的按位校准,只需对发射器内的延时单元进行校准,且实时自动校准在硬件上只需提供一个不随外界温度和电压变化的TDC时钟且延时链长度增加1倍即可。

关键词关键词:时间数字转换器;Wave Union C;Wallace 树;ROM结构;实时自动校准

DOIDOI:10.11907/rjdk.161396

中图分类号:TP301文献标识码:A文章编号文章编号:16727800(2016)007002404

0引言

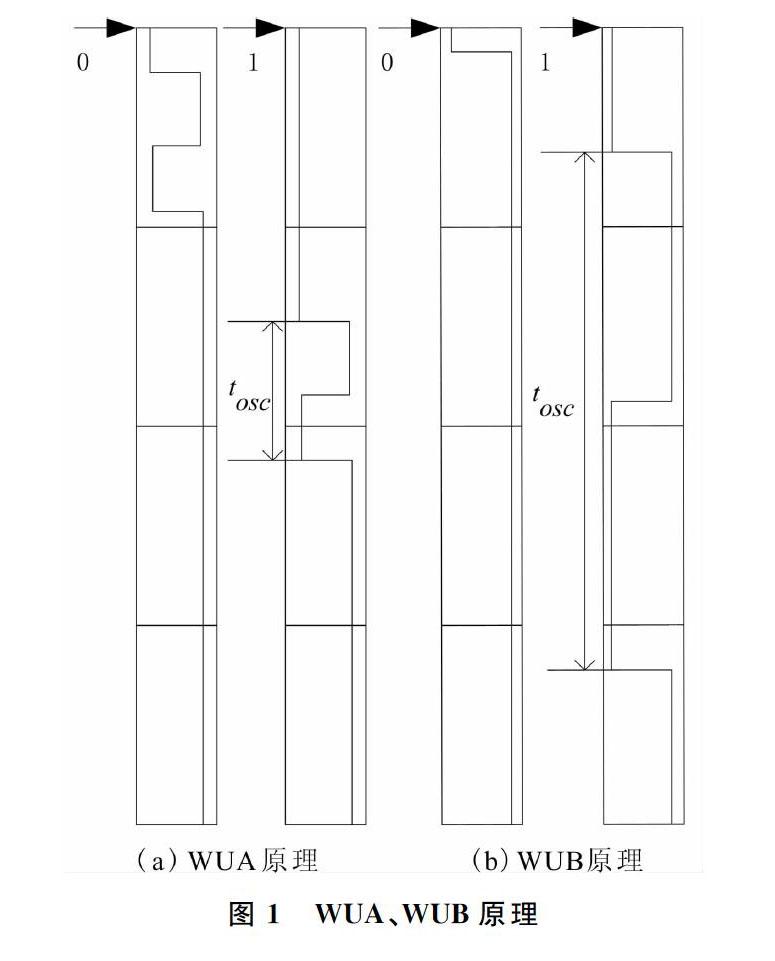

Wave Union方法可以提升时间数字转换器(Time Digital Converter,TDC)的时间分辨率至单元延时以下。Wave Union A(WUA)和Wave Union B(WUB)原理分别如图1(a)和(b)所示,优点是利用一个tosc内跳变沿之间的关系,便可完美地解决首个跳变沿处于延时链超宽位内带来的测量误差问题,并消除由于亚稳态、噪声或时钟网络延时网络不对称等造成的“bubble”现象。最大的挑战是针对锁存延时链得到的非温度计码的编码器设计问题,更短的编码时间意味着可以实现TDC的连续测量以及更短的延时链长度、更长的TDC时钟周期、更低的TDC通道资源使用量。为了消除温度和电压变化对TDC测量精度的影响,采用了占用大量硬件资源的实时按位校准方法。在Altera 的Cyclone II器件上,时钟频率为400MHz,64位延时链的WUA TDC使用了1 621个逻辑单元,其标准差RMSE为25ps、“死时间”为5ns(2个TDC时钟周期);采用WUB TDC使用了6 851个逻辑单元,其标准差RMSE为10ps、“死时间”为50ns(18个TDC时钟周期)。

随后采用的Wave Union TDC主要通过改进多通道测量、实时按位校准和非线性补偿等方面来提升测量精度,但对于编码器这一重要部件的电路实现和性能分析很少,均侧重于TDC测量精度分析。如在Xilinx Virtex-4 FPGA上,实现了时钟频率为100MHz,200位延时链的采用步进树结构编码器的WUB TDC,其标准差RMSE为10ps、“死时间”为50ns(5个TDC时钟周期)。在Xilinx Virtex 5上,实现了时钟频率为120MHz,276位延时链的采用改进胖树结构编码器的WUA TDC,其标准差RMSE为10ps、“死时间”为8.33ns(1个TDC时钟周期)。

针对Wave Union编码器实现复杂、延时过长和按位自动校准困难等缺点,通过选择合适的tosc,改WUA的单次发射为连续发射,实现了一个新的可以克服以上缺点的Wave Union C(WUC)及编码器。1WUC实现

图2(a)为WUC原理图,利用超前进位链实现的WUC如图2(b)所示,其中的前m个延时单元通过一个与门反馈形成一个wave union连续发射器。hit输入0时,延时链的输出I[n-1:0]全为1;hit输入1时,发射器开始输出由m个1和m个0组成的Wave Union,周期tosc如式(1)。

式中,tτ(i)表示第i个延时单元的延时;tf表示反馈路径延时;tnand表示与门延时。

tosc的选择需要保证每个周期的m个1或m个0不会淹没在超宽位里,即保证每个Wave Union在延时链里传输时仍有一个上升沿跳变和一个下降沿跳变。tosc选择不能过大,太大不利于TDC测量精度的提升,如大到一个延时链里只有一个tosc时,WUC就变成了WUB。tosc选择需满足式(2)。

式中,MAX表示延时单元的最大延时值。

为了保证在环境温度变化以及供电电压变化等导致延时单元延时发生变化的情况下WUC能正常工作,在式(2)的基础上tosc需再附加4个延时单元的延时。即由式(1)、式(2)得出的m值需最后再加2进行修正。例如在Altera的EP3C10E144C8中,延时单元的延时值在34~175ps,由式(1)、式(2)可得m=5+2=7。

延时链长度n的选择如式(3),其中tclk为TDC的时钟周期。一般n还需再增加几个延时单元,以保证在环境温度变化以及供电电压变化等导致延时单元延时发生变化的情况下hit的上升沿跳变能在延时链内。如在Altera的EP3C10E144C8中,TDC的时钟频率选择为400MHz时,延时链长度n>71,考虑到每个LAB(Logic Array Block,逻辑阵列块)由16个LE(Logic Elements,逻辑单元)组成[14],即每个LAB内的延时链长度为16,故最终选择的延时链长度为16的整数倍,n取80。在EP3C10E144C8中每LAB之间,LAB的前8个LE和后8个LE之间就会有一个超宽位,m选取小于等于8时,可以避免tosc内包含超宽位。

2WUC编码器实现

2.1发射器状态检测

WUC编码器由计算延时链中tosc个数和计算当前发射器发射状态组成,如式(4):

式中,thit表示hit输入的上升沿跳变到第一个TDC时钟上升沿之间的时间间隔;tosc为发射器周期,由式(1)决定;tlaunch表示当前发射器已经发射的时间;k表示延时链中tosc的个数。

编码器中使用的1-out-of-n码转换分为检测延时链中0-1跳变和1-0跳变两种,分别由式(5)、式(6)表示。

式中,I1n_01[i]表示1-out-of-n码的第i位输出;下标1n_01表示检测0-1跳变沿的1-out-of-n码输出;下标1n_10表示检测1-0跳变沿的1-out-of-n码输出;I[i]表示延时链的第i位输出。

8位ROM结构的1-out-of-n码解码器[15]表达式如式(7):

式中,hROM[i]表示第i位ROM解码器的输出;I1n[i]表示1-out-of-n码的第i位输出。

由于发射器中的延时单元属于一个LAB的前8个LE,故超前进位链的延时差别不是很大,故为了简化计算,使用tavg=tosc/14来表示发射器中各延时单元的平均延时值。tlaunch如式(8):

hROM_01和hROM_10中只有一个有数值,另一个是0,为了降低电路复杂度,图3采用全0检测模块保证正确的tlaunch被送到后继的处理电路。

2.2tosc个数计算

每个tosc包含14个延时单元,故延时链的每个LAB中的前8个和后8个延时单元的输出最多包含一个tosc,相邻两个LAB/2的中间8个延时单元的输出也最多包含一个tosc。检测0-1跳变沿的1-out-of-n码中每个1表示一个tosc,累加1的个数就得到延时链中tosc个数。

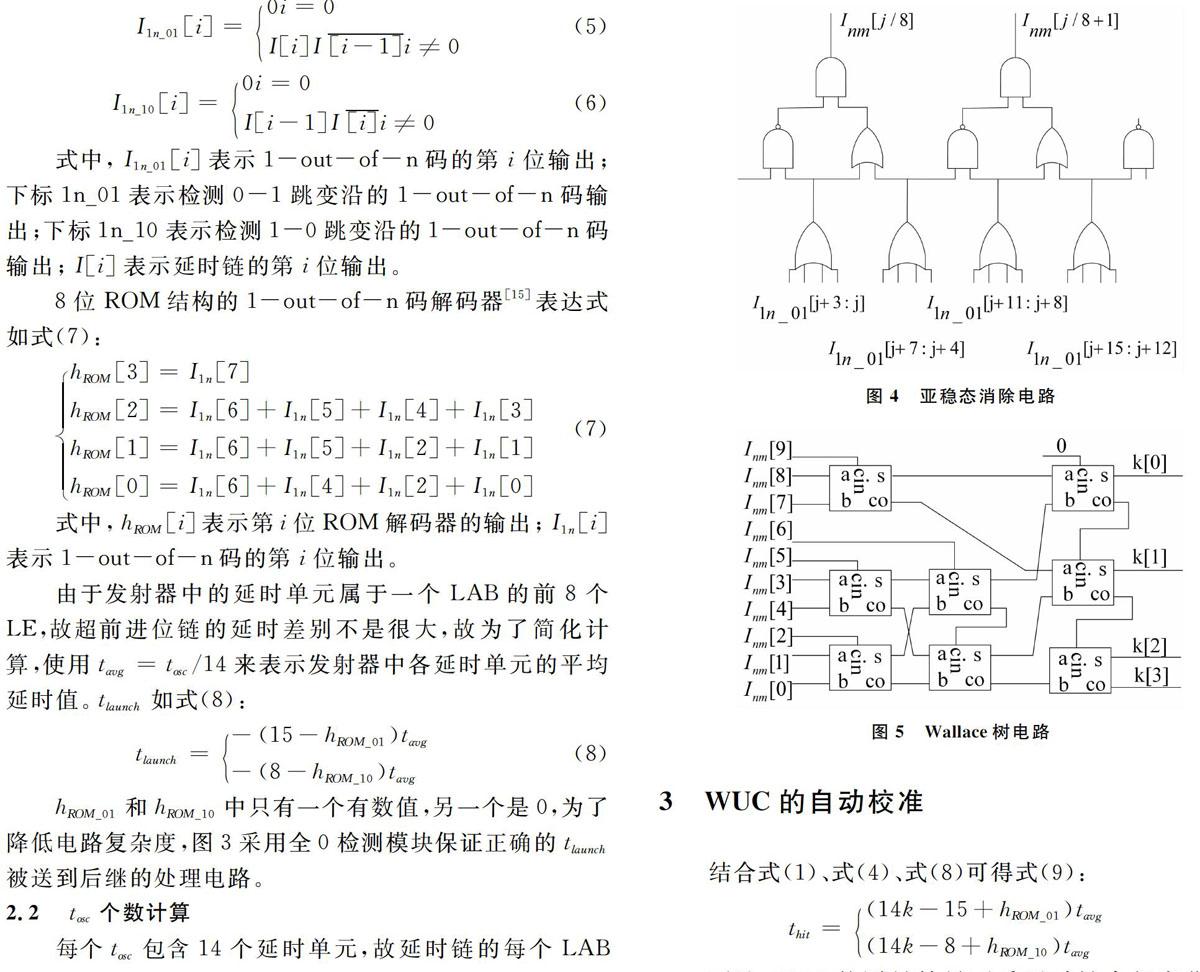

延时链中首个0-1跳变沿在经寄存器锁存时,由于违反寄存器的建立保持时间,会出现亚稳态现象。比如首个跳变沿处应该输出“0011111”,结果实际输出“0010111”、“0101111”、“0010011”和“0010001”等。首个0-1跳变沿处的输出经1-out-of-n码编码后输出“0010100”、“0101000”、“0010010”和“0010001”等。4个延时单元的时间在4*34=136ps,因此首个边沿后面0的个数不会超过3。但这种亚稳态现象导致在相邻的8个延时单元内会出现两个0-1跳变沿的情况。图3中的亚稳态消除电路如图4所示。如果首个0-1跳变和亚稳态0-1跳变处于任一个LAB的前8个和后8个延时单元中,两个四输入或门只会保留1个0-1跳变沿;如果首个0-1跳变和亚稳态0-1跳变处于任一相邻的LAB/2的中间8个延时单元,则说明后继的8个延时单元的输出1为亚稳态,应该清零。计算tosc个数的Wallace树电路[15]如图5所示。图4亚稳态消除电路

3WUC的自动校准

结合式(1)、式(4)、式(8)可得式(9):

可见,WUC的测量结果不受延时链中超宽位的影响,测量精度完全取决于发射器的7个延时单元的延时值。这就意味着,对于延时链的校准只需要对前7个延时单元进行校准即可,这大大降低了实时自动校准难度,进一步提升了TDC的测量精度。

实时自动校准电路的延时链长度是单个TDC延时链长度的2倍。在同一个hit的触发下,设第一个时钟周期测得tlaunch(0)=M(0)tavg,第二个时钟周期测得tlaunch(1)=M(1)tavg。则tavg可由式(10)求出:

故在实时校准时,只需要将TDC的系统时钟tclk修改为一个不随温度和电压变化而变化的时钟源输入,这在硬件电路设计时较为容易满足。

4结语

最终单通道的WUC在Altera 的EP3C10E144C8中实现,使用166个逻辑单元,编码器的编码时间(TDC的“死时间”)为2.089ns(不到1个TDC时钟周期)。优于25ns 的WUA和8.3ns 的WUA。而式(10)的实时自动校准方法极大降低了硬件资源使用率,提升了校准的实时性,而且非常易于实现。

以上描述的是基于FPGA的WUC实现,该WUC完全适用于ASIC的TDC设计。在ASIC设计中,由于很少有超宽位的存在,故发射器的延时单元数m可以选择更小,但考虑亚稳态的问题,建议m≥3,这样以上讨论的WUC编码器电路仍然适用。

参考文献参考文献:

WU J,SHI Z.The 10ps wave union TDC:improving FPGA TDC resolution beyond its cell delay.Nuclear Science Symposium Conference Record,2008: 34403446.

WU J.An FPGA wave union TDC for timeofflight applications.Nuclear Science Symposium Conference Record (NSS/MIC),2009: 299304.

BAYER E,TRAXLER M.A highresolution 48channel timetodigital converter implemented in a field programmable gate array[J].IEEE Transactions on Nuclear Science,2011,58(4): 15471552.

WANG J,LIU S,ZHAO L,et al.The 10ps multitime measurements averaging TDC implemented in an FPGA[J].IEEE Transactions on Nuclear Science,2011.

BCHELE M,FISCHER H,GORZELLIK M,et al.A 128channel timetodigital converter (TDC) inside a virtex5 FPGA on the GANDALF module[J].Journal of Instrumentation,2012.

HERV C,CERRAI J,LE CAR T.High resolution timetodigital converter (TDC) implemented in field programmable gate array (FPGA) with compensated process voltage and temperature (PVT) variations[J].Nuclear Instruments and Methods in Physics Research Section A:Accelerators, Spectrometers, Detectors and Associated Equipment,2012,682(2):1625.

QI J,GONG H,LIU Y.Onchip realtime correction for a 20ps wave union timetodigital converter (TDC) in a fieldprogrammable gate array (FPGA)[J].IEEE Transactions on Nuclear Science,2012,59(4):16051610.

FISHBURN M W,MENNINGA L H,FAVI C,et al.FPGAbased TDC with multiple channels for open source applications[J].IEEE Transactions on Nuclear Science,2013,60(3): 22032208.

ZHAO L,HU X,LIU S,et al.The design of a 16channel 15 ps TDC implemented in a 65 nm FPGA[J].IEEE Transactions on Nuclear Science, 2013,60(5): 35323536.

LICHARD P,KONSTANTINOU G,VILANUEVA A V,et al.Performance evaluation of multiple (32 channels) subnanosecond TDC implemented in lowcost FPGA[J].Journal of Instrumentation,2014.

PAN W,GONG G,LI J.Timetodigital converter implemented in fieldprogrammable gate array with automatic temperature correction[J].IEEE Transactions on Nuclear Science,2014, 61(3):14681473.

HU X,ZHAO L,LIU S,et al.A steppedup tree encoder for the 10ps wave union TDC[J].IEEE Transactions on Nuclear Science,2013,60(5): 35443549.

QI S,LEI Z,SHUBIN L,et al.A fast improved fat tree encoder for wave union TDC in an FPGA[J].Chinese physics C,2013,37(10):102106.

Altera.Cyclone III device handbook\[EB/OL\]. http://www.altera.com.cn/literature/hb/cyc3/cyclone3_handbook.pdf.

SAIL E,VESTERBACKA M.A multiplexer based decoder for flash analogtodigital converters.TENCON 2004,2004:250253.