H.264解码器的帧内预测优化

张亚运,孟李林,景博利

(西安邮电大学 电子工程学院,陕西 西安 710061)

H.264解码器的帧内预测优化

张亚运,孟李林,景博利

(西安邮电大学 电子工程学院,陕西 西安710061)

摘要通过对H.264帧内预测加以优化,以提高其速度。采用4×4块级流水线方式代替串行处理方式,以及自适应的流水线协调不同种类块、不同预测模式下的帧内预测,用四路并行的多功能处理单元在1个周期内计算出1列4个像素点的预测值;以“种子”法取代平面预测模式的直接计算方式。基于FPGA开发平台设计出优化后的预测电路,验证结果表明,优化电路处理一个宏块平均只需196个时钟周期。

关键词H.264;流水线;帧内预测;多功能处理单元

H.264视频压缩编码标准具有较高的压缩效率[1],但计算复杂度相比于上一代视频压缩编码标准H.263增加了10倍以上,编解码时间也成倍增加。另外,H.264视频压缩编码标准所处理的视频图像局限在1 920×1 080分辨率之内,要支持更高分辨率的视频图像,就必须提高解码器的解码效率。对H.264帧内预测算法进行优化,就是解决此问题的途径之一。

H.264帧内预测算法[2]利用空间的相关性,根据当前宏块的相邻已解码参考像素及帧内预测模式,对当前宏块的待预测像素点进行帧内预测计算。

为提升解码效率,可考虑以加法器、数据选择器、寄存器为基础,通过控制接口来重复使用H.264帧内预测硬件结构[3]。也可采用基于4×4子块的并行方法,找出符合并行计算的新预测顺序,以避免数据依赖问题,提高系统运算速度[4],或可采用流水线的办法对硬件结构进行优化,以提高数据吞吐量[5]。不过,这些优化方法仅局限于对硬件结构的改变。

本文拟对帧内预测硬件结构及其算法进行双重优化,即采用4×4块级流水线方式代替串行处理方式,用自适应的流水线协调不同种类块及不同预测模式下的帧内预测,利用4路并行的多功能处理单元在1个周期内计算出1列4个像素点的预测值,采用“种子”法取代平面预测模式的直接计算方式,以求提高帧内预测电路的处理速度。

1硬件结构优化

对帧内预测算法的硬件结构采用4×4块级流水线及4×4块自适应流水线两种不同的流水线设计。4×4块级流水线设计将每个宏块拆分为24个4×4块,4×4块作为最小的处理单元。4×4块自适应流水线主要对帧内预测的参考像素准备及计算进行流水线处理,可根据预测模式、块大小、块类型的不同选择相应的时钟周期,以节约处理周期。

设计一种多功能处理单元(Multifunction Processing Element,MFPE)实现全部13种帧内预测模式下的运算,以节约逻辑单元数量,避免资源浪费。

1.1流水线

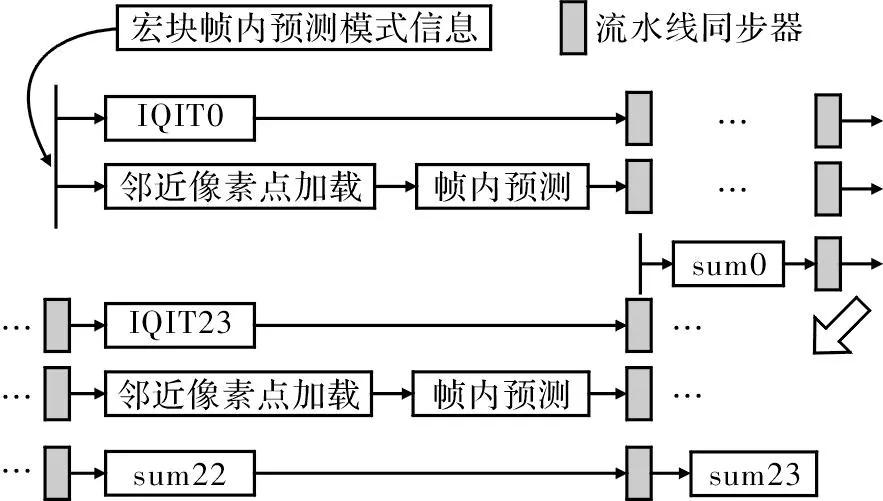

每个宏块可分解为16个4×4亮度子块和8个4×4色度子块。如图1所示,通过每个亮度、色度4×4子块的预测模式及其相应的参考像素完成帧内预测,得到相应的帧内预测结果。随后通过流水线同步器的同步控制将预测结果与残差块相加得到当前4×4子块的重建值,重建块中与下一待预测块相邻的像素点作为待预测块的参考像素点。

与16×16宏块级流水线相比,4×4块级流水线可与H.264标准的最小块匹配,可迅速完成内容切换;需要更少的寄存器用于存储中间变量。4×4块级流水线代替了串行处理方式。

图1 帧内预测4×4块级流水线

1.2多功能处理单元

4×4亮度块的帧内预测模式有9种,16×16亮度宏块的帧内预测模式有4种,色度块的帧内预测模式也有4种,且与16×16亮度宏块的帧内预测模式类似。除垂直、水平、平均预测模式类似外,其余预测模式间基本没有相似点,若针对每种预测模式均设计与其对应的处理单元,会造成大量的资源浪费。故需设计MFPE以处理不同预测模式下的帧内预测。

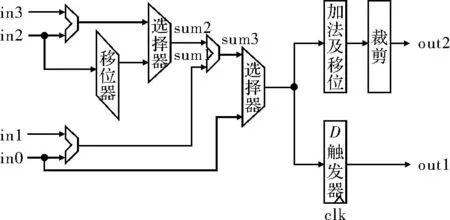

如图2所示,MFPE由4个数据输入、1个时钟输入和2个数据输出组成。输入的参考像素点经过MFPE中移位器和选择器等的处理可得到任一预测模式下的任一待预测像素点的预测结果。MFPE中的内部寄存器负责暂存一些中间产生的结果,供其他MFPE在下一时钟节拍使用。

图2 MFPE的电路结构设计

1.3自适应流水线

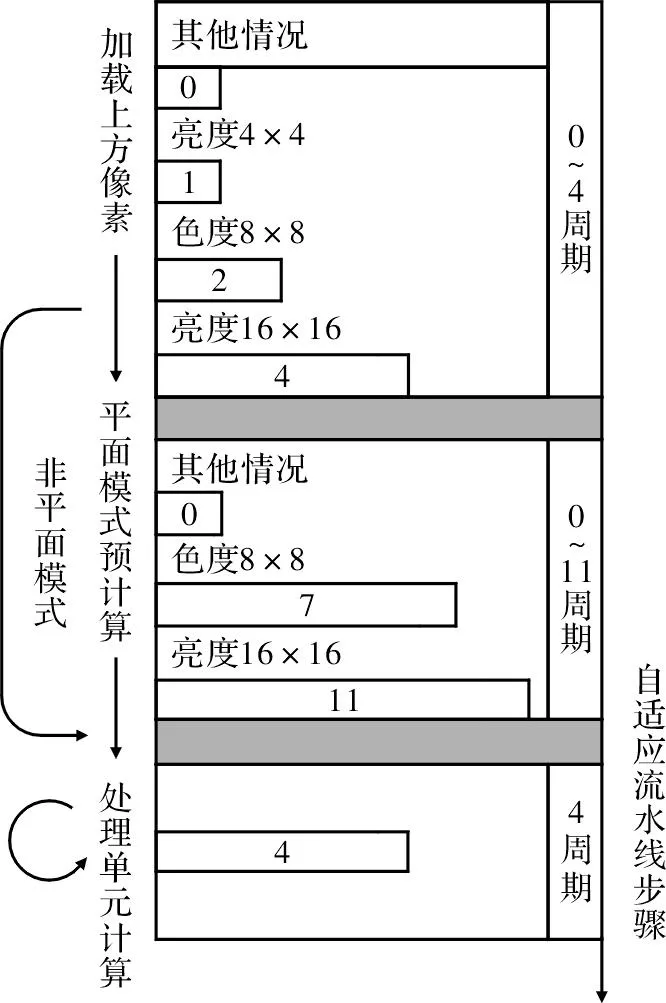

不同的待预测块和帧内预测模式都需要特定位置的相邻像素点用于计算,而一个固定的流水线无法有效地协调整个帧内预测过程。因此,一种自适应的流水线可灵活处理各种情况下的运算。通过自适应流水线的处理,可减小平均预测延迟,提高工作频率[6]。如图3所示,将自适应流水线划分为3个步骤。加载、预计算作为前两个步骤,其处理周期是可变的,根据当前待预测块及帧内预测模式的不同选择其相应的处理周期。计算作为自适应流水线处理的第3步,具有固定的4个处理周期,每个周期通过4路并行的MFPE计算出1列4个像素点的预测值,通过4个周期即可计算出当前4×4块的帧内预测结果。下面详细介绍流水线的3个步骤:

(1)加载。参考像素由上邻块最下一行像素点和左邻块最右一列像素点组成。由于选用存储器的位宽为32位,故存取上方4×4亮度子块最下一行4个参考像素点只需1个周期即可完成,存取8×8色度块参考像素点在2个周期内可完成,存取16×16亮度宏块参考像素点在4个周期内可完成。当采用水平预测模式或上方参考像素无效时,可直接将加载的周期设置为0;

(2)预计算。在进行平面模式预测前,需提前计算出5个中间变量用于后续计算。根据当前待预测像素在宏块中的位置及5个中间变量可计算出预测像素值。该步骤只适用于平面预测模式,除平面预测模式以外的其他预测模式均可在流水线处理中跳过此步;

(3)计算。得到当前4×4块的参考像素及预测模式后,经过4个固定的周期可计算出当前块的预测值。

图3 帧内预测自适应流水线

2平面预测模式的算法优化

对计算复杂度较高的平面预测模式进行算法优化。

除平面预测模式外,其他帧内预测模式可直接通过相邻像素点计算出预测结果,而平面预测模式需要5个中间变量H、V、a、b、c用于预测。首先计算中间变量H/V,其余中间变量可通过H/V计算得出[7]。若直接计算H/V会需要大量的乘法器,必会增加硬件的负担。故将计算分解为加法及移位计算,如乘5可分解为(乘4+乘1),通过一个移位器和一个加法器即可实现计算,其余项的计算方式与之类似。

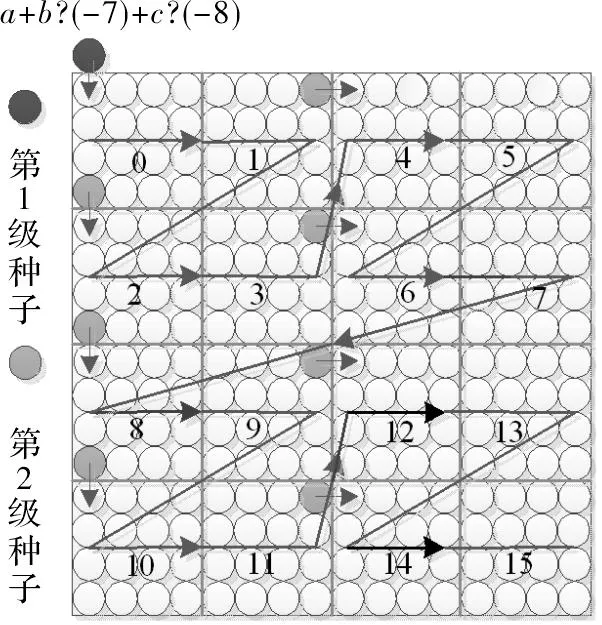

为降低计算复杂度,提出一种两级“种子”法。计算出1个一级种子,通过该一级种子计算7个确定像素点作为二级种子。通过这8个种子算得当前16×16亮度宏块在平面预测模式下的预测值。两级“种子”法的处理顺序如图4所示。

图4 两级“种子”法处理顺序

当前待预测亮度宏块内第0个4×4子块可通过一级种子与中间变量b,c求和完成预测,第1个4×4子块的预测值可通过其左邻像素点与中间变量b求和得出,亮度宏块内其余子块的预测方式与之类似。

若对平面预测模式采用H.264标准中的直接计算方式,则完成一次平面预测操作需要512次乘法操作和1 024次加法操作[8],而两级“种子”法只需279次加法操作和13次移位操作。与直接计算方式相比,两级“种子”法去除了所有乘法操作,减少了72.8%的加法操作,使算法得到优化。

3设计验证

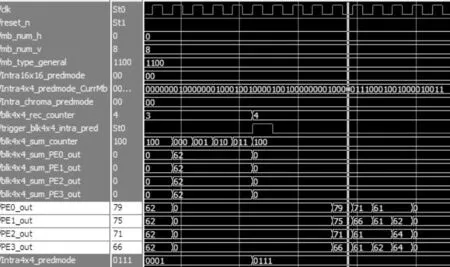

经流水线、并行化处理后的帧内预测器采用verilog HDL实现,在Modelsim SE 10.1a下得到仿真波形,以4×4亮度帧内预测为例对仿真结果进行说明。如图5所示,位于当前图像帧的第8行,第0列的宏块采用4×4亮度块帧内预测方式,Intra4x4_predmode_CurrMb表示当前亮度宏块的全部16个亮度子块的预测模式,blk4x4_sum_PE0_out~blk4x4_sum_PE3_out表示用于参考的重建像素值,可在4个周期内得当前宏块第4个子块的预测值PE0_out~PE3_out。与官方编解码模型JM18.6的提取结果进行比对,可知该预测结果完全正确。经过验证可知,帧内预测硬件电路是完全可行的。

图5 帧内预测仿真结果

基于Altera公司EP4CGX110DF27C7开发平台实现了硬件电路设计,使用Quartus 12.0完成电路综合,结果表明:最高工作频率为53.44 MHz,使用了5 063个逻辑单元,631个寄存器。完成一个宏块预测平均需要196个时钟周期,帧内预测电路每秒可处理272 653个宏块。

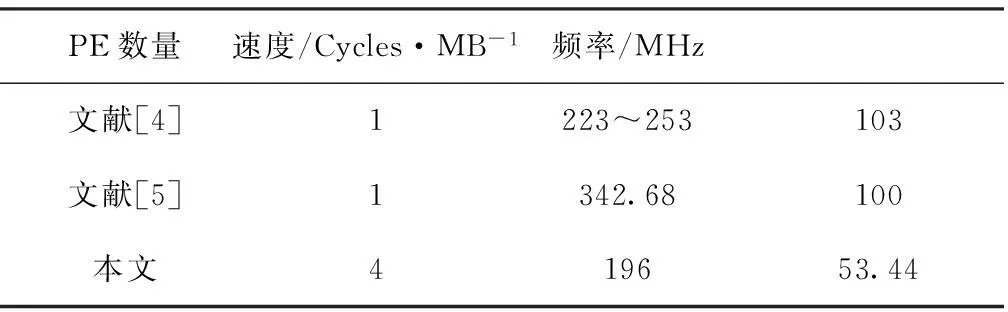

表1为几种帧内预测器的性能对比。本文帧内预测器的预测速度相比文献[4]经并行处理的帧内预测器的预测速度提高了23%,相比文献[5]经流水线处理的帧内预测器的预测速度提高了43%。

表1 帧内预测器性能对比

4结束语

为降低帧内预测算法的复杂度,提升预测效率,本文采用4×4块级流水线与H.264视频编码标准的最小处理块大小相匹配,完成块级流水线处理;自适应流水线减小了平均预测延时,提高了工作频率;采用4路并行的MFPE在4个周期内即可计算得出4×4块的帧内预测结果;在进行平面预测时采用两级“种子”法,去除了乘法操作并减少了72.8%的加法操作。一系列的电路结构及算法优化提升了帧内预测器的运算速度。在FPGA开发平台上实现了帧内预测器的硬件设计及验证,结果表明:该帧内预测电路的工作频率可达53.44 MHz,完成一个宏块平均需要196个时钟周期,每秒可处理272 653个宏块。

参考文献

[1]朱立,成卫,甘羽,等.H.264帧内预测模式判定快速算法研究[J].电网技术,2012,36(7):275-280.

[2]宋云,沈燕飞,龙际珍,等.基于方向梯度的H.264帧内预测模式选择算法[J].计算机学报,2013,36(8):1757-1764.

[3]刘西振,杨静,王威.基于FPGA的H.264帧内预测实现和优化[J].计算机工程,2012,38(7):257-259,262.

[4]Wu Lagou,Zhang Duoli,Du Gaoming,et al.A 4×4 pipelined intra frame decoder for H.264[C].Hong Kong:Anticounterfeiting,Security,and Identification in Communication,IEEE Press,2009.

[5]Wang Xi,Cui Xiaoxin,Yu Dunshan.A parallel intra prediction architecture for H.264 video decoding[C].Changsha:IEEE 8th International Conference on ASIC,IEEE Press,2009.

[6]徐平,余青山,金朝阳,等.基于时空预测的H.264快速帧内预测模式选择算法[J].通信学报,2010,31(9):139-145.

[7]唐浩漾,王曙光.一种改进的H.264帧内预测模式选择算法[J].西安邮电大学学报,2014,19(5):46-50.

[8]汪大勇,孙世新,杨洁淼,等.适合于空间可伸缩编码的帧内快速算法[J].计算机辅助设计与图形学学报,2010,22(11):1959-1965.

Optimization of Intra-prediction for H.264 Decoder

ZHANG Yayun,MENG Lilin,JING Boli

(School of Electronic Engineering,Xi’an University of Posts and Telecommunications,Xi’an 710061,China)

AbstractTo optimize the intra-prediction of the H.264 coding standard for improving the speed of intra-prediction,a 4×4 block pipeline is adopted instead of serial processing method.A adaptive pipeline is adopted which harmonizes the intra-prediction under different blocks and different prediction modes,using the four-channel parallel multifunction processing element to calculate the prediction values of four pixels in a column in one cycle.The “seed” method is adopted to replace the way of calculate directly in planar prediction mode.The optimized intra-prediction circuit is designed by using FPGA development platform.The verification results show that the optimized intra-prediction circuit only needs 196 clock cycles in average to process a macro block.

KeywordsH.264;pipeline;intra-prediction;multifunction processing element

中图分类号TN919.81

文献标识码A

文章编号1007-7820(2016)04-063-04

doi:10.16180/j.cnki.issn1007-7820.2016.04.017

作者简介:张亚运(1990—),男,硕士研究生。研究方向:专用集成电路设计。孟李林(1962—),男,教授。研究方向:计算机系统结构,嵌入式系统。

收稿日期:2015- 09- 09