基于PN码的多通道幅相测量设备设计及实现

张传林,孙垂强

(中国空间技术研究院 西安分院,陕西 西安 710100)

基于PN码的多通道幅相测量设备设计及实现

张传林,孙垂强

(中国空间技术研究院 西安分院,陕西 西安710100)

摘要为测量校准信号源的幅度相位一致性,设计并实现了一种基于可编程门阵列的多通道幅相测量设备。该设备利用伪噪声(PN)码的伪随机性,采用相关解调的方法,在射频直接采样,减少了测量设备带来的幅度相位测量误差,并提高了测量精度。在多通道间的幅度相位差测试结果证明,幅度相位测量精度分别达到0.2 dB和2°。

关键词PN码;多通道;幅度相位测量

Design and Implementation of Multichannel Amplitude and Phase Measurement Device

ZHANG Chuanlin,SUN Chuiqiang

(Xi’an Branch,Academy of China Space Technology (CAST),Xi’an710100,China)

AbstractA multichannel amplitude and phase measurement device based on field programmable gate array (FPGA) is proposed and implemented for the calibration signal source.The device takes advantage of the randomness of PN code and the method of correlating demodulation.Direct sampling at radio frequency is used to reduce measurement error and improve measurement precision.Test of amplitude difference in multi channels shows that the measurement precision of the amplitude and phase is 0.2 dB and 2° respectively.

KeywordsPN code;multichannel;the measurement of the amplitude and phase

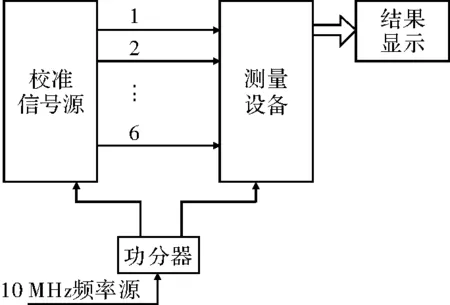

阵列信号处理经常使用多通道,多通道存在通道间的幅度相位一致性,为提高阵列信号处理的精度,需要对多通道的误差进行补偿[1]。为测量通道间的幅度相位误差,设计了高精度的基于PN码的多通道信号源,对多通道校准源之间的幅度相位一致性测量便成为更难解决的问题。本文设计并实现了6通道的测量设备,用于测试多个通道间的幅度相位一致性。测量设备与校准信号源的连接关系,如图1所示。

图1 测量设备与校准信号源连接关系

1理论设计与分析

校准信号源采用伪随机序列中的m序列,m序列是一种重要的伪随机序列,有优良的自相关性,有时称为伪噪声(PN)序列[2],PN序列的周期为2 048,生成多项式为x11+x10+x7+x3+1。由于发送信号的重复周期已知,可在接收端发出一重复周期与发送信号相同的“干净的”本地信号[3],将本地信号与混有噪声的输入信号进行互相关。

设输入信号为

x(t)=s1(t)+n(t)

(1)

本地参考信号为

y(t)=s2(t)

(2)

其中,s1(t)为待测信号,n(t)信号s1(t)中混入的噪声,y(t)=s2(t)为已知参考信号,若s2(t)与信号s1(t)有相关性,而与噪声n(t)无相关性,输入经延时、相乘、积分及平均运算后,得互相关输出Rxy(τ)为

(3)

由于参考信号s2(t)与信号s1(t)有某种相关性,而s2(t)与噪声n(t)没有相关性,且噪声平均值为0,则有Rns2(τ)=0。即Rxy(τ)中包含了信号s1(t)所携带的信号,由此便可将待测信号s1(t)检测出来。

使用Matlab对算法进行仿真,校准源输出信号的调制信号基带波形和调制后的信号,如图2所示。

图2 校准信号

经过相关解调,求出两个通道的最大值点,如图3所示,然后根据最大值点,求出幅度相位差。

图3 通道1与通道2的相关运作结果

仿真通道间的幅度相位一致性结果如表1和表2所示。

表1 通道间幅度一致性仿真结果

表2 通道间相位一致性仿真结果

2软硬件设计

为尽量减少模拟器件对测量通道幅度相位误差测量的影响,接收端减少模拟器件的使用,将输入信号直接匹配输入到模拟到数字转换器(ADC)的输入端。由于校准信号源输出载波为2 GHz,要实现对校准信号的高速高精度数据采集,对ADC的采样频率、模拟输入带宽、量化位数和动态性能都有较高的要求。带通信号无混叠采样条件为

(4)

其中,fs为采样频率;f0为带通信号的中心频率;B为带通信号的带宽;mmax=[(2f0+B)/2B]([x]表示≤x的最大整数)。根据式(4),为采用基于多相滤波的数字正交变换[4]的方法以简化后续的正交解调过程,可选择采样频率满足

(5)

测量设备的实现框图,如图4所示。

图4 测试设备实现框图

测试设备实现使用NI的机箱,该机箱基于面向仪器系统的PCI扩展(PCI Extensions for Instrumentation,PXI)总线设计,共使用3块板卡,两块用于信号采集及数字下变频处理,一块用于为采集板卡提供高精度时钟。

数字下变频后处理结果存储到上位机硬盘,然后上位机进行分析,计算出通道间的幅度相位差。本设备选择E2V公司的EV10AS150AVTP,其单通道最高采样率为2.5 GSample·s-1,量化位数为10 bit,全功率输入带宽为5 GHz,具有良好的动态性能[5]。

高速数据采集中时钟质量非常重要,时钟抖动会造成采样信号的失真及影响后端信号处理的结果[6]。系统选用时钟芯片AD9516-4为ADC提供所需要的高频时钟。AD9516-4可输出6路高达1.6 GHz的低压正发射极耦合逻辑(Low Voltage Positive Emitter-Couple Logic,LVPECL)时钟信号,这6路差分时钟的输出延时可用参数配置,最小延迟单位可达10 ps,为以后ADC的多通道采集提供了完全同步的相参时钟。

信号处理由FPGA(Field Programmable Gate Array)完成,考虑到ADC输出接口,FPGA应能接收高速LVDS信号。LVDS接口具有高速、低功率、抗干扰性能好等特点[7],在差分PCB导线对或平衡电缆上传输速率可达几百Mbit·s-1甚至几Gbit·s-1,并具有低电压、低辐射、低功耗、低成本和可内含时钟等优点。LVDS技术正逐渐成为宽带高速系统设计的首选接口标准。

启用ADC(EV10AS150A)输出MUX功能,可将输出数据率降为500 Mbit·s-1,数据位宽变为20 bit。因此,FPGA可选择Xilinx公司的Virtex-4 FPGA实现,芯片支持LVDS电平标准,最高速率可达1 Gbit·s-1,且片内的数控阻抗(DCI)技术直接配置FPGA内部端接阻抗,每个Bank只需1对电阻便可实现该Bank内所有IO内部阻抗匹配要求[8]。这样省去了专用LVDS电平转换芯片,大幅节省了印制电路板(Printed Circuit Board,PCB)的设计空间。另外,为简化源同步接口,FPGA集成了ChipSync技术,每个IOB均含有SERDES模块(包含OSERDES和ISERDES),集成IDELAY(可变延时线)和Bitslip(比特滑动)功能。利用可编程的精确延迟,可实现动态相位对齐(DPA),以补偿不同链路之间的时滞以及数据和时钟之间的时滞。

2.1FPGA软件仿真

使用Modelsim对FPGA的软件进行了仿真,仿真结果如图5所示。

图5 FPGA软件仿真结果

将FPGA仿真结果与Matlab定点仿真结果进行比较,其结果完全一致。

2.2AD9516-4控制设计

FPAG通过SPI接口对AD9516-4进行参数输入控制[9],图6给出了FPGA与AD9516-4串行控制口连接结构框图。通过串行控制口(/CS,SDO,SDIO,SCLK)来设置,其中,/CS为片选信号。串行口配置时钟SCLK要求最大不超过25 MHz,配置数据由SDIO口来传输,其中指令为16 bit格式,第一位为读/写选择信号,接下来两位为传输字节长度选择,后13位为操作的地址,SDO为读同数据线。

图6 FPGA与AD9516-4串行口连接图

2.3接收ADC输出数据

ADC输出数据率为500 Mbit·s-1,通过串并转换模块扩展位宽降低数据率。位宽由16 bit变为128 bit,数据率降为156.25 Mbit·s-1。

2.4执行数据组帧

数据组帧的依据是带通采样定理,采用率高于信号的带宽的两倍即可不失真地恢复被采样信号。采样率在工程上一般选择带宽的4~6倍,本项目中选择6倍采样。

2.5数字下变频

为提高频率、相位分辨率,需要对组帧后的数据进行数字下变频处理。使用数字正交下变频方案,信号与NCO(0,1,0,-1)输出相乘后,仅用CIC滤波器即可完成满足带外抑制指标的抽取滤波[10]。

3系统测试验证与分析

多通道间的幅度相位差测试结果,如表3所示。从表3中得出,测量设备测量精度中,幅度为0.2 dB;相位为2°。采用多次平均的方法,可提高测量精度。

表3 通道间幅度相位差测试结果

4结束语

本文设计了6通道的高速直接采样的测量设备,使用低时钟抖动的时钟驱动芯片,保证了各个通道ADC的同步采集,在Xilinx公司的Virtex-4 FPGA上实现了算法,利用PN码的相关性对校准信号进行了解调,测量通道间的幅度相位差,设备测量精度高。

参考文献

[1]Lier E,Purdy D,Ashe J,et a1.An on-board integrated beam conditioning system for active phased array satellite antennas[C].Piscataway:Proceedings of 2000 IEEE International Conference on Phased Array Systerns and Technology,IEEE,2000.

[2]郭梯云,邬国扬,李建东.移动通信[M].3版.西安:西安电子科技大学出版社,2004.

[3]韩佳鸣.用于微弱信号检测的数字相关解调器设计[D].上海:上海交通大学,2008.

[4]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[5]E2V Semiconductors.EV10AS150AVTP datasheet[EB/OL].(2009-05-16)[2014-12-29]http://www.e2v.com.

[6]陈佳民,童智勇,杨汝良.时钟抖动对中频线性调频采样及脉冲压缩影响的研究[J].电子与信息学报,2010,32(7):1686-1691.

[7]盂令军,张国兵,王宏涛,等.基于FPGA的LVDS高速差分接口应用[J].化工自动化及仪表,2010,37(5):94-96.

[8]Xilinx.Virtex-4 user guide input advanced select io logic resources[EB/OL].(2008-08-12)[2014-12-29]http://www.xilinx.com.

[9]Analog Devices Inc.AD9516-4 datasheet[EB/OL].(2005-10-19)[2014-12-29]www.analog.com.

[10]于进强,陶小鱼,欧斌.基于CIC滤波的重采样技术[J].信息技术,2008(12):65-67,71.

中图分类号TN911.7

文献标识码A

文章编号1007-7820(2016)03-157-04

doi:10.16180/j.cnki.issn1007-7820.2016.03.041

作者简介:张传林(1983—),男,工程师。研究方向:星载阵列信号处理等。孙垂强(1984—),男,工程师。研究方向:星载阵列信号处理等。

收稿日期:2015- 07- 14