多种高速串行总线的对比研究与分析

刘军伟(中航工业西安航空计算技术研究所,西安,710065)

多种高速串行总线的对比研究与分析

刘军伟

(中航工业西安航空计算技术研究所,西安,710065)

摘要:针对新一代非嵌入式系统及嵌入式系统对数据通信传输能力需求的进一步提高,高速串行总线技术应时而生,高速串行总线中应用最为广泛的三种为以太网总线、PCIe总线及RapidIO总线。对比分析以太网、PCIe及RapidIO的特点及原理,通过对比其区别为硬件设计时选用合适的高速串行总线提供一定的帮助。

关键词:以太网;PCIe;RapidIO

0 引言

随着计算机技术的发展,当前及下一代计算机系统对通信带宽的需求也越来越高。其中如何能提高数据传输速度及传输效率是系统必须解决的问题。嵌入式系统处理器的频率不断提高,高处理性能的处理器与低数据传输速度间的矛盾日益突出,于是高速的串行总线应时而生,其中最常使用的是PCIe及RapidIO总线。非嵌入式系统间的互联则通常选用以太网。

以太网、PCIe及RapidIO三种高速串行总线都是基于相似的SerDes串行解码技术,具有一定的相似性,三者无论从数据传输速率、带宽或者时延性各方面指标均优于并行总线,然而三者在物理层、传输层及逻辑层等方面也存在差异。了解清楚三者的相似性及差异性,有助于硬件设计时选用合适的高速串行总线,最优化地完成硬件模块相应功能设计。

1 概述

以太网是由Xerox公司创建并与Intel、DEC联合开发的基带局域网规范,是一种基于总线型拓扑结构,使用分布式仲裁机制解决数据冲突的总线,其采用载波监听多路访问及冲突检测技术(即CSMA/CD技术)。以太网上的设备任何时候都可以发送信息,但发送前需检测网络是否空闲,即“监听”,假设某时刻有多个设备发生冲突,则检测到冲突,欲发送数据的设备就需等待一段时间,即“回退”,回退时间随机产生,回退时间过后再次试图发送,这就是以太网中提到的载波监听多路访问及冲突检测技术(即CSMA/CD技术)。以太网按照传输速度可分为标准以太网(传输速度10Mbps)、快速以太网(传输速度100Mbps)及千兆以太网(传输速度1000Mbps)。三种以太网中,千兆以太网以其高的传输速度特点,通常与PCIe总线及RapidIO总线进行比较。

PCIe全称Peripheral Component Interface Express,是由Intel公司在PCI并行总线的基础上于2001年提出的用来取代PCI总线的下一代高速串行总线接口标准,也可称为3GIO。PCI总线是一种33MHz@32bit或者66MHz@64bit的并行总线,带宽为133MB/s至533MB/s,连接在其总线上的设备共享带宽,然而随着计算机通信技术的进一步发展,新一代的高速接口总线大量涌现,例如千兆以太网、光纤通道(FC)技术等使得PCI总线的带宽已经无力应付系统内部大量的高带宽并行读写要求,PCI总线也成为系统性能提升的瓶颈,于是就出现了PCIe总线。PCIe是一种高性能、高灵活性、高可扩展性、稳定可靠的低成本通用I/O 架构,它融合多个市场领域的所有应用要求,以无缝的方式弥补了现有PCI 总线的不足并进行市场过渡,使设计人员能够逐步采用新的拓扑技术。PCIe总线是基于对芯片间的互联的需求及以较低的开销升级现有的PCI结构的性能需求的基础上开发出来的。PCIe总线接口根据对应位宽的要求可分为1X、2X、4X、8X及16X,相应接口均向下兼容。同时PCIe总线具有点对点串行互联,双通道、高带宽、传输速度快,以及支持设备热插拔及热交换等优点。

RapidIO是由Motorola和Mercury等公司研发的一种高性能、低引脚数、基于数据包交换的开放式的互联技术标准。目前主要采用的标准为RapidIO 1.x及RapidIO 2.x,其中RapidIO 1.x标准支持信号传输速率为1.25Gbps、2.5 Gbps、3.125 Gbps,RapidIO 2.x标准兼容RapidIO 1.x标准,同时支持5GHz及6.25GHz的传输速率。目前嵌入式系统主要使用的是RapidIO 1.x标准。RapidIO总线具有高带宽、低延时同时对于软件透明等优点,同时RapidIO总线具有比以太网、PCIe总线更高的传输效率,能广泛满足嵌入式系统的应用的需求。

2 区别

2.1基本性能比较

千兆以太网、PCIe及RapidIO均为高速串行总线,三种总线的基本性能如下表表1所示。

通过比较可以看出,千兆以太网、PCIe及RapidIO三种高速串行总线有很多相似的特点,譬如具有高的传输速率,具备较长的传输距离等等。然而同时它们也有其各自特有的特点,譬如有无前端CRC、最大有效载荷等等。了解清楚三者的相似性及差异性,有助于硬件设计时选用合适的高速串行总线,最优化地完成硬件模块相应功能设计。

表1 基本性能对照表

2.2物理层区别

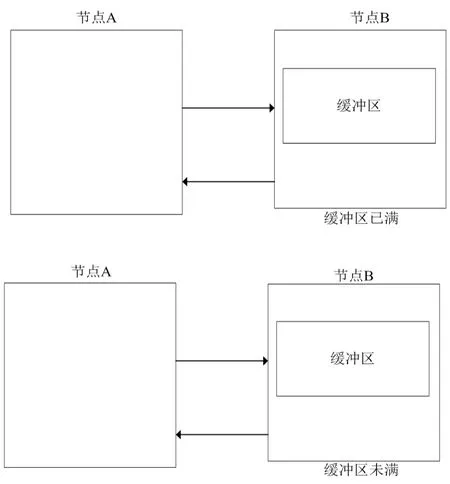

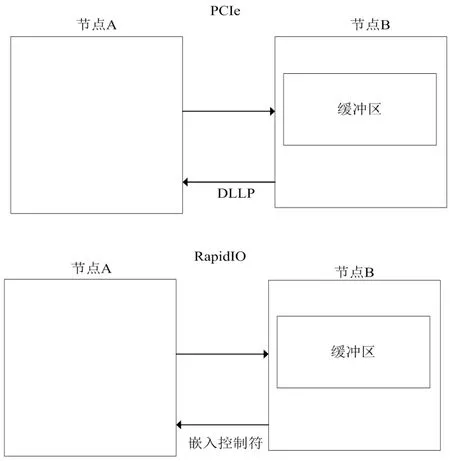

在物理层,三者在流量控制及误码恢复机制方面有着很大的区别。以太网流量控制主要是在网络层用软件实现的,其物理层的流量控制机制是PAUSE,同时其采用弃包的方式处理拥塞。PCIe和RapidIO的物理层流量控制机制可确保数据包发送的可靠性,其中每个数据包都会被保留直到被确认,如果检测到误码,链路维护协议迫使重传。PCIe采用数据链路层数据包即DLLP来进行发送,而RapidIO则使用嵌入式控制符进行数据的发送,其原理与数据链路层数据包(DLLP)不同,RapidIO控制符可以被嵌入在数据包中,可以实现低时间延迟的流量控制信息交换,同时允许在一定时间内发送更多的数据包。以下图1及图2直观地反映了这一概念。图1中当节点B的缓冲区数据满时节点A不能向节点B发送任何数据包,节点B可以向节点A发送数据包,当节点B的缓冲区空闲出来时,节点B需向节点A告知。图2中DLLP在当前数据包的传送完成之前是无法传送数据,而RapidIO的控制符被嵌入在正在发送的数据包中。将控制符嵌入在正在发送的数据包中的特性使RapidIO具有PCIe和以太网目前无法提供的能力。RapidIO能以更低延迟和更高的吞吐量完成可靠的数据包传送。

图1 示意图

发送的数据包中的特性使RapidIO具有PCIe和以太网目前无法提供的能力。

图2 DLLP与嵌入式控制符示意图

2.3传输层区别

RapidIO和以太网均支持多种拓扑结构,在任何端点组都可以用任何拓扑结构进行连接,包括环形、树形及网状等多种拓扑结构。其所发送的数据包根据其网络地址完成具体路由过程。其中以太网的IP地址是其网络地址,RapidIO的destID是其网络地址。系统扩展在RapidIO和以太网中不受任何约束。然而,PCIe则与之不同,PCIe在支持单个根联合体的树状结构(即Root Complex结构),其扩展则依靠PCIe桥片来实现,一个PCIe层可以访问另一个PCIe层。以太网、PCIe及RapidIO在误码检测、提醒及恢复机制等方面具有相似的功能同时具有各自的特点。以太网与PCIe、RapidIO相比,误码检测机制相对较慢,其时延要大很多。PCIe与RapidIO相比较,虽然都可以保证数据包的发送,但在误码条件下均会弃包来防止链路堵塞,PCIe的误码条件机制不可配置,当链路需要在询链时数据包通常会被丢弃。相反RapidIO的误码管理有很大的灵活性,允许对误码作出重新询链的响应,当误码发生时系统立即开始弃包或者保留包并允许堵塞的发生。

2.4逻辑层区别

以太网、PCIe及RapidIO在逻辑层方面存在着较大的差异。其中在所支持的语义方面的差异尤为明显。PCIe数据包支持基于地址的读写语义,发起读或者写的实体必须知道系统的全局存储器映射图中的目的地址。PCIe同时也支持通过消息TLP的消息传送,不过消息TLP只支持有限数量的功能,例如中断和复位信号,这点与以太网及RapidIO消息包有很大的不同,以太网和RapidIO可用于进程间通信。以太网协议只支持消息语义,在发送消息时发送者只需要知道接收地址。寻址机制一般是分层的,因此没有哪个节点必须知道所有的地址,地址可能会改变。RapidIO同时支持读/写及消息语义,除了明显的架构优势和系统灵活性外,对读/写和消息处理的支持允许单路互连。在逻辑层方面RapidIO要比PCIe及以太网更简单。在读写语义的效率方面,RapidIO和PCIe的效率明显高于以太网的远程直接存储器访问(RDMA),RDMA协议建立在其它以太网协议上,比如TCP,其中每个数据包都需要大量的包头开销。与RapidIO读/写事务处理相比,RDMA在时延和带宽方面消耗大。

3 总结

以太网、PCIe和RapidIO都是基于相似的Serdes技术,它们在使用可用带宽方式及适用的专门领域上存在着差些。以太网适合地理上分散的具有长延时并且动态网络配置的网络系统。PCIe则能对单板上的分层总线结构提供最理想的支持,PCIe为外围设备到主机DMA的连通性提供高性能的的内部互联,这两种技术都可用于板上、板间和设备间的通信,而且在很多时候被用于同一系统。RapidIO是一种高性能的交叉开关内部互联技术,具有与PCIe和以太网相似的功能,并且具有其他互联技术无法达到的优点,能将这两种互联的优势结合到单个互联中,并可显著节省资源。RapidIO可以弥补以太网及PCIe总线的不足,RapidIO适用于高实时性、高可靠性的嵌入式系统设计中,PCIe由于其数据传输速率高、系统拓扑简单、技术门槛低及设计成本低等特点,则更适用一些对成本控制严格,对实时性、可靠性要求较低的嵌入式系统中。

参考文献

[1] 廖寅龙.田泽.FC网络通信中PCIe的接口的设计与实现[J],航空计算技术2010.

[2] 孟会.刘雪峰.PCI Express 总线技术分析[J],计算机工程,2006.

[3] 翟彦彬.蒋志焱.张保宁.大规模RapidIO协议交换的FPGA实现[J],现代雷达,2011.

刘军伟,中航工业西安航空计算技术研究所,工程师。

Comparative Study and Analysis of Multiple High Speed Serial Bus

Liu Junwei

(AVIC Computing Technique Research Institute;Xi’an;710065)

Abstract:For a new generation of non-embedded system and embedded system of Data transmission capacity needs to further improve,the high speed serial bus should be timely,high speed serial bus used most widely three is Ethernet bus,PCIe bus and RapidIO bus.Comparative analysis of principles and characteristics of Ethernet bus,PCIe bus and RapidIO bus,through the comparison of the difference,the hardware design for the selected appropriate high speed serial bus to provide some help.

Keywords:Ethernet;PCIe;RapidIO

作者简介