Buck型DC-DC电路振铃现象的抑制

来鹏飞,陈 峰,曹发兵,李 良

(无锡中微爱芯电子有限公司,江苏 无锡 214072)

Buck型DC-DC电路振铃现象的抑制

来鹏飞,陈 峰,曹发兵,李 良

(无锡中微爱芯电子有限公司,江苏 无锡 214072)

摘 要:Buck型DC-DC电路在负载较大时,外接电感电流在一个调制周期内会出现减小到零的情况。为了防止电路进入强制连续导通模式(FCCM),电感电流反向,导致负载电容通过续流NMOS管放电,降低DC-DC的转换效率,需要设计保护电路在电感电流减小到零时检测电感前端电压,当电压大于零时强制关断NMOS管,使电路工作于断续导通模式(DCM)。由于开关管寄生电容与外接电感LC形成振荡回路,电感残余电流产生振铃现象。为了抑制振铃现象,通过控制电路在LXC与地之间接入阻尼电阻,减小电容的等效并联电阻,加快振荡衰减。

关键词:Buck型变换器;DC-DC电路;抗振铃;阻尼电阻

1 引言

Buck型DC-DC变换器在宽泛的工作电压内具有很高的转换效率,使之成为便携式电子设备优先选择的电源管理电路。目前集成DC-DC电路为了提高效率多采用开关型调整器,工作过程中伴随较高频率的开关切换,期间输出高频噪声容易对系统中RF等噪声敏感电路的正常工作产生干扰,尤其当DC-DC电路负载电流较小时,电路进入DCM状态,由外接储能电感和电路内部开关功率管寄生电容形成的谐振回路会产生明显的振荡,需要采取有效的措施抑制振铃现象。

本文首先介绍了Buck电路的工作原理,然后分析了振铃现象产生的原因以及Buck电路中抗振铃电路设计的困难,最后提出一种采用阻尼电阻抑制振铃现象的方法。

2 振铃现象的形成

2.1Buck型DC-DC工作原理

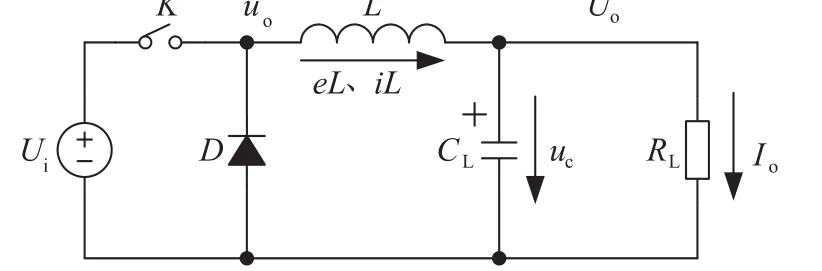

Buck型DC-DC变换器拓扑结构如图 1所示。储能电感L在控制开关K导通时将流过的电流iL转换成磁能存储,同时防止输入电压Ui直接作用于负载电阻RL,产生大的电流,对负载产生冲击,然后在控制开关关断时把磁能转化成电能为负载提供能量;储能电容CL在开关导通时将流过电感的部分电流以电荷形式存储,然后在开关关断时通过负载放电,提供能量;续流二极管D在控制开关关断时为储能电感释放能量提供电流通路。在控制开关关断时,储能电感将产生反电动势使电流iL由反电动势eL的正极流出,通过负载电阻,再经过续流二极管后回到反电动势eL的负极。

图1 Buck型DC-DC电路拓扑结构

Buck型DC-DC电路的具体组成如图2所示。拓扑结构中的开关K及续流二极管D分别采用PMOS管MP和NMOS管MN实现。D1与D2是MOS管衬底寄生二极管,CP是MOS管漏端的寄生电容。由于开关管MN和MP面积较大,所以CP值往往也很大。Buck电路稳定工作时,电感电流iL的有效值等于流过负载的电流, 下面按照电路的3种工作模式进行分析[1]。

图2 Buck型DC-DC具体电路

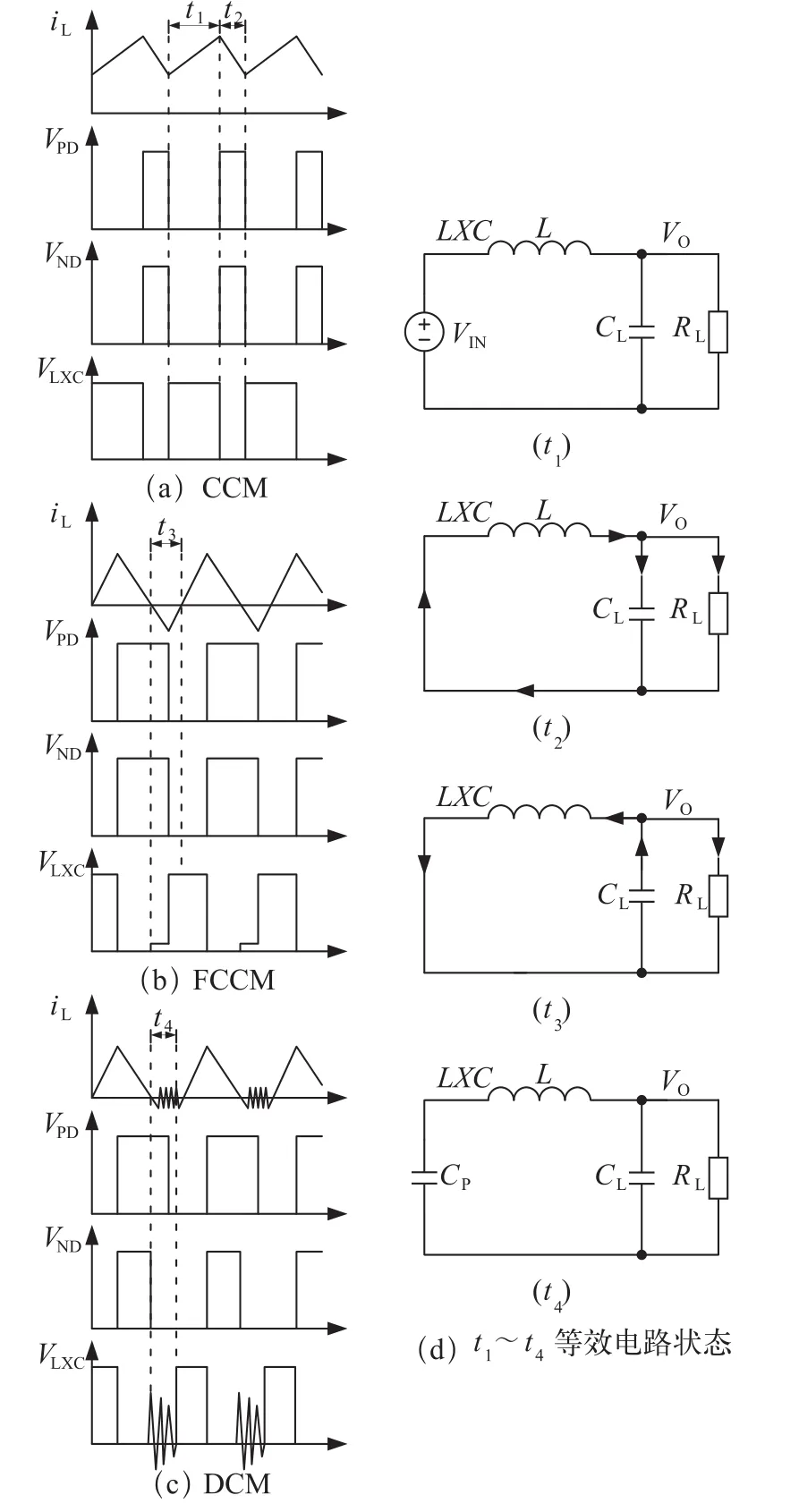

2.2CCM状态

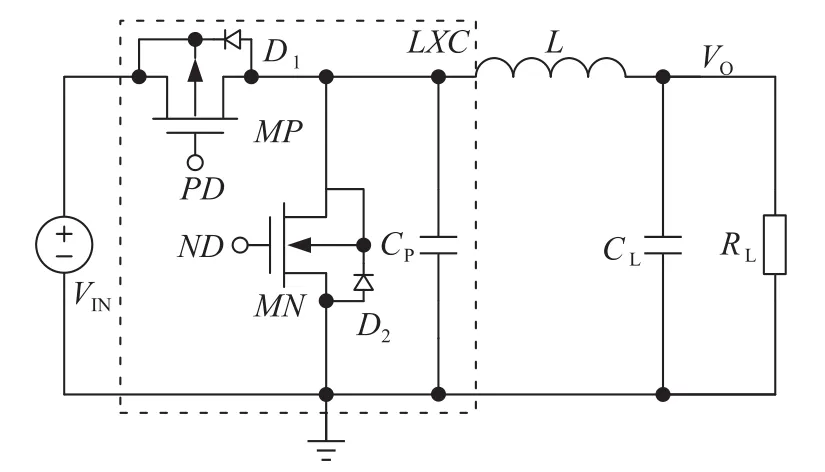

当负载电流较大(负载较小)时,电感电流iL在一个调制周期内不会下降到零,电流方向也不会发生变化,此时电路进入连续导通模式(CCM)[2],如图3 (a)所示。调制周期包括2个阶段。在t1阶段,P管导通,N管关断,电感两端电压VL=VIN-VO>0,电感电流iL连续上升;在t2阶段,P管关断,N管导通,电感两端电压VL=-VO<0,电感电流连续减小。在t1阶段,寄生电容CP通过MN短路到地;在t2阶段,CP通过MP与VIN构成低阻回路。整个周期交流等效电路与t2阶段的直流通路相同,如图 3(c)t2所示。

图3 Buck电路工作模式及对应的等效电路

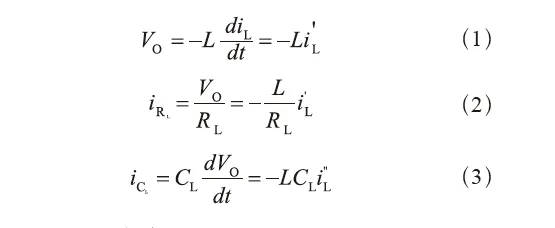

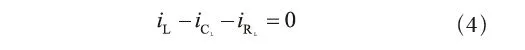

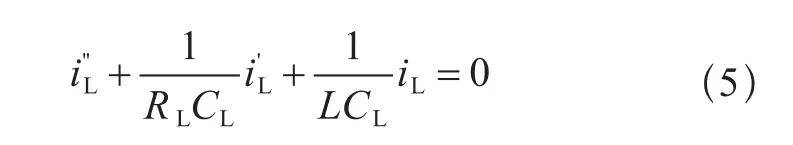

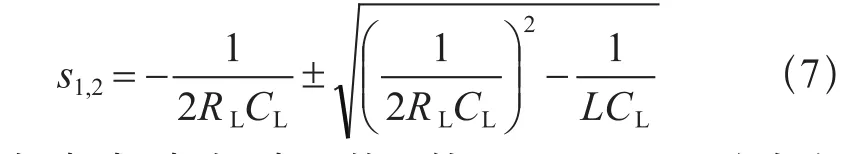

图 3(d)t2中由RL、CL、L构成的回路中[3]:

根据KCL定律:

将以上3式带入(4)式计算得:

(5)式的特征方程为:

特征根为:

根据电感、电容、电阻的取值不同,RLC回路会有3种阻尼状态:

(1)当(1/2RLCL)2>1/LCL时,为过阻尼状态;

(2)当(1/2RLCL)2=1/LCL,为临界阻尼状态;

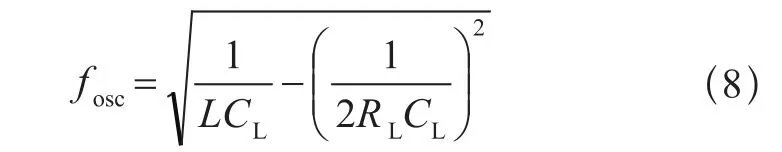

(3)当(1/2RLCL)2<1/LCL,为欠阻尼状态,LXC处出现衰减振荡,频率为:

通过上面的公式可以得出,振荡会随着RL的减小而加快,当RL足够小时,Buck电路进入过阻尼状态,LXC处不会振荡。通常Buck电路外围负载电容较大,欠阻尼振荡的频率只有几十kHz,远小于电路内部开关调制频率(MHz级),如果负载电阻较小,振荡会很快消失,在调制过程中不会对电路造成干扰。

2.3FCCM状态

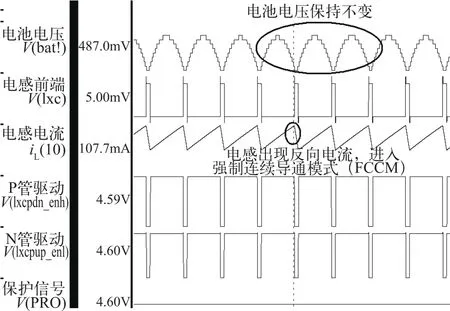

同步拓扑结构中采用NMOS开关管代替续流二极管,NMOS的导通压降远小于二极管的压降,虽然显著减小了续流通路的导通损耗,但是当负载电流较小(RL较大)时,电感L电流iL在一个调制周期内会下降到0,此时VND仍然为高电平,MN仍然导通,CL通过电感L对地放电,电感电流方向发生变化,电路进入FCCM[4],如图 3(b)所示。此时Buck电路包括3个阶段,t1、t2阶段与CCM类似,t3阶段的等效电路如图 3(d)t3所示。如果Buck电路用于对电池充电,电路工作于FCCM会导致电池电压停滞,电池处于充电-放电电压保持不变的状态,如图 4所示。

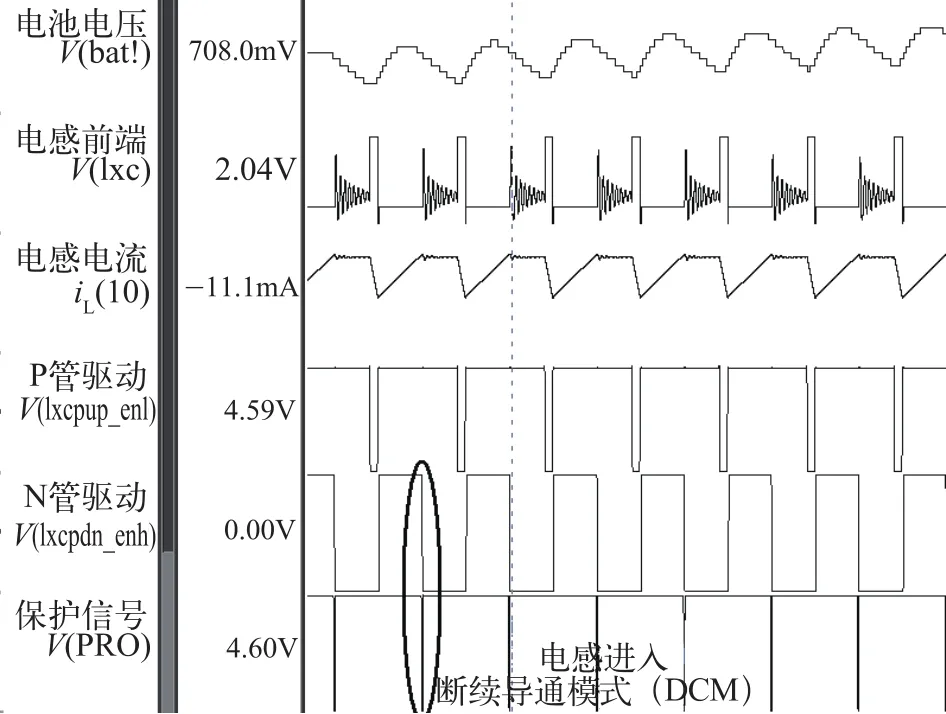

2.4DCM状态

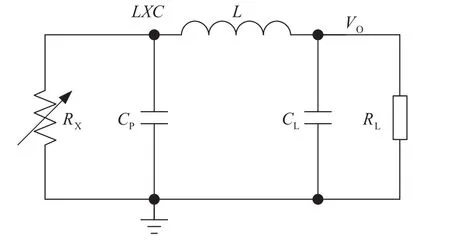

为了防止电感进入FCCM,获得非同步拓扑中二极管可以防止电感电流在调制周期的任意时刻变换电感电流方向的效果,需要在NMOS管导通PMOS管关断阶段检测LXC处的电压。当VLXC>0时,即电感上出现反向电流,产生保护信号将NMOS管关断,使电感进入断续导通模式(DCM),如图3(c)所示。电路工作于DCM对电池充电的仿真结果如图5所示。此时Buck电路包括3个阶段,t1、t2阶段与CCM类似,t4阶段时MP和MN均被控制信号关断,寄生电容CP没有到交流地的通路,CP与RL、CL、L构成LC振荡回路,等效电路如图 3(d)t4所示,由于CL>>CP,此时振荡频率为:

由于CP较小,fOSC通常较大,会在LXC处形成显著的振荡,如图 3(c)所示。如果电路在进入t4阶段时电感两端电压和流过的电流都恰好为0,那么LXC处于稳定状态, 不会出现振铃现象。在实际电路工作时, 很难同时保证这两个条件,所以存在一个趋向稳定的过程,可能出现不同的阻尼状态。此时较小的阻尼系数将会导致长时间的振铃现象。振荡的基波可能通过电感磁场或寄生电容传播到系统其他敏感(射频)电路中, 影响整体的功能。

图4 Buck电路FCCM模式对电池充电

图5 Buck电路DCM模式对电池充电

3 Buck型DC-DC中振铃现象的抑制

3.1Buck型DC-DC抗振铃设计的困难

为了使振荡尽快衰减, 可以通过减小电感的等效并联电阻实现,但对于 Buck型DC-DC,只有电感前端与芯片相连,所以不能采用上面的方法抑制振铃现象。Buck型DC-DC电路中,为了抑制振铃现象,最直接的手段是提高控制精度,使电感中残余的电流在N管关断时趋向于零, 但控制电路不易实现,并且抗振效果不理想。

3.2抗振铃设计的原理

为了抑制振铃现象,电路进入DCM的t4阶段时,可以在LXC和GND之间接入阻尼电阻RX,减小CP的并联电阻,如图 6所示。由于储能电容上的电荷会通过电感和电阻到地的通路泄漏,降低转换效率,所以在振铃结束后需要将电阻断开。较小的RX可以加快振荡的衰减,但RX断开时电感中还会残留较大的电流(峰值为VO/RX),导致RLC回路再次振荡;如果RX阻值偏大,那么振荡衰减会很慢,所以需要选取阻值合适的RX。

图6 抗振铃原理图

3.3具体电路设计

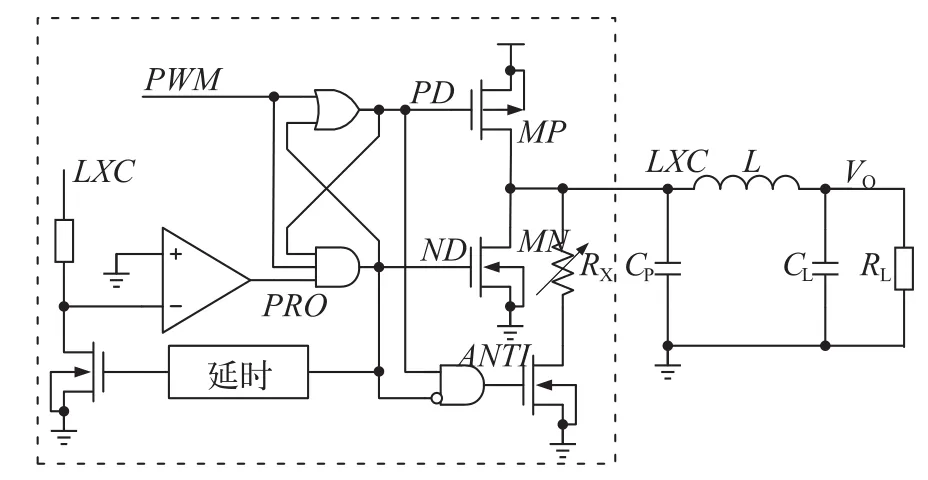

抗振铃电路的具体设计如图7所示。 Buck系统通过调制信号PWM产生开关MOS管的驱动信号PD、ND。当ND为高电平,NMOS管导通时,保护电路检测LXC电压,当VLXC>0时,通过比较器产生保护关断信号将MN强制关断,电路进入DCM。此时PD、ND分别为高和低电平,MP、MN同时关断,通过控制门产生抗振铃使能信号,将阻尼电阻RX接入LXC与GND之间,起到抗振铃作用。

图7 Buck电路抗振铃设计

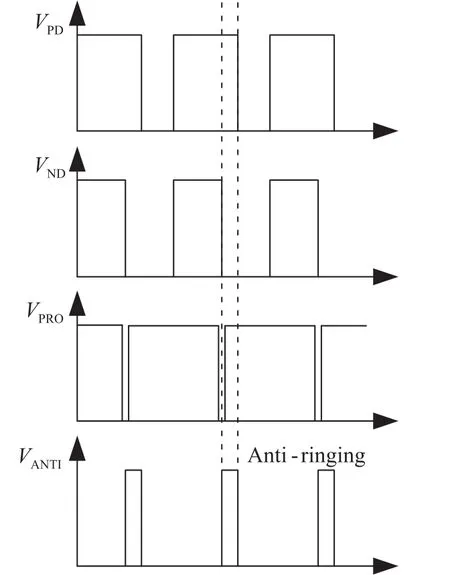

抗振铃过程时序如图8所示。当保护电路检测到VLXC>0时,产生保护信号PRO使ND为低电平,NMOS管关断,电路进入DCM,同时产生抗振铃使能信号,电阻RX接入LXC与GND之间,下一个调制周期开始后,抗振铃使能信号失效,防止电容通过RX对地放电。

图8 抗振铃过程时序

4 仿真结果

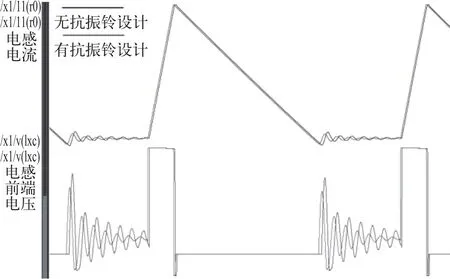

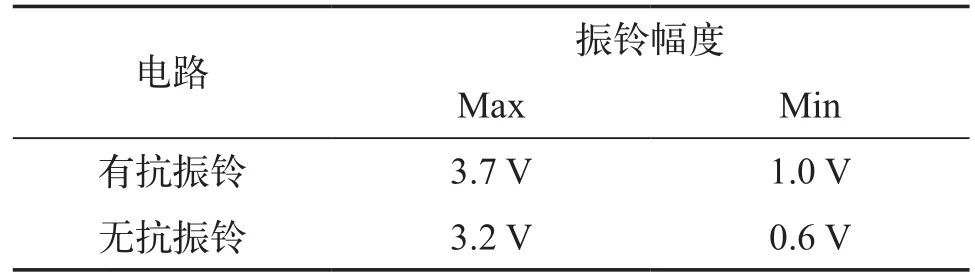

基于CSMC 0.5 μm CMOS工艺,设计了一款带抗振铃设计的Buck电路,振幅峰值可降低15%左右。采用Hspice软件对有、无抗振铃设计的Buck电路分别进行仿真,电感电流iL及电感前端电压VLXC的结果对比如图 9所示,可以通过抗振铃设计使电感电流及电感前端电压衰减明显加快,从而减小振铃现象对系统RF电路的高频噪声干扰。实际上,可以通过精确选择阻尼电阻RX获得更好的抗振铃效果。

图9 有无抗振铃设计仿真对比

有无抗振铃设计电路的振铃幅度对比如表 1所示。

表1 有无抗振铃设计振铃幅度对比

5 结论

本文提出一种用于抑制Buck电路振铃现象的设计方法,采用简单控制逻辑在DCM开关管关断时,将阻尼电阻RX接入LXC与地之间,加快振荡衰减。阻尼电阻选取的大小非常关键,需要根据系统对振铃噪声的要求及负载情况权衡优化,在起到抗振铃作用的同时,不能降低电路转换效率。

参考文献:

[1] Anthony John Stratakos. High-efficeency low-voltage DCDC conversion for portable application[D]. Dortor’s Thesis, University of California at Berkeley, 1998.

[2] Vattche Vorperian. Simplified analysis of PWM converters using model of PWM switch partI:continuous conduction mode[J]. IEEE Transactions on Aerospace and Electronic Systems,1990,25(5):490-496.

[3] 王红义,来新泉,等. 一种新颖的BUCK型DC-DC芯片的抗振铃电路[J]. 电子学报,2006,34(2):361-364.

[4] Sanjaya Maniktala著,王志强等译. 精通开关电源设计[M]. 北京:人民邮电出版社.

来鹏飞(1988—),男,山东莒县人,2010年获山东科技大学学士学位,2013年获南通大学硕士学位,就职于无锡中微爱芯电子有限公司,主要从事数模混合集成电路设计。

The Restrain of Ringing Phenomenon for Buck DC-DC Circuit

LAI Pengfei, CHEN Feng, CAO Fabing, Li Liang

(Wuxi I-CORE Electronics Co., Ltd., Wuxi 214072, China)

Abstract:The current of the inductor connected outside may drop to zero when the buck converter has a smaller load. In order to prevent the buck converter enter into FCCM and the current direction of inductor reversed which results in the discharge of the load capacitor through the free-wheeling NMOS and the reduction of the DC-DC conversion efficiency, we design the protection circuit detecting the voltage of the inductor frontend when the current dropped to zero. If the voltage is greater than zero, it forces to shut off the NMOS switch and the buck converter enters into DCM. The parasitic capacitor of the switch MOS form the LC oscillation circuit with the inductor outside and generate the ringing phenomenon. In order to restrain the ringing phenomenon, this article designs control circuit to insert a damping resistor to reduce the parallel resistor of the capacitor, which accelerates the attenuation of the oscillation.

Keywords:Buck converter; DC-DC circuit; anti-ringing; damping resistance

作者简介:

收稿日期:2015-9-22

中图分类号:TN402

文献标识码:A

文章编号:1681-1070(2016)02-0028-05