可远程控制的快速跳频源控制系统设计※

张琦,郭金丽

(1.空军预警学院,北京 100843;2.联发博动科技(北京)有限公司)

可远程控制的快速跳频源控制系统设计※

张琦1,郭金丽2

(1.空军预警学院,北京 100843;2.联发博动科技(北京)有限公司)

摘要:介绍一种以单片机和FPGA为核心的跳频源的控制单元。控制单元采用液晶触摸屏实现人工输入控制参数并显示对应的工作状态,同时可以通过串口与计算机通信,采用VC编程,实现人机交互控制捷变频源的工作方式并在液晶屏上显示。对实物的测试结果表明,该控制单元可以实现对跳频源的本地控制和远程控制。

关键词:超宽带;捷变频;MCU;FPGA;DDS

引言

作为微波电子系统的核心组成部分之一,频率合成器的应用范围非常广泛。频率源是构成雷达、通信等电子系统的关键部分,随着仪器仪表、遥控遥测通信、雷达、电子对抗、导航以及航空航天等技术的进步,系统对频率合成器也提出了越来越高的要求。

频率合成器在国外已经发展得比较成熟,形成了各种类型的锁相式整数频率合成器、锁相式分数频率合成器、直接数字频率合成器、双环或多环锁相式频率合成器、DDS与PLL混合式频率合成器等完整系列品种,满足了通信、数字电视等领域的需求,形成了巨大的频率合成器市场。而国内研究生产的单位不多,国内巨大的市场被国外产品所垄断。现有生产单位技术水平以及产品性能指标在一定程度上远不如国外限制出口的频率合成器产品,因此自主研制高性能的超宽带捷变频源来替代进口设备、突破其技术封锁具有重要意义[1-2]。

本设计中使用的跳频源以100 MHz恒温晶振作为DDS芯片AD9912的时钟信号,通过控制单元将频率控制字写入DDS内部的寄存器中,DDS输出一个频率在115 MHz附近的模拟正弦波,设置PLL的分频比,使其输出5~10 GHz的信号。PLL输出经过1/2/4/8分频器可以得到所需的2~18 GHz信号,通过倍频方式可以获得10~18 GHz频段信号。最后通过设置SP5T开关来控制信号通路以得到所需的不同波段的信号输出。

本系统中的跳频源原理框图如图1所示。

图1 跳频源原理框图

其中,系统时序控制、DDS控制逻辑、PLL分频控制以及波段选择开关等都需要由控制单元来实现,因此对于整个捷变频源系统来说,控制单元的设计至关重要。原有系统仅采用单片机来控制捷变频源工作,经过仿真和测试发现,单纯的单片机技术难以满足系统要求的速度和时间精度,所以本设计在原来的基础上进行改进,核心控制芯片采用集时序逻辑和控制功能于一身的FPGA。

1控制单元

1.1原理框图

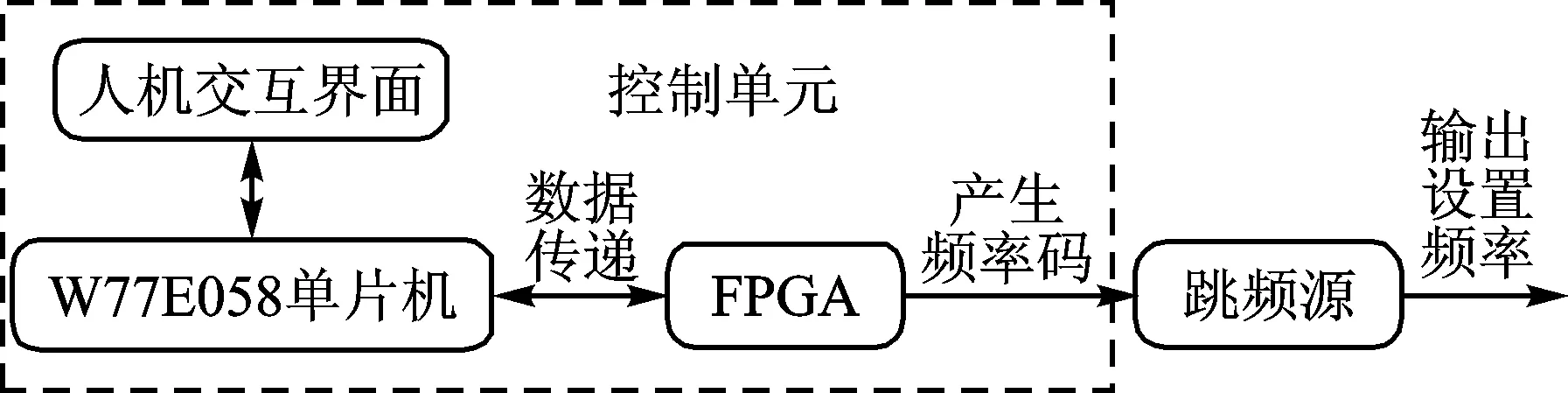

整个控制单元主要由人机交互界面、MCU以及FPGA构成,实现将面板设置或外部控制数据转换为对应的DDS控制逻辑和波段选择信号等功能。控制单元结构框图如图2所示。

图2 控制单元结构框图

人机交互界面包括本地控制端和远程控制端。本地控制端为一款串口液晶屏,远程控制端为基于VC编写的PC控制界面,二者的工作相互独立并且都是通过串口实现MCU之间的通信。

MCU为W77E058系列单片机,它与C51系列单片机兼容,而且增加了一个全双工串口,处理速度更快。W77E058主要完成人机界面交互,响应超宽带捷变频源面板设置,然后将数据以频率码的形式传递给FPGA。FPGA主要完成内外控制数据接口、控制数据转换、DDS控制逻辑、PLL分频控制和波段选择信号产生等功能。

本设计中主控制单元电路板实物图略——编者注。

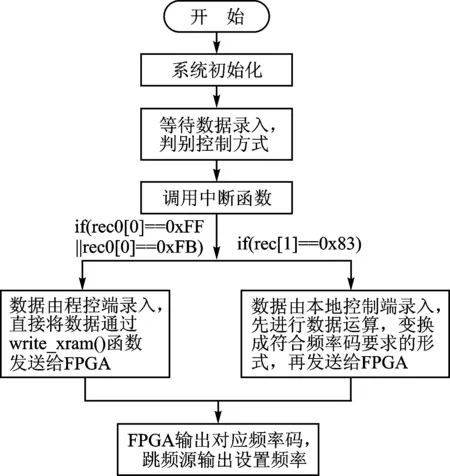

1.2工作流程

控制单元硬件电路搭建成功之后,需要进行软件设计。软件部分由主程序、串口中断子程序、系统初始化子程序、数据回传子程序、单片机读和写外部RAM子程序组成。

主程序的主要功能:系统初始化、数据换算及转发。主程序中的数据处理部分是最关键的,这里以点频控制为例,假设期望输出频率为2 GHz,其数据处理过程如下:

k0=((tempdata0/1000-1.9)×100000 +0.1);

其中tempdata0是通过控制界面输入的频率值,由于输入的频率值可以保留到小数点后3位有效数字,根据液晶屏的工作原理,串口实际接收值为2 000,故除以1 000,最终得到的k0为0.1×100 000,10 000即为2 GHz对应的频率码,然后再将k0拆分成字节形式传递给FPGA对应点频控制地址单元中。

bit0[0] = (k0 % 256);

bit0[1] = (( ( k0 - bit0[0] ) / 256 ) % 256);

bit0[2] = (k0 /65536);

在FPGA寄存器地址中,它们是以二进制形式存在的,这样就构成了21位频率码,其表示的最大频率码值为222-1=2.097 151 (MHz),2×10 kHz+1.9 GHz=21.9 GHz,使得输出频率能够满足2~18 GHz的宽频带范围要求。

串口中断子程序:在与远程控制端和本地控制端通信协议一致的前提下,接收通过串口0或串口1发送给单片机的数据[3],并对应存储在rec0[]、rec[]数组中。

系统初始化子程序:单片机和FPGA的初始化,主要是完成对定时器、串口相关寄存器的设置,FPGA置位和复位功能。其中,由于本设计中单片机程序代码过大,片内256字节缓存RAM空间不足,因此要使用1 KB片上数据SRAM,它受PMR寄存器控制。PMR寄存器的最低位DME0决定用户是否可以访问片上SRAM,该位复位后是0,置1后系统才可以访问片上SRAM[4]。因此在STARTUP.A51文件中,有如下初始化指令:

; Standard SFR Symbols

PMR DATA 0C4H

;sfr声明PMR电源管理寄存器

STARTUP1:

MOVPMR, #41H

;将PMR的第1位DME0置1

数据回传子程序:实现单片机到控制界面的通信功能。

单片机写外部RAM子程序:当通过控制界面输入数据时,数据传递给单片机,该子程序负责把转换后的数据传递给单片机的外部RAM,即硬件上与之相连接的对应FPGA各个寄存器的地址单元中,完成单片机到FPGA的单向通信。

单片机读外部RAM子程序:读取外部RAM寄存器单元中的数据,完成FPGA到单片机的单向通信。

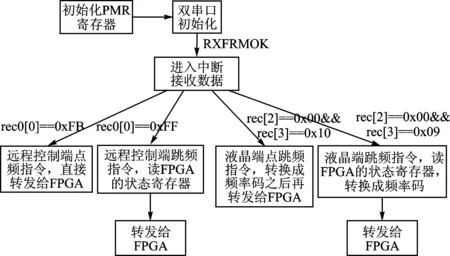

主程序通过while循环一直在检测是否有数据输入,若有,根据不同的指令形式判断用户使用的是哪种交互界面。PC端界面控制程序自身已对输入数据做出处理,故只需直接将数据转发给FPGA;若是本地控制输入端,则还需先进行数据处理,然后再转发给FPGA。整个程序流程图如图3所示。

图3 程序流程图

2人机交互模块

2.1本地控制端

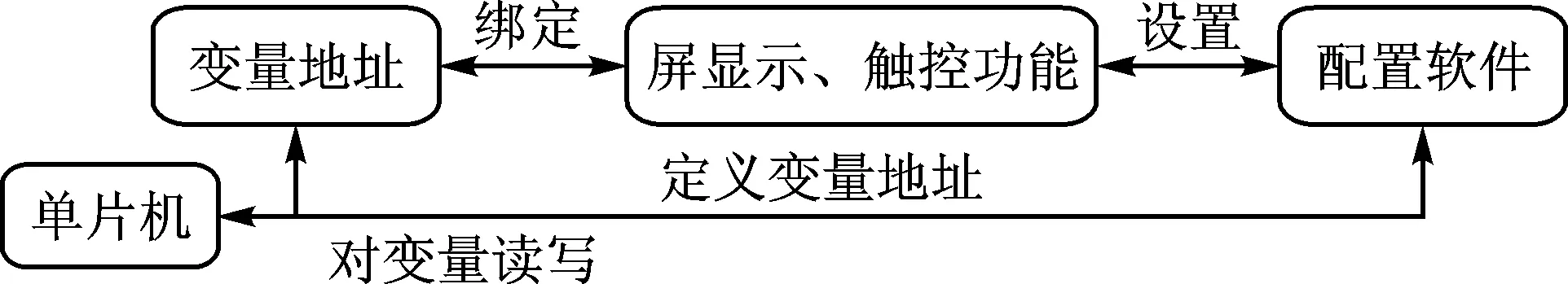

本控制单元中的液晶屏是人机交互的核心,同时也是软硬件交互的核心。通过触摸屏发送命令给单片机,调用内部的功能模块并完成相应动作,以达到控制要求。图4是液晶屏的控制原理图,使用配置软件将变量和需要实现的功能关联起来,然后通过控制端给该设置的变量赋值来实现对应的功能,或读取变量值来查看显示屏相关功能的当前状态。

图4 液晶屏控制原理图

液晶系统配置界面略——编者注,其中系统参数配置菜单用于设置液晶屏与单片机之间的通信参数,这里设置的波特率和单片机串口1的19 200 baud保持一致,首先设帧头为A5 5A,自动上传到串口模式,设置完成后输出配置文件,然后进行液晶界面设计,最后把界面配置文件以及图片等信息存储在SD卡中并下载到液晶中。用户端录入数据后,会自动上传到串口,经由串口2的RXD引脚将数据传送给W77E058。

2.2远程控制端

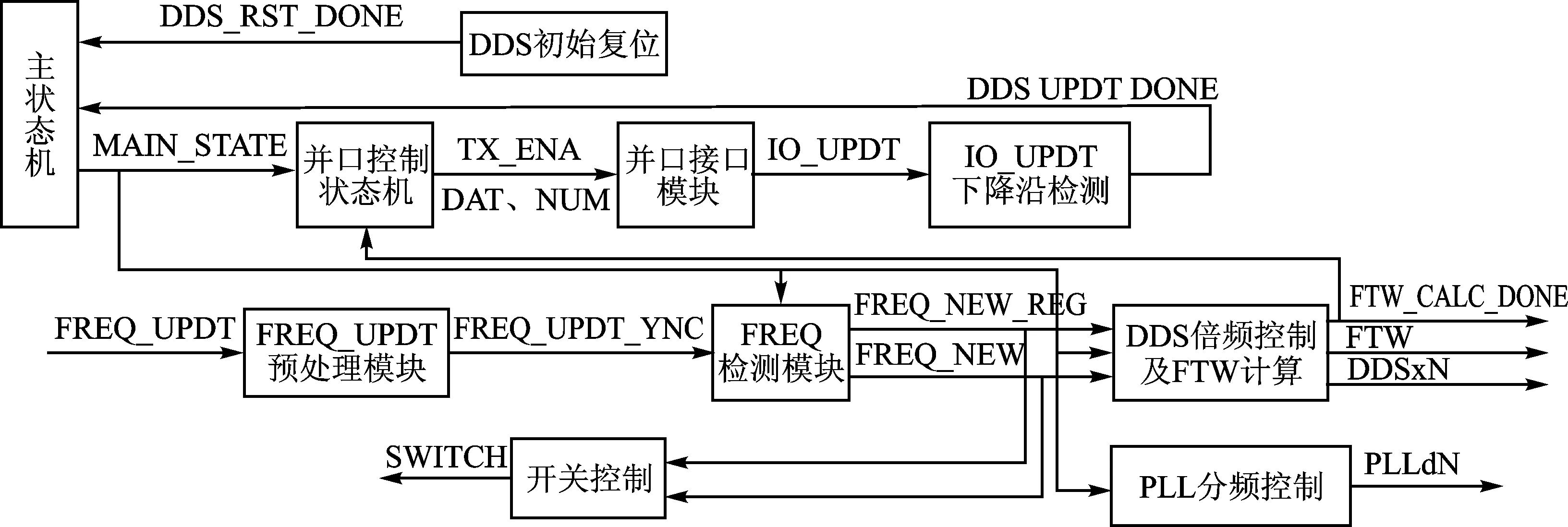

图6 FPGA对跳频源内部模块的控制过程

远程控制端是基于VC实现的,和本地控制类似,都要先进行界面设计,利用控件来创建显示界面,并且根据功能需求设置变量和函数。程序控制界面中主要函数有初始化、串口通信、点频及跳频数据处理、数据发送函数。点击确定按钮,即可把相关参数通过串口0发送给W77E058。远程控制端界面设计图略——编者注。

3单片机和FPGA工作原理

图5为单片机的主要工作原理,主要实现将设置数据转换成21位频率码传递给FPGA的功能。其中,当变频源处于跳频工作状态时,单片机在执行命令之前要先读FPGA的状态寄存器,只有等前一个跳频周期结束之后才能执行下一个跳频命令。

图5 单片机工作原理

跳变时间是捷变频源的一个关键性能指标,取决于DDS接口控制速度、波段开关切换速度和FPGA处理速度,实际跳变时间取决于FPGA处理及控制DDS时间。FPGA将外部控制信号转换为DDS所需控制信号并写入DDS控制字,总共需要600多个时序,工作于200 MHz的FPGA所需时间超过300 ns[5]。只采用单片机技术难以满足系统所要求的速度和时间精度,所以采用集时序逻辑和控制功能于一身的FPGA来满足设计要求。

本控制单元采用FPGA+MCU的结构实现,W77E058系列单片机和80C51兼容,该系列单片机技术成熟,开发简单[4]。FPGA采用Altera公司的Cyclone芯片,该系列芯片资源丰富、功能强大,工作频率为200 MHz,能够满足快速控制的要求。

FPGA的设计是整个控制单元的核心,首先FPGA要控制整个捷变频源系统的时序,其时序控制功能逻辑框图略——编者注。其次,FPGA要通过计算将频率码转换为对应的DDS频率控制字,再通过并口接口发送给DDS对应寄存器,同时相应更新DDS倍频数和PLL分频数以及波段选择开关的切换,即控制整个捷变频源频率的产生和跳变工作。FPGA对捷变频源内部模块的控制过程如图6所示。

频率控制字FTW的计算:首先根据频率码换算出的频率偏移码FREQ_NEW_REG,判断频率应该在43~87之间的哪一个倍频段内,从而确定DDS的倍频数DDSxN,然后根据下式求频率控制字FTW:

fpll=FTW×DDSxN×fc/2N

其中,FTW=FTW0+n×DFTW,故有:

fpll=(FTW0+n×DFTW)×DDSxN×fc/2N

其中,FTW0为每一个倍频系数DDSxN对应的起始频率值,可以根据fpll(M)=115×(DDSxN+0.5) MHz求得;n为刚更新的频率值对应的偏移码与倍频系数对应的起始频率值对应的偏移码之差;DFTW是最小跳频间隔10 kHz,由于10 GHz以上每跳10 kHz需要锁相环按5 kHz 跳变,所以要以5 kHz为最小单位进行频率跳变,因此DFTW×DDSxN×fc/2N=5 kHz,由此求出DFTW。

DDS倍频控制和频率切换点控制:

fpll=fdds×M

其中,fdds为DDS的中心频率(115 MHz),偏差不超过1.4 MHz。实际上,PLL若有5~10 GHz范围内的频率输出,根据M=[fpll/fdds],[]表示按四舍五入取整,计算可得M的取值范围为43~87。fpll=fdds×M=115×M+det×115 (MHz),取M=43~87,det=0.5,因此根据DDS的倍频数M,可以计算出DDS倍频对应的频率切换点,而每个频率切换点对应的偏移码可以根据下式计算得出:

Fcode(5 kHz)=(115×(M+0.5)-5 000)×200

PLL分频控制和输出5~10 GHz频率控制:根据输入频率码可以计算获得PLL的输出频率。PLL直接输出频率5~10 GHz,通过分频和滤波通道的倍频实现10~18 GHz频率范围的输出。频率切换点2 500 MHz对应的21位频率码为60 000,当输入频率码小于60 000时,PLL分频设置为4;同理切换点5 000 MHz时,分频设置为2,大于等于5 000 MHz对应的频率码,分频设置为1。然后将频率码换算成5~10 GHz之间,相对于5 GHz且以5 kHz为单位的频率偏移码FREQ_NEW_REG。由fdll=fdds×M,又fdds=FTW×fc/2N,其中fc=1 GHz,为DDS的时钟频率;N=48,为相位累加器位数;FTW为频率控制字;M为DDS倍频数DDSxN。因此,当输入频率码的偏移码FREQ_NEW_REG 4实测结果 使用频谱仪观察捷变频源的射频输出,软件中设置源的初始值为2.7 GHz,如果开机之后正常显示,说明控制板和捷变频源在硬件连接上是正常的。这里展示的实测结果以本地控制结果为例,测试结果表明,远程控制端和该控制结果是完全一致的。 点频输出控制:通过人机交互界面设置2~18 GHz之间任意一个频率值,而且小数点后可以根据需要保留不同的位数,本设计中小数点后保留3位。本文中以10 GHz点频的设置为例,控制端输入和输出界面略——编者注。 跳频输出控制:这里以6~14 GHz频段内的扫频为例,先设置100 kHz步进、250 μs重复周期对跳频功能进行控制,控制界面以及结果展示略——编者注。再将参数改成20 kHz步进,200 μs重复周期,观察结果略——编者注,对比发现若步长变小、周期变短,输出频谱成分更多更密,一个扫频周期用时更短。 实测结果表明,该控制单元能够在2~18 GHz的频率范围内,快速、精确地实现对捷变频源的控制,可以根据需求将频率精确到小数点后n位,跳频步长达10 kHz~2.55 MHz,脉冲重复周期达1~255 μs,而且这些参数可以根据系统指标要求灵活更改。 结语 本文设计了一种基于双串口单片机和FPGA的跳频源控制单元,为操作者提供了两种控制捷变频源的方法,用户可以根据自身需求选用合适的控制方式。测试结果表明,两个交互界面均可准确地完成数据录入工作,互不干扰,并且本地控制端和机箱是一体的,携带方便,具有较高的实用价值。同时FPGA和单片机在功能上互补,使得捷变频源能快速精确地实现频率跳变,高效完成对捷变频源系统的控制工作。实践证明,本控制单元性能稳定、操作简单,具有很好的应用前景。 参考文献 [1] 万天才.频率合成器技术发展动态[J].微电子学,2004,34(4):366-376. [2] Par k C H,Kim O,Kim B A.1.8 GHz self-calibrated phase-locked loop with precise I/Q matching[J].IEEE J Sol Sta Circ,2001,36(5):777-783. [3] 严平,雷津.基于W77E58单片机的无人机飞行安控器设计[J].航空电子技术,2007,38(2):46-49. [4] Winbond Electronics Croporation.W77E058 Data Sheet,2005. [5] 刘林,田进军,刘朝辉.基于DDS和直接频率合成技术的超宽带捷变频源设计与实现[J].兵工学报,2010,31(12):1648-1652. [6] 杨国渝,粟显义.采用DDS+PLL技术实现s波段频率合成的一种方法[J].电子科技大学学报,1999,28(4):388-391. [7] 张克舟,陆洪涛,施敏良.基于AD9910的宽带捷变频频率合成器设计[J].应用天地,2011,30(8):73-76. 张琦(硕士研究生),主要研究方向为电子与通信技术;郭金丽(硕士研究生),主要研究方向为电磁场与微波技术。 Design of Fast Frequency Hopping Source Remote Control System※ Zhang Qi1,Guo Jinli2 (1.Air Force Early Warning Academy of PLA,Beijing 100843,China;2.MediaTek (Beijing) Inc.) Abstract:In the paper,a control unit of the frequency agile sources based on MCU and FPGA is introduced.The LCD touch screen is used to achieve the functions of manual input control parameters and display the corresponding working state.At the same time,it can communicate with the computer through the serial port,using VC programming to achieve the function of human-computer interaction control the frequency agile sources,and the parameters can display on the control interface.The test results show that this kind of control unit designed in this paper can realize the local control and the remote control of the frequency agile sources. Key words:ultra-wideband;frequency agile;MCU;FPGA;DDS 收稿日期:(责任编辑:薛士然2015-11-10) 中图分类号:TN74 文献标识码:A