Virtex-6 FPGA的eMMC控制器设计

张耀军,孙铭,王锏

(西安电子科技大学 电子信息攻防对抗与仿真重点实验室, 西安 710071)

Virtex-6 FPGA的eMMC控制器设计

张耀军,孙铭,王锏

(西安电子科技大学 电子信息攻防对抗与仿真重点实验室, 西安 710071)

摘要:介绍了eMMC芯片的技术特点、工作原理,以及控制器的设计方案。该设计基于Xilinx公司的Virtex-6系列FPGA芯片,实现了控制器的设计方案,并给出了仿真结果,验证了该设计方案的可行性。此外,该设计均采用硬件逻辑实现,具有速度快、通用性强、可靠性高的特点。

关键词:FPGA;eMMC;控制器

引言

eMMC(embedded Multi Media Card)是由MMC协会所订立的,主要针对手机、平板电脑等便携式产品的内嵌式存储器。eMMC存储芯片的优势在于将NAND Flash和主控芯片封装成一个微型的BGA芯片,提供标准的接口并管理内存,不需要处理复杂的Flash兼容性和管理问题,使得应用厂商专注于产品开发的其他部分,从而缩短产品研发时间、降低研发成本。本设计是基于eMMC4.5(JESD84-B45)协议,并在FPGA(XC6VLX240T)上硬件实现,具有性能稳定、可移植性强、通用性好的特点,用户无需关注底层物理协议,而且操作简单。

1eMMC工作原理

1.1初始化

系统上电后,在eMMC能进行正常读写之前,必须按照协议规定的步骤完成初始化。 初始化过程如下:

① 复位进入Idle State的方式有两种:一种是通过Power On即上电进入,另外一种是通过发送命令CMD0。复位之后所有的寄存器都复位成默认值,此时CLK需要设置成fOD的范围,即0~400 kHz。

② 在Idle State发送命令CMD1,如果eMMC寄存器OCR回复值中的busy位为0,则上电复位仍未完成,需要一直发送命令CMD1,直到busy位为1且电压匹配,则进入Ready State。

③ 在Ready State发送命令CMD2,如果命令发送成功,则得到CID寄存器的值,而eMMC进入Identification State,若不成功,则eMMC状态不变。

④ 在Identification State发送命令CMD3,完成RCA地址分配,其中多片eMMC依靠分配不同的RCA地址来区分,进入Stand-by State,当eMMC芯片进入Stand-by State,不再响应命令CMD1、CMD2和CMD3。

⑤ 在Stand-by State,首先发送命令CMD9,获取设备寄存器CSD的值,可以得到如块长度、存储容量、最大时钟速率等。然后发送命令CMD7,通过参数中包含设备已分配的相对地址来选定设备,进入Transfer State。

⑥ 在Transfer State发送命令CMD6,其中包含切换工作速率的参数,将eMMC初始化低速时钟切换到正常工作的高速时钟。再次发送命令CMD6,其中包含数据位宽和单双沿模式的参数,默认模式是一位数据位宽和单沿模式,转换数据位宽和单双沿模式,此时eMMC停留在Transfer State,初始化工作全部完成。eMMC初始化流程图如图1所示。

图1 eMMC初始化流程图

1.2数据读

eMMC初始化完成后进入数据传输模式(即Transfer Mode),它是eMMC的工作模式, 在此模式下可实现对eMMC的数据读写。当没有数据传输时,DAT0~DAT7处于高电平状态,数据传输是以数据包为单位的,数据传输封包结构是一位开始位0,接着是数据流,包含了数据和CRC校验码,最后是一位结束位1,其中数据传输和时钟是同步的。数据基本的传输单元是Block,它的最大长度被定义在CSD中的READ_BL_LEN。

数据读分为单块读和多块读。单块读操作开始时,主机先发送CMD16(SET_BLOCKLEN)设置块长度,eMMC接收后再发送CMD17命令读取单块数据,单块数据读完成后自动返回Transfer State,等待下一次读操作。多块读操作开始时,主机同样先发送CMD16设置块长度,然后发送CMD23命令设置读取块个数,接着发送CMD18命令开始读取单块数据,每次单块数据读取完成则块计数加1,直到块计数等于预定块个数,多块读完成,返回Transfer State,进入下一轮读过程。其中须注意命令CMD17、CMD18设置读取块开始地址时,地址只有32位(4 GB),对于容量小于2 GB的芯片来说,地址即为每一位字节地址,对于容量大于2 GB的芯片来说,地址为扇区地址,每个扇区为512 KB。如果想要进行局部块读操作,则必须事先通过发送命令CMD9查看CSD寄存器中的READ_BLK_MISALIGNED和READ_BL_PARTIAL的值是否为0,若不为0,则系统不允许局部块读,读数据时,读出块大小必须为512 B或者CSD中READ_BL_LEN[83∶80]设置的值。eMMC数据读流程图如图2所示。

图2 eMMC数据读流程图

1.3数据写

写操作的数据传输格式与读操作相同,均由开始位、数据、CRC校验、结束位构成。eMMC有严格的数据写入检查机制,通过检查CRC校验位来判断接收到的数据是否正确,数据正确则允许写入,否则将被舍弃。数据写分为单块写和多块写。单块写操作开始时,主机先发送CMD16(SET_BLOCKLEN)设置块长度,eMMC接收并响应后,再发送CMD24命令写入单块数据,单块数据写完成后自动返回Transfer Stae,等待下一次写操作。多块写入方式有3种:开放式写入、块写入和可靠写入。其中前两种方式与可靠写入的区别在于后者具有数据的保护写入机制:其一是新数据未写入之前,原数据保持不变;其二是在编程过程中即使掉电数据也会保持有效。

在可靠性写入中,所有块长度均为512 KB,不受设置块长度影响,可靠性写入必须是与扇区对齐的,不能任意指定地址,如果没有对齐将终止写入操作。一般情况使用块写入方式,当多块写操作开始时,主机同样先发送CMD16设置块长度,然后发送CMD23命令设置写入块个数,接着发送CMD25命令开始写入数据,每次单块写入完成则块计数加1,直到块计数等于预定块个数,多块写完成后,返回Transfer State,等待下一轮写过程。与读过程一样,写过程也分写字节地址和写扇区地址,如果想要局部块写入操作,也必须事先通过CMD9命令查看CSD寄存器中的WRITE_BLK_MISALIGNED是否为0,若不为0,则系统不允许局部块写入,块写入时也要注意写入块必须与物理地址对齐。eMMC数据写流程图如图3所示。

图3 eMMC数据写流程图

2eMMC控制器设计方案

本文设计的基于FPGA的eMMC控制器包括初始化模块、传输控制模块、时钟模块、命令接口模块、数据处理模块、缓存模块。各模块功能如下:

① 初始化模块。初始化模块的主要功能是完成对eMMC的基本配置工作(如复位、电压匹配、RCA地址分配、时钟切换、数据位宽设置等)。

② 传输控制模块。传输控制模块主要是在eMMC读写操作时完成读写命令的发送、命令响应的对应处理以及数据CRC校验的比对,另外传输控制模块还要与上层用户交互。

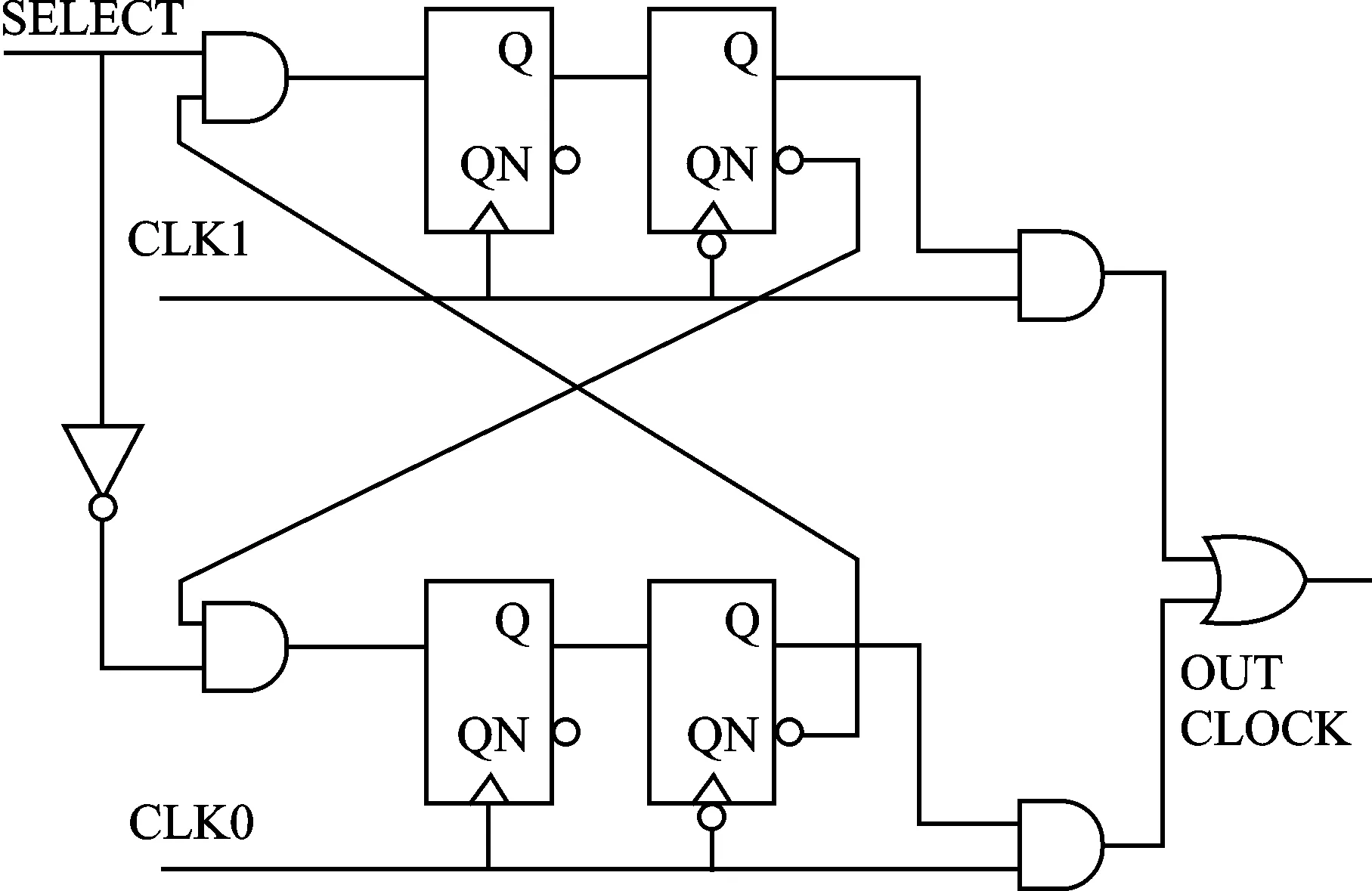

③ 时钟模块。由于eMMC芯片初始化时钟和工作时钟速度要求不同,所以时钟模块要提供时钟切换的功能,但简单的多路选择切换电路会产生毛刺,导致时钟不稳定,所以本文设计了防毛刺时钟切换电路,电路原理图如图4所示。

图4 eMMC防毛刺时钟切换电路图

④ 命令接口模块。命令接口模块的主要功能是将并行命令转换成串行命令发送给eMMC,接收eMMC响应的命令,并根据其响应的结果做出相应的处理。

⑤ 数据处理模块。数据处理模块的主要功能是通过eMMC的DAT接口读写eMMC数据,并对读写数据进行CRC校验。

⑥ 缓存模块。缓存模块是通过FPGA定制的FIFO IP核,暂存读写数据。

eMMC控制器各模块之间需要相互协同工作。控制器工作时,初始化模块发送一系列初始化命令给命令接口模块,命令接口模块将命令通过CMD(Inout型)信号线发送给eMMC芯片,此模块发送命令之后就等待eMMC芯片响应,根据响应命令来确定初始化流程状态,期间通过初始化的高速切换标志通知时钟切换模块切换到高速时钟,初始化完成之后,通知用户层可以开始进行数据传输;用户层向传输控制模块发送命令(如读写地址、读写块数、读写属性),然后传输控制模块解析上层用户的命令发送相应的读写命令给命令接口模块,而命令接口模块将命令转发给eMMC;当读数据时,eMMC将数据通过DAT接口发送给数据处理模块,数据处理模块将对读出的数据进行CRC校验,并将eMMC响应的CRC校验值和数据处理模块计算的值一起发给传输控制模块,在传输控制模块中对比CRC校验值,如果一致,则读取完成,将数据存储到缓存模块,然后传输给用户层,否则传输控制模块将重新发送读取命令,重新读取数据,直到CRC校验一致为止;当写数据时,用户层将数据暂存到缓存模块,缓存模块将数据传输给数据处理模块并计算CRC校验值,然后将数据封包发送给eMMC,eMMC内部将自动对比CRC校验值,如果一致,则写入eMMC,否则将被舍弃,并通过命令接口反映给传输控制模块,重新发送命令,直到CRC校验值一致则写入完成。多块读写重复以上读写过程,直到块数和预定的块数一致为止。eMMC控制器框图如图5所示。

图5 eMMC控制器框图

3仿真验证结果

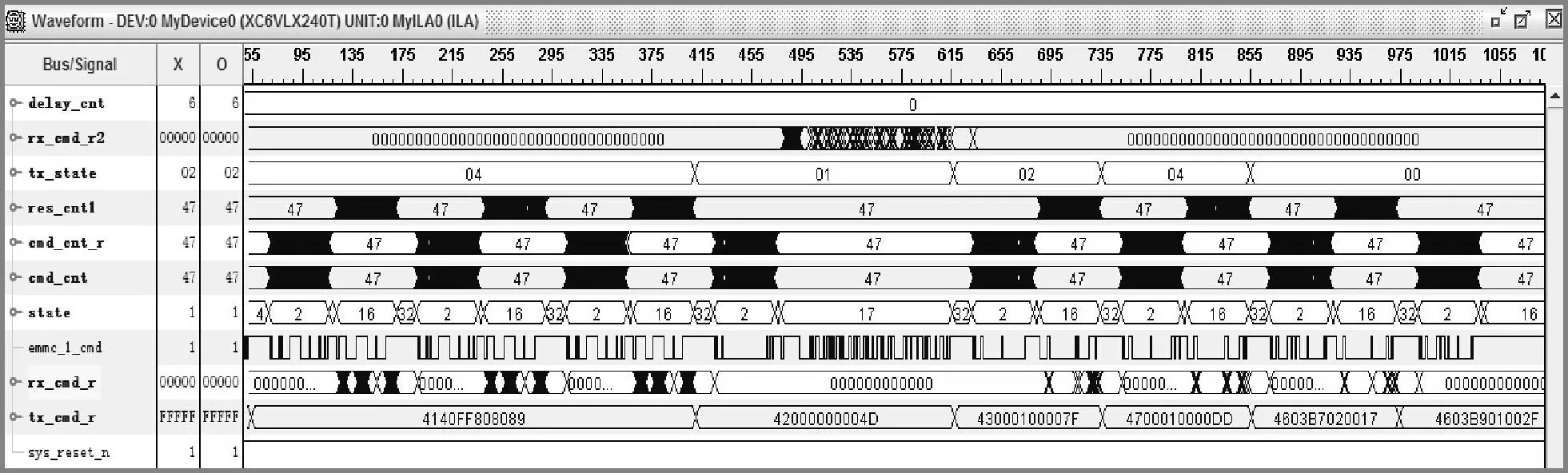

本文在Xilinx 集成开发工具ISE14.6开发环境下,用Verilog HDL硬件编程语言实现eMMC控制器的总体功能以及各模块功能,使用ISE在线逻辑分析仪Chipscope来仿真和验证控制器功能。仿真验证结果如图6~图10所示。

图6 eMMC控制器初始化过程

图7 eMMC控制器单块读

图8 eMMC控制器多块读

图9 eMMC控制器单块写

图10 eMMC控制器多块写

结语

通过对eMMC的技术特点和工作原理的分析,提出

参考文献

[1] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[2] 潘松,黄继业,陈龙.EDA技术与Verilog HDL[M].北京:清华大学出版社,2010.

[3] 刘常.数字逻辑电路[M].北京:国防工业出版社,2002.

[4] JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.JEDEC STANDARD eMMC specification[S].USA:JESD84-B45,2011.

[5] 曹军.安全SOC芯片中eMMC 主接口的设计与实现[D].沈阳:辽宁大学,2014.

[6] 胡文文.基于eMMC存储系统性能的研究和优化[D].北京:北京邮电大学,2012.

[7] 周杰,郝立燕,李建厂.基于FPGA的eMMC控制器及其工作方法:中国,103280238A[P].2013-09-04.

[8] 郑亮.SD/MMC控制器的设计与实现[D].厦门:厦门大学,2008.

[9] Xilinx Company.Virtex-6 FPGA Packing and Pinout Specifications.UG365(v2.4),2011.

[10] Xilinx Company.Virtex-6 FPGA Memory Resources User Guide.UG363(v1.6),2013.

张耀军(硕士),研究方向为基于FPGA的高速海量数据传输与存储;孙铭(硕士),研究方向为基于FPGA的电子系统设计;王锏(硕士),研究方向为基于FPGA的海量数据传输。

TI为中国互联网企业带来创新物联网解决方案

TI与腾讯、百度、阿里巴巴及京东四家中国领先的互联网企业建立了IoT合作伙伴关系。通过久经行业验证的低功耗和超低功耗SimpleLink线MCU产品组合,TI针对四家企业的不同IoT应用提供了多种创新的无线连接解决方案。SimpleLink产品组合包括面向广泛嵌入式市场的无线MCU、无线网络处理器(WNP) 、RF收发器和距离扩展器,能够简化IoT应用的开发并轻松实现万物互联。凭借对Bluetooth Smart、Wi-Fi、Sub-1 GHz、6LoWPAN、ZigBee等多达14项无线连接标准的支持,该产品组合可帮助生产商将无线连接功能轻松添加至任何产品和设计中,并满足所有的应用需求。

作为此次TI与腾讯的合作项目之一,微信将指定TI作为其Bluetooth Smart以及Wi-Fi芯片的供应商,其终端用户可以在TI的无线芯片上实现AirKiss和AirSync协议,并接入腾讯推广的微信硬件平台。未来,微信还希望将其合作论坛的一部分权限开放给TI,让TI的技术工程人员能够在论坛上为开发者提供支持,共同打造更多的创新应用。

eMMC Controller Design Based on Virtex-6 FPGA

Zhang Yaojun,Sun Ming,Wang Jian

(Key Lab of Electronic Information Countermeasure and Simulation,Xidian University,Xi’an 710071,China)

Abstract:The technical characteristics,working principle of the eMMC chip,and the design of the controller are introduced.The design is based on Xilinx Virtex-6 series FPGA chip,and the simulation results are given.The test verifies the feasibility of the design.In addition,the design adopts the hardware logic,which has the characteristics of high speed,strong commonality,high reliability.

Key words:FPGA;eMMC;controller

收稿日期:(责任编辑:薛士然2015-08-24)

中图分类号:TP37

文献标识码:A