12位低功耗高精度SAR ADC的研究与设计

北京理工大学信息与电子学院 洪 祥 杨晨晨 张晓洁

12位低功耗高精度SAR ADC的研究与设计

北京理工大学信息与电子学院 洪 祥 杨晨晨 张晓洁

本文基于0.18um CSMC CMOS 1P6M工艺,设计了一种12bit高精度低功耗的SAR ADC。该设计采用全差分结构、栅压自举开关等方法提高精度,使用同步时钟、传输门的触发器和“部分单调开关”的整体结构降低功耗,并抑制了共模失调。本设计中使用Aether软件,完成了电路的结构设计、仿真以及版图设计。设计的后仿结果能够在采样频率280KHz,输入53KHz正弦波的情况下,信号SNR为66.891dB,SFDR为77.79dB,有效位数10.826位。INL为±0.53LSB,DNL为±0.16LSB。总电流为56uA,不考虑reference电流为40uA,芯片核心面积为836.015um X 603.665um。

全差分;栅压自举开关;同步时钟;部分单调开关

1. 引言

随着计算机和微电子技术的高速发展,片上系统(SOC)成为当前CMOS技术的主要发展方向。数字信号处理技术凭借成本低、规模大的优势得到了飞速发展。但来自于自然界的信号大都是模拟量,在模拟信号和数字信号之间就必须存在转换接口。

模数转换器(ADC)就是将模拟信号按照一定的编码规则转换为数字信号的接口电路,只有通过它,SOC才能对外界模拟信号进行采集和处理。因此,随着高速信号处理应用的不断增加,模数转换器也向着高速高精度方向发展,以满足无线通信、高速信号处理等领域的要求。在多种不同的ADC架构中,逐次逼近式模数转换器(SAR ADC)具有功耗低,面积小,高度数字化,转化延迟小的优点,通常用于低功耗中低速中高精度的应用场合,是目前ADC的热门技术。本文研究重点是低功耗高精度的SAR ADC。

2. SAR ADC的原理

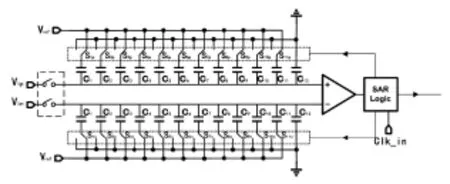

图2-1中给出了SAR ADC电路模块的框图,包括采样开关、比较器、DAC电路和逻辑控制单元,由采样开关对输入信号进行采样,采样后的电平保持在DAC的上极板,采样信号被送入比较器,控制逻辑根据比较结果控制DAC下极板开关,依据比较结果逐位确定模拟信号对应的数字码,最后使得DAC的输出在最高精度范围内逼近模拟输入。

图2-1 SAR ADC 结构框图

信号转换过程如图2-1所示:

图2-2 SAR ADC信号流程图

将模拟信号输入VIN、VIP,被采样开关采样,转换周期开始。采样信号首先被送至比较器,比较大小后输出比较结果,控制逻辑依据此结果切换DAC最高位的值,如果VIN>VIP,则N端电压变为VIN-0.5Vref,N端MSB确定为1。转换的第一步完成,接下来重复上述流程,直到最低位被确定,SAR ADC完成一次逐次逼近转换。

3. SAR ADC的结构与实现

3.1 栅压自举开关

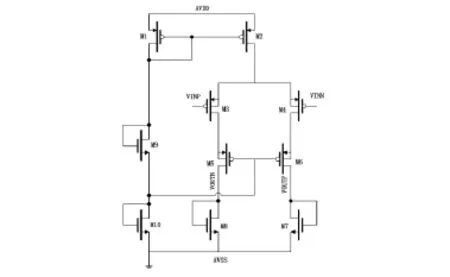

采样保持电路对模拟输入信号进行瞬时采样并保持,作为SAR ADC的前端模块,其性能对整体信噪比、线性度、直流失调等参数有重要影响。本文采用栅压自举开关结构,导通管的栅极电压能够跟随输入电压的变化,即导通电阻不受输入电压的影响,有效地提高了开关的线性度,改善了采样保持电路的性能。

电路结构如图3-1所示:

图3-1 栅压自举开关

工作过程如下:时钟信号CLK为低电平时,由M3和M4组成的反相器输出为高电平,M6导通,电容一端接低电平,同时M8、M9也导通,节点n3接低电平,PMOS管M5导通,电容被充电到VDD,M1导通,M7因栅极接高电平截止,开关处于断开状态。当时钟信号跳变到高电平时,反相器输出为低电平,M6、M9截止,M2导通,M7的栅极连接到节点n2,其栅源电压为-VDD,管子导通,节点n3接高电平,M5截止,M10导通,节点n1、n3的电平被抬升到VDD+Vin,开关处于导通状态,其栅源电压为VDD,实现栅压自举功能。此结构的信噪比可达79dB,有效位可达12.90位。

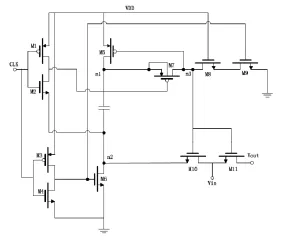

3.2 预放大与比较器

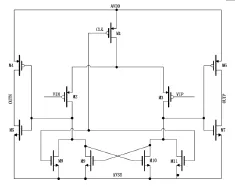

预放大电路是比较器的前级电路,主要作用是提高动态锁存比较器的分辨率并减小回踢噪声。设计时,需要将输入共模范围、输出摆幅、共模抑制比、电源抑制比和功耗等因素综合考虑。由于比较器是模拟输入、数字输出的器件,数字信号会干扰模拟输入,因此通过共源共栅结构高输出阻抗的特性,一定程度上屏蔽了放大器输出端信号对输入模拟信号的影响。原理图如图3-2所示:

图3-2 预放大电路原理图

比较器是SAR ADC系统中最重要的模拟模块,分辨精度至少为1/2个LSB的电压,失调电压也要控制在1/2个LSB以内。本文设计的ADC具有12位精度,量化量程为1.8V,因此分辨精度为220V。采用预放大锁存比较器,将输入信号经一级预放大,放大后再由锁存器进行比较,以节省静态功耗,并满足高精度的要求。锁存器通过正反馈将输入信号以指数形式快速放大,原理图如图3-3所示:

前级预放大的输出通过PMOS管M2、M3输入,M9、M10构成正反馈结构,后面通过一级反相器将结果输出。时钟信号CLK为高时,M1截止,M8、M11导通,把电路中相应节点的电压强制拉至低电平;CLK为低时,M1导通,输入信号通过正反馈被迅速放大锁存。

前仿比较器精度可达到100V,后仿可达到200V。

图3-3 比较器原理图

3.3 DAC电路

DAC的线性度直接影响了整体电路的转换精度,DAC的误差主要来源于两个方面,一是寄生电容及干扰,二是电容的匹配精度。

对于DAC而言,较大的单位电容有助于减小寄生和失配带来的影响,但会导致功耗增加,版图面积增加,综合电路的要求以及CSMC的工艺文档,我们取单位电容C=400fF,w=20u,l=20u。

由于电容个数与位数成指数关系,直接利用电容构造12位DAC是不可行的,必须引入分段结构,分段电容的容值一般是分数,在我们的电路中。通过对电容阵的整体仿真,虽然可以利用单位电容的串并准确的构造出分数电容,但走线复杂、寄生难以控制,由此引起的误差反而使其得不偿失,最终,我们将一个稍大的电容做为分段电容,将其边长设置为w=l=20.16u,电路整体结构如下图所示:

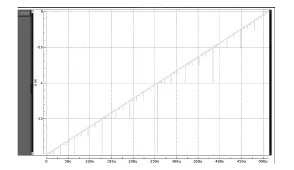

通过将不同的置位信号赋值到DAC下极板,仿真结果如下图所示:

图3-4 DAC电路仿真结果

可以看到电路完成了DAC的基本功能,完成了数字到模拟信号的转换。

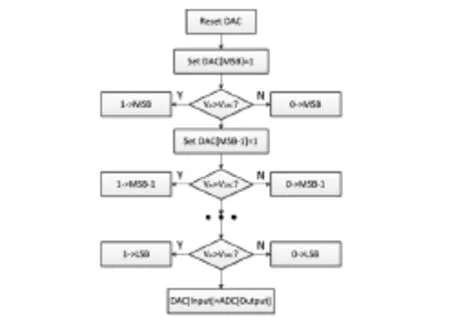

3.4 逻辑控制单元

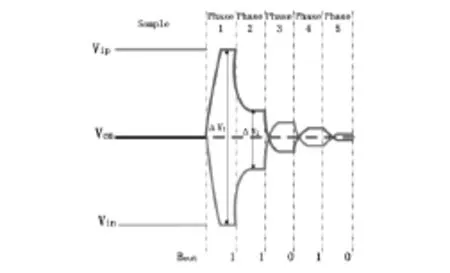

逻辑控制单元的主要功能是根据比较器返回的比较结果,在相应的时钟沿到来时切换开关,DAC的下极板设置为VREF或0。切换开关时需要考虑开关的切换策略,传统的切换过程如图3-5所示,由于差分端信号都需要切换,功耗较大,为了降低功耗,我们采用单调开关的切换策略,如图3-6所示。

图3-5 传统开关切换方式

图3-6 单调开关切换方式

图3-7 部分单调开关切换策略

单调式开关在转换过程中差分两端的信号会逐渐降低,引起比较器的共模失调,影响SAR ADC的SFDR(无杂散动态范围),为减小共模偏移的影响,我们采用“部分单调”的开关策略,在最高位MSB将较小的一端上拉,其他位下拉,这样共模电平的偏移最小,转换过程如图3-7所示。

由于电路中同时存在“上拉”“下拉”两种不同的操作,需要有两种不同的逻辑控制单元,电路如图3-8、3-9所示。

图3-8 上拉控制单元

图3-9 下拉控制单元

上拉单元工作原理如下:当时钟为低时,与非门输出为“1”,置位端C1为模拟地AVSS,当比较结果到来时,由触发器将结果输送到B1,如果比较结果“1”,经过反相器变为“0”,结果保持不变;若比较结果为“0”,经过反相器变为“1”,与非门输出“0”,置位端C1为VREF,完成上拉动作。下拉单元工作过程和上拉单元相反。

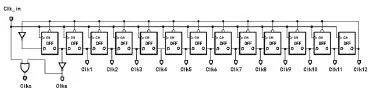

控制单元中还包括整个电路的时序的产生,时钟信号产生电路主要功能是根据输入时钟信号,产生控制采样开关、比较器,以及各个时序开关的时钟信号,其原理框图如图3-10所示:

图3-10 时序电路框图

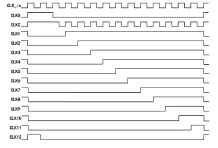

简单的时序分析可知,电路将产生如图3-11时序:

图3-11 时序逻辑图

其中,采样时钟clks为2个clk周期采样,12个clk周期保持,比较时钟clkc也保持两个周期静止,其后12个周期依次比较。

4. 仿真结果与版图

4.1 仿真结果

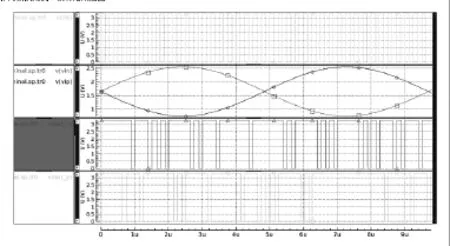

各子模块搭建完毕后,按框图将各个子模块连接起来进行仿真,利用频率103.2KHz,幅度1.8V的正弦波作为测试用例。仿真结果如图4-1所示:

图4-1 SAR ADC瞬态仿真结果

将仿真结果导出,重建波形后分析频谱,结果如图4-2所示:

图4-2 仿真结果频谱分析

软件分析结果为SNR=70.913dB,SFDR=80.857dB,有效位数ENOB=11.438。

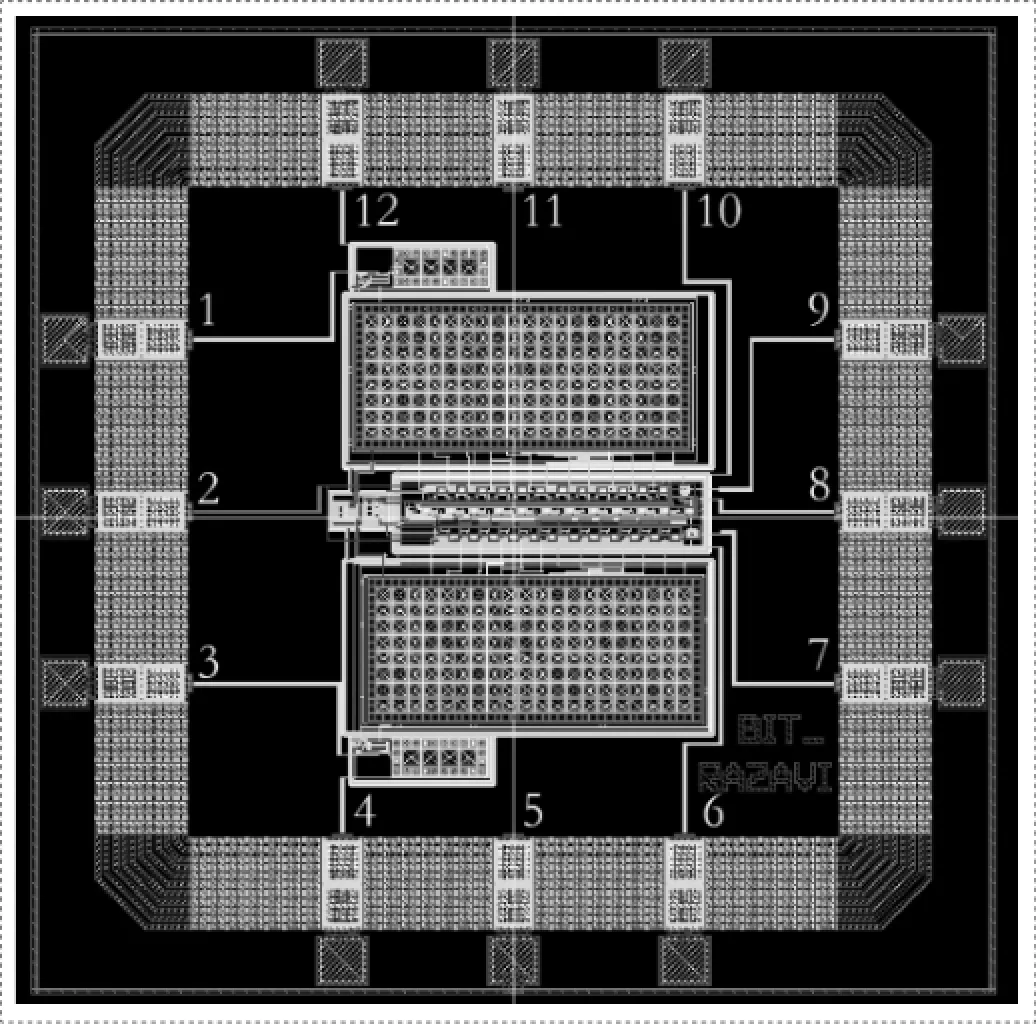

4.2 版图设计

前仿实现功能后我们开始准备版图,首先对版图进行整体规划,如图4-3所示:

图4-3 整体版图布局

由于SAR ADC是混合信号电路,同时包含数字部分和模拟部分,在整体考量时应尽量减小数字部分对模拟部分的干扰,通过上述布局可实现模拟模块和数字模块的隔离,使关键信号线上没有交叠。整体版图如图4-4所示。

图4-4 SAR ADC整体版图

5. 结论

本次设计采用0.18um CSMC CMOS 1P6M工艺,通过Aether软件仿真验证了12位280KS/s的低功耗SAR ADC芯片。本设计采用了部分单调的开关策略,在降低功耗的同时不影响无杂散动态范围。设计的后仿结果能够在采样频率280KHz,输入53KHz正弦波的情况下,信号SNR为66.891dB,SFDR为77.79dB,有效位数10.826位。INL为±0.53LSB,DNL为±0.16LSB。总电流为56uA,不考虑reference电流为40uA,芯片核心面积为836.015um × 603.665um,添加I/O PAD后总面积为1508um × 1508um,达到了设计要求。

[1]卢宇潇.高速低功耗逐次逼近式ADC研究与实现[D].上海:上海交通大学, 2014. 60-75.

[2]Chun-Cheng,Liu.Design of High-Speed Energy-Efficient Successive-Approximation Analog-to Digital Converters[D]. Taiwan,CN:National ChengKung University,2010.22-90.

[3]黄海.低压、低功耗、高精度的逐次逼近型ADC设计[D]. 成都:电子科技大学, 2013. 31-67.

[4]郝乐.基于低电压高精度的12-bit SAR ADC设计[D]. 北京:北京交通大学, 2008. 27-55.

洪祥(1993—),安徽马鞍山人,硕士研究生,现就读于北京理工大学。

杨晨晨(1994—),陕西咸阳人,硕士研究生,现就读于北京理工大学。

张晓洁(1993—),湖北荆州人,硕士研究生,现就读于北京理工大学。