一种低功耗CMOS带隙基准电压源设计

武汉大学物理科学与技术学院 汤知日 周孝斌 杨若婷

一种低功耗CMOS带隙基准电压源设计

武汉大学物理科学与技术学院 汤知日 周孝斌 杨若婷

本文设计采用的是CSMC 0.18um的标准CMOS工艺技术,利用MOS管代替现有基准源电路中的电阻从而达到减小功率的目的,并且利用两类不同电压各自的温度系数相反,使得输出总电压的温度系数得到补偿,极大地降低了输出基准电压的温度系数。仿真结果表明,该电路在1.5V的电源下,在-40~90℃之间,可以实现电路快速启动,并且输出基准电压为0.5996686V,温度系数为17.254ppm/℃,线性度为430.8ppm/V,启动时间约为70us,功耗仅为217nA,版图面积约为0.0495mm2。

CMOS工艺;基准电压;温度补偿;快速启动

0 引言

在如今集成芯片规模越来越大的信息化社会中,特别是SOC系统中,功耗已经成为一项与性能、面积同等重要的指标,低功耗产品的设计会带来许多便利[1]。带隙基准模块是绝大多数SOC系统都需要用到的模块,用来提供稳定的电压或者电流输出,它的性能影响着整个系统工作的性能。随着人们对于电子产品要求的逐渐提高,低功耗基准电压模块的设计已成为必然。

本次基准带隙电压源的设计基于CSMC 0.18um的标准CMOS工艺,设计了一种工作在亚阈值区的极低功耗的CMOS带隙基准源电路,包括启动电路、差动放大器、电流源子电路以及偏置电压子电路。本设计不包含双极性晶体管和电阻,在减小面积的同时也极大地降低了功耗。

1 电路原理

本设计是利用MOS管工作在亚阈值区的特性构成的。当MOS管的栅源电压小于阈值电压,但是足够在硅表面形成耗尽区时,MOS 管工作在亚阈值区[2]。具体在当Vds较大时,工作在亚阈值区的MOS管的电流电压特性如下:

本设计带隙基准源的原理电路分为启动电路、核心电路和偏置电压子电路三大部分,其中核心电路由一个放大器和电流源子电路组成[3],如图1所示:

图1 带隙基准源电路原理图

电流源子电路采用自偏置的技术,用一个工作在深三极管区的MOS管电阻MR1代替传统的电阻R,产生一个电流Ip,偏置电压子电路通过PMOS电流镜电流,并且产生一个基准电压的输出偏置电压子电路由一个MOS管和两个源极耦合对构成。在偏置电压子电路中M3~M7的栅极和源极两极电压和电流源子电路中的MR1构成了一个闭环的形式。除了MR1所有的MOS管都工作在亚阈值区。

上式给出了VREF与栅源电压 VGS4、热电压 VT以及晶体管尺寸比的关系。其中,η=1+Cd/COX是亚阈值斜率因子,K3、K4、K5、K6和K7分别是M3、M4、M5、M6和M7管的宽长比。阈值电压与温度系数的关系式为:

其中,VTH0是绝对温度为 0 K 时的阈值电压,κ是VTH的温度系数。从上面可以得到,阈值电压 VTH与温度成反比例关系,热电压 VT与温度成正比例关系。因此可以通过调整晶体管的尺寸将上面两式所表产生的正、负比例效果相抵消,得到零温度系数的输出电压

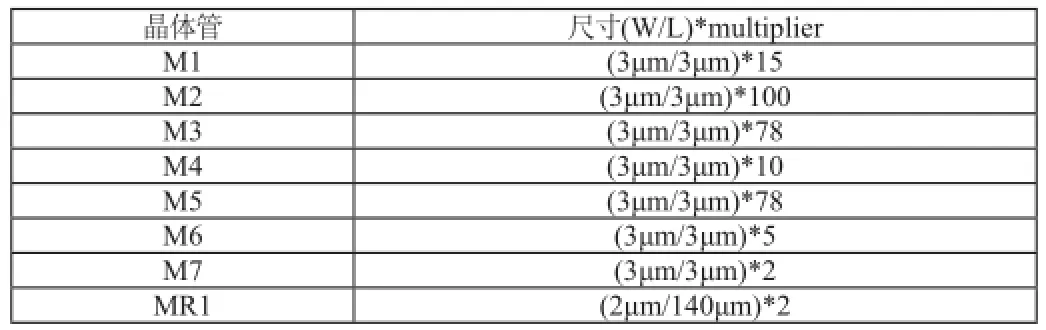

该电路中各个主要晶体管的宽长比由表1给出:

表1 电路主要晶体管参数

2 电路仿真

2.1 温度系数

在1.5V电压驱动下,从-40到90℃进行温度扫描,TC仅为17.25ppm/℃。其中在t=27℃,VREF=0.5996686V 。温度扫描波形如图2所示:

图2 温度扫描波形图

2.2 电源抑制比(PSRR)

在1.5V电压驱动下,加入1V的噪声干扰,仿真结果为:在0Hz时,电源抑制比为67.39dB,在1KHz时,电源抑制比为58.31dB,如图3所示。

2.3 启动时间

电源驱动经过5us上升到1.5v,整体电路启动时间约70us,如图4所示。

2.4 功耗

在1.5V的驱动电压下,功耗电流仅为217nA,功率仅为325nW。

图3 电源抑制比波形图

图4 启动时间波形图

2.5 不同工艺角下性能参数对比

在相同1.5V电压下,电路在不同工艺角下的参数总结,如表2所示:

表2 不同工艺角下的仿真参数

3 电路版图

在版图布局中,将每个模块都独立分开,分别进行版图的绘制;再结合设计经验,将NMOS衬底接地,PMOS衬底接高电压,版图最外围为地线,方便各模块接地需要。版图设计如图5所示:

图5 整体版图

其中,MR1的版图为了匹配尺寸改为并联结构,节约了空间。此外,根据Aether软件提供的网格数据可以得到,该设计版图的整体电路面积约为0.05mm2(263um*188um),满足设计要求。

4 电路后仿真

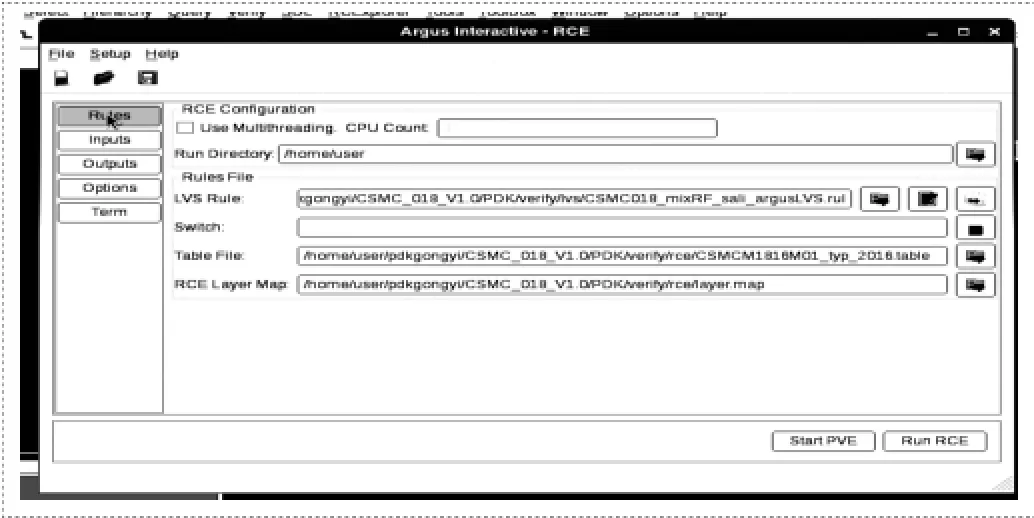

在RCE界面设置用于后仿真的配置文件如图6所示:

图6 寄生参数配置文件

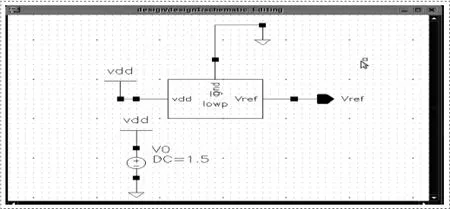

RCE参数提取后,创建一个symbol进行电路的后仿真,如图7所示:

图7 后仿真电路图

后仿完成后将结果与前仿对比,其结果近似相同,表明版图的布局匹配很成功。前仿与后仿的结果比较如表3所示:

表3 前仿与后仿结果对比

5 结论

本文采用CSMC 0.18um的标准CMOS工艺技术,仿真结果表明,在1.5V的输入电源下,-40~90℃之间,该设计可以实现电路的快速启动,启动时间约为70us,且输出基准电压为0.5996686V,温度系数为17.254ppm/℃,线性度430.8ppm/V,功耗仅为217nA,版图面积约为0.05mm2。

[1]吴文兰,邢立冬.带隙基准源的现状及其发展趋势[J].微计算机信息,2010,26(6):186~188.

[2]赵玉迎,厚娇.低功耗CMOS带隙基准源[J].电子世界,2015(23):27~30.

[3]张小莹.低压低功耗CMOS带隙基准电压源设计[D].西安:西安电子科技大学硕士,2009:29~32.

[4]王国瑞.高性能带隙基准电压源的分析与设计[D].吉林:吉林大学硕士,2010:32~37.

[5]瞿美霞.CMOS带隙基准源的研究与实现[D].合肥:合肥工业大学,2007:1~2.

This design uses CSMC 0.18um standard CMOS process technology, which use MOS instead of resistance in the existing voltage reference circuit to achieve the purpose of reducing power. What’s more, it uses opposite temperature coef fi cient of two different voltage types to make temperature coef fi cient of total output voltage compensated and to reduce the temperature coef fi cient of output voltage reference greatly. The simulation results show that it can implement quick start in the 1.5V between -40~90℃ and output voltage reference is 0.5996686V, temperature coef fi cient is 17.254ppm/℃, linearity is 430.8ppm/V, start time is about 70us, power consumption is only 217nA, the layout area is about 0.0495mm2.

CMOS process; voltage reference; temperature coef fi cient; quick start

汤知日(1994-),男,安徽芜湖人,大学本科,现就读于武汉大学物理科学与技术学院。

周孝斌(1994-),男,浙江绍兴人,大学本科,现就读于武汉大学物理科学与技术学院。

杨若婷(1994-),女,四川成都人,大学本科,现就读于武汉大学物理科学与技术学院。