超低功耗高精度电压基准设计

吉林大学 王仁广 李捷菲 宫浩然 纪永成

超低功耗高精度电压基准设计

吉林大学 王仁广 李捷菲 宫浩然 纪永成

本文设计了一款适用于超低功耗SoC的高精度电压基准模块。本次设计的电压基准模块创新性的使用了工作于亚阈值区的MOSFETs来代替传统的电路结构。除了用做电阻的工作于线性区的MOS管之外,其余所有的MOS管均工作在亚阈值区。仿真结果表明,整体电路(包含启动电路)的功耗仅为210nA,电路版图面积仅为70,在0.7~1.8V的电源电压范围内,电路都能正常输出大小为630mV的基准电压,在-40~125温度范围内,温漂系数TC为16ppm,在1kHz带宽范围内的电源抑制比PSRR接近50dB。在电源上电以后,电路可以10s内快速稳定的启动。

超低功耗;高精度;超小面积;全亚阈值;电压基准模块

引言

基准电压是所有模拟电路中不可缺少的模块,在大规模集成电路中有着广泛的应用。随着可穿戴电子设备的普及,对内部电子芯片也提出了更高的要求,超低功耗、超小面积成为了一种趋势。工作在亚阈值区的MOSFETs能够很好地满足要求。因此本文提出了一款适用于超低功耗SoC的高精度电压基准模块。相比于传统的带隙基准结构,在面积和功耗方面有着巨大的优势。

1. 电路原理介绍

基准参考电压产生电路的整体架构如图1所示,左半部分为启动电路,右半部分为基准偏压产生电路。除了MOS管之外,电路中所有的晶体管都工作在亚阈值区。该电路通过将两路具有相反温度系数的电压加和来获得具有近零温度系数的基准参考电压。

图1中左侧启动电路的工作原理为:在电源上电时,基准电压为低电平,此时管和导通,将的栅端电压拉高使得管导通,从而和的栅压被拉至低电平,此时参考电压产生电路开始工作,启动电路失去作用。

图1中右侧为基准电压产生电路。M3~M6为cascode结构,将和的漏端电压钳位在相同电位,工作于线性区的管作为电阻使用,而工作于亚阈值区的管和实际上相当于型的三极管,它们一起产生电流。M7~M11的栅源电压与构成了一个闭环反馈系统。

基准电压产生电路工作原理:

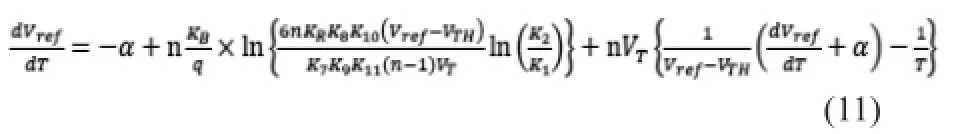

工作于亚阈值区的MOS管漏电流公式为:

体管的阈值电压,n为亚阈值斜率因子。一般当VDS>0.1V时,亚阈值漏电流公式可以简化为:

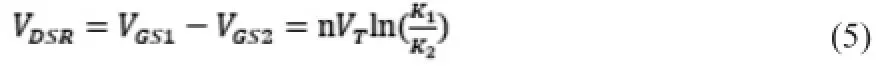

其中VDSR为晶体管MR漏源两端的电压差。因此易得:

由于晶体管MR作为电阻使用,工作于线性区(深三极管区),因此其阻值为:

进而可得:

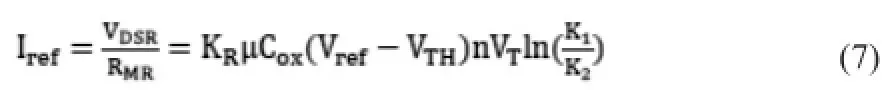

由公式8可以看出,基准参考电压Vref可以写成栅源电压VGS7与热电势Vr的倍数相加的关系。由于阈值电压VTH具有负温度系数而热电势VT具有正温度系数,因此可以通过调整晶体管M8~M10的尺寸来获得近零温度系数的基准参考电压Vref。

阈值电压与温度之间的关系为:

其中VTHO为0K时晶体管的阈值电压,a为阈值电压的温度系数。

因此基准参考电压可以写成:

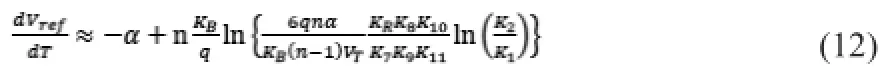

进而可得VREF的温度系数:

因此当:

成立时,可以得到零温度系数的基准参考电压。

图1 整体电路原理图

2. 电路仿真结果

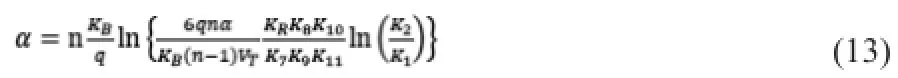

仿真结果表明,启动电路支路电流,参考电流,因此整体电路总电流。输出电压与温度关系如图2所示,在-40~125温度范围内,输出基准电压仅变化了,温漂系数TC为。

输出基准电压vref随电源电压的变化关系如图3所示,在0.7~1.8V电源电压范围内,电路能够正常输出670mV的基准电压,线性调整率为3.21mV/V。

在室温电源供电时的电源抑制比如图4所示,由图中可以看出,在带宽范围内的电源抑制比PSRR超过了。

电源上电时输出基准电压的建立过程如图5所示,由于电路中正反馈环的存在,使得基准电压的建立时间得到很大程度的降低。由图中可以看出,电路在10s内可以稳定快速的启动。

图2 基准电压随温度的变化关系

图3 基准电压随电源电压的变化关系

图4 在室温电源供电时的电源抑制比

图5 电源上电时的建立过程

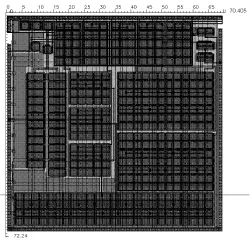

基准参考电压产生电路的版图如图6所示,版图尺寸面积仅为:7070m2,本次设计只采用MOSFETs管,未采用电阻和电容等,使用cascode结构代替运算放大器实现了电压的钳位,很大程度上减小了整体芯片的面积。

图6 整体芯片的版图设计

3. 总结

本次设计采用华大九天自主EDA软件Aether,结合华润上华0.18m工艺设计了一款适用于超低功耗SoC的高精度电压基准模块。本次设计的电压基准模块创新性的使用了工作于亚阈值区的MOSFETs来代替传统的电路结构,巧妙的利用具有负温度系数的MOS管阈值电压与具有正温度系数MOS管栅源电压相加的方法,来得到近零温度系数的基准电压。除了用做电阻的工作于线性区的MOS管之外,其余所有的MOS管均工作在亚阈值区。避免使用了大面积的三极管和电阻,有效的减小了整体芯片的面积和系统功耗。仿真结果表明,整体电路(包含启动电路)的功耗仅为210nA,电路版图面积仅为70,在0.7~1.8V的电源电压范围内,电路都能正常输出大小为630mV的基准电压,在-40~125温度范围内,温漂系数TC为16ppm,在1kHz带宽范围内的电源抑制比PSRR超过48dB。在电源上电以后,电路可以10s内快速稳定的启动。

[1] Chen, Hung-Wei, and Hsuan-Lun Kuo. “A low power supply CMOS bandgap reference voltage generator used current differential amplifier and DTMOST diode.” 2016 International Conference on Applied System Innovation (ICASI). IEEE, 2016.

[2] Shrivastava, Aatmesh, et al. “5.4 A 32nW bandgap reference voltage operational from 0.5 V supply for ultra-low power systems.”2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers. IEEE, 2015.

[3] Lee, Chu-Liang, et al. “A low power bandgap voltage reference for Low-Dropout Regulator.” Micro and Nanoelectronics (RSM), 2015 IEEE Regional Symposium on. IEEE, 2015.

[4] Abbasi, Mohammad Usaid, et al. “A high PSRR, ultra-low power 1.2 V curvature corrected Bandgap reference for wearable EEG application.” New Circuits and Systems Conference (NEWCAS), 2015 IEEE 13th International. IEEE, 2015.

[5]Ivanov,Vadim,Ralf Brederlow,and Johannes Gerber.“An ultra low power bandgap operational at supply from 0.75 V.”IEEE Journal of Solid-State Circuits 47.7(2012): 1515-1523.

[6]Ueno,Ken,et al.“A 300 nW, 15 ppm/C,20 ppm/V CMOS voltage reference circuit consisting of subthreshold MOSFETs.”IEEE Journal of solid-state circuits 44.7(2009):2047-2054.

王仁广(1993-),安徽人,吉林大学硕士研究生。

李捷菲(1994-),女,陕西人,吉林大学硕士研究生。

宫浩然(1994-),男,辽宁人,吉林大学本科生。

纪永成【通讯作者】(1981-),男,吉林人,吉林大学硕士研究生,工程师。