大功率LED封装界面层裂对界面传热性能的影响分析

杨道国,莫月珠,聂要要,蔡 苗,刘东静

(桂林电子科技大学 机电工程学院,广西 桂林 541004)

大功率LED封装界面层裂对界面传热性能的影响分析

杨道国,莫月珠,聂要要,蔡 苗,刘东静

(桂林电子科技大学 机电工程学院,广西 桂林 541004)

对大功率LED封装器件进行了封装界面层裂的热仿真分析,在芯片粘结(DA)层上构建了不同的界面层裂模型,探究了不同层裂形状、位置及分布时界面层裂对芯片热传递的影响规律。结果表明:随着界面层裂面积的增加,LED芯片结温以14 ℃/mm2以上的速率增大,层裂面积达到36%时,芯片最高温度为68.68 ℃,相比无层裂时升高了9.8%;并且界面层裂处于DA层的下界面比上界面对芯片温度分布影响更大;此外,针对同一界面的层裂缺陷,相对于边缘位置和中心位置,封装边角位置的层裂对整体LED封装热传输能力的阻碍作用更明显。

大功率LED;芯片粘结层;界面层裂;有限元分析;热仿真;传热性能

发光二极管(Light Emitting Diode, LED)是一种固态半导体发光二极管,自1993年日本的中村修二运用氮化镓(GaN)和铟氮化稼(InGaN)开发出了具有商业应用价值的蓝光LED以来,LED逐步应用于各种领域,如信号通信、室内照明、景观照明、屏幕显示和显示背光等。LED具有节能,环保,高效,寿命长等一系列优点,LED照明有可能取代传统的白炽灯和卤素灯成为第四代照明光源及绿色光源[1-3]。然而LED芯片电光转换效率较低,只有20%~30%的输入功率转换成光,而其余的都被转换为了热量[4]。若器件热管理方面设计不合理,热量不能及时散失,将导致LED芯片结温升高,降低光效、影响色温,甚至导致器件的使用寿命缩短或永久性损坏。

芯片粘结(DA)层材料,也称热界面材料,不仅起到机械支撑与导电的作用,也是热传输的重要通道,它能使热量从芯片传递到散热片上,所以影响着整个器件的可靠性[5-6]。大功率LED封装器件界面层裂破坏是LED器件工作期间主要的失效形式之一。近年来,电子器件的封装界面缺陷等问题也逐步受到国内外学者的广泛关注。陈颖等[7]研究了芯片粘接层的空洞对功率器件散热特性的影响,发现空洞位于粘结区域四角位置时,芯片散热情况最差。Otiaba等[8]通过三维有限元分析方法对芯片级封装器件的热界面材料空洞进行研究,分析了空洞结构、深度和空洞位置在热阻和结温上的影响。苏喜然等[9]针对FCOB(基板倒装焊)器件底充胶与芯片界面层裂问题进行了有限元仿真。Zhang等[10]通过有限元ANSYS软件建立了LED封装界面内聚力模型,模拟了LED封装界面层裂在热应力作用下的扩展。尽管有关粘结层界面缺陷和界面层裂对器件可靠性影响的研究存在不少,但是大部分的研究都是关于空洞或界面层裂的扩展与应力的探究,而针对大功率LED封装的界面传热,精确地构建DA层不同层裂面积、位置、形状以及层裂分布情况在封装传热上影响的研究报道却很少。

本文从分析封装界面层裂缺陷存在的不同形式对封装传热性能影响的角度,展开大功率LED封装器件的热仿真分析。通过构建不同界面层裂缺陷模型,对LED封装器件进行传热分析,对比并探讨LED DA层不同位置、形状及分布情况的界面层裂对LED芯片热传递的影响规律。

1 有限元模型

1.1 模型描述

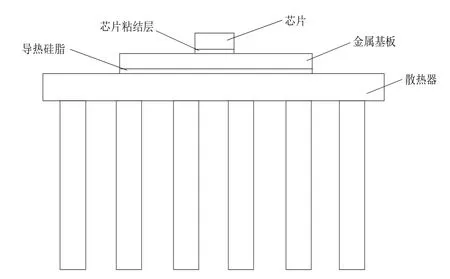

在LED实际封装中,由于芯片与基板的形状和型式多种多样。本文以功率型LED封装器件作为建模参考,建立单一芯片的LED简化模型,模型的基本结构如图1所示。模型主要由五部分组成,主要考虑芯片-粘接层-基板-热界面材料-散热器这一热传导路径。首先把LED芯片通过金锡共晶合金(Au80Sn20)固晶材料粘结到金属基板上,然后用热界面材料将其固定于散热器上。假设各种材料各向同性,且粘结良好。封装结构的各组成部分尺寸及材料参数分别见表1。

图1 COB-LED模型封装结构Fig.1 Package structure of COB-LED model

表1 LED封装模型各组成部分尺寸和材料属性Tab.1 The component size and material properties of LED package model

1.2 载荷与边界条件设定

分析中,芯片为热源,加载方式为在芯片上加载热生成率载荷。热生成率定义为单位体积的热流率。单个芯片功耗大小为1 W,由于芯片体积为0.25×109m3,发光效率为20%,所以热生成率为3.2×10 W/m3。假定模型的环境温度25 ℃,忽略可能存在的辐射散热,热量以传导形式传播,芯片产生的热量通过基板和散热器将生成的热量带走,基板和散热器表面与空气自然对流散热,对流散热系数为10 W/(m2·℃),对模型进行稳态热分析。

2 结果与分析

2.1 层裂模式

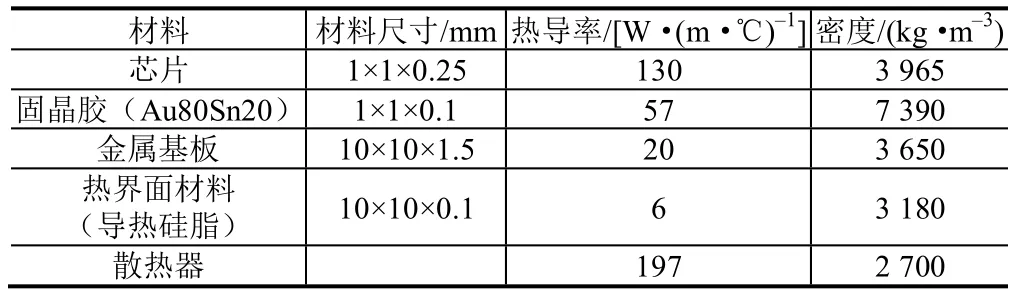

在引入界面层裂前,需要对界面层裂的形状大小、位置以及分布情况进行合适的选取。形状上主要选取正方形和长方形两种不同结构的层裂进行比较。为了研究方便,定义层裂率为层裂面积占DA层总面积的大小。本文引入了5种情况的层裂率,分别为4%,9%,16%,25%和36%作为研究对象。在位置的分布上,进行了两种对比,一是对分布在同一界面上的三种不同位置进行分析,分别是层裂出现在中心位置、边缘位置和边角位置;二是对针对上述三种不同位置,分别对比层裂出现在DA层上界面和下界面时器件温度变化情况。界面层裂分布在上、下界面的情况如图2所示。最后对集中大层裂和分散小层裂进行对比。层裂隙部分设为空气,厚度选取20 μm,热导率为0.026 1 W/(℃·m)。

图2 层裂出现在芯片粘结层(DA层)上、下界面Fig.2 Delaminations appeared in the upside and underside of the die attach layer

2.2 层裂位置分布对温度分布的影响

2.2.1 层裂分布在同一界面的不同位置

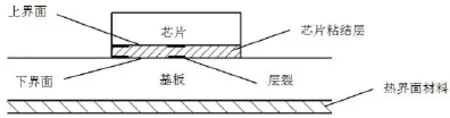

为了精确分析层裂缺陷在同一DA界面层不同位置的传热影响,本文主要针对三种不同位置的比较,如图3所示,16%的正方形界面层裂分别引入到DA层下界面的边角位置、边缘位置和中心位置。

图3 层裂以正方形模式出现在界面的三种不同位置Fig.3 Three different positions of square delamination mode

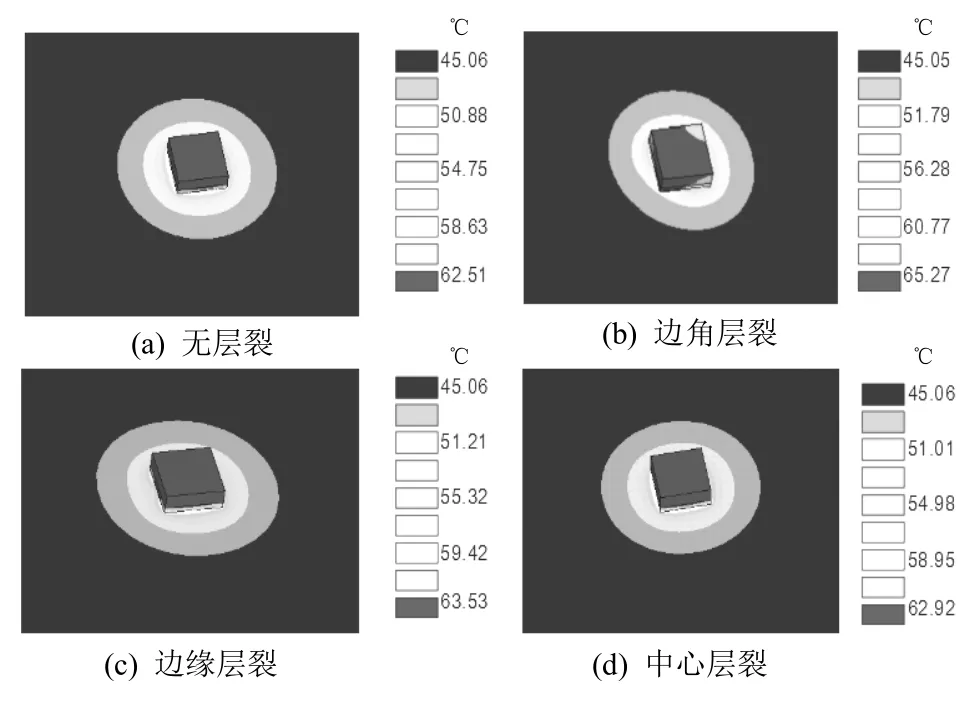

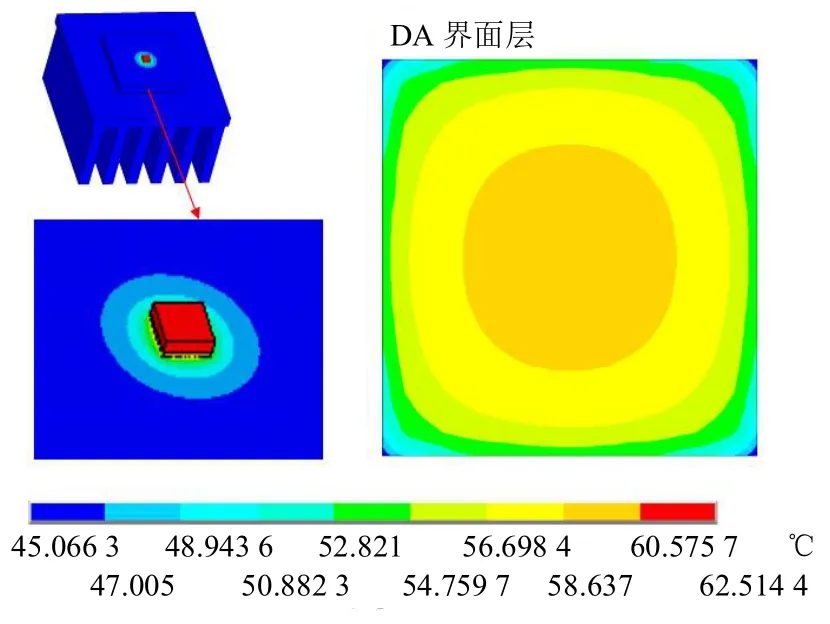

如图4所示,图4(a)、(b)、(c)、(d)分别为无层裂,层裂处于边角位置、边缘位置和中心位置的三维芯片温度分布图。图5为DA层无界面层裂的三维LED封装模型与DA层温度分布,从图可见,芯片最高温度(即结温)为62.51 ℃,离中心温度四周逐渐降低,DA界面层表面等温线呈圆形分布;在垂直方向上,芯片到基板和散热器的温度逐渐降低。

图4 层裂分布在不同位置的三维芯片温度分布Fig.4 The temperature distributions of three dimensional chips with delamination at different locations

图5 DA层无界面层裂的三维LED封装模型与DA层的温度分布Fig.5 Three dimensional LED package model with non-delamination and temperature distribution of die attach

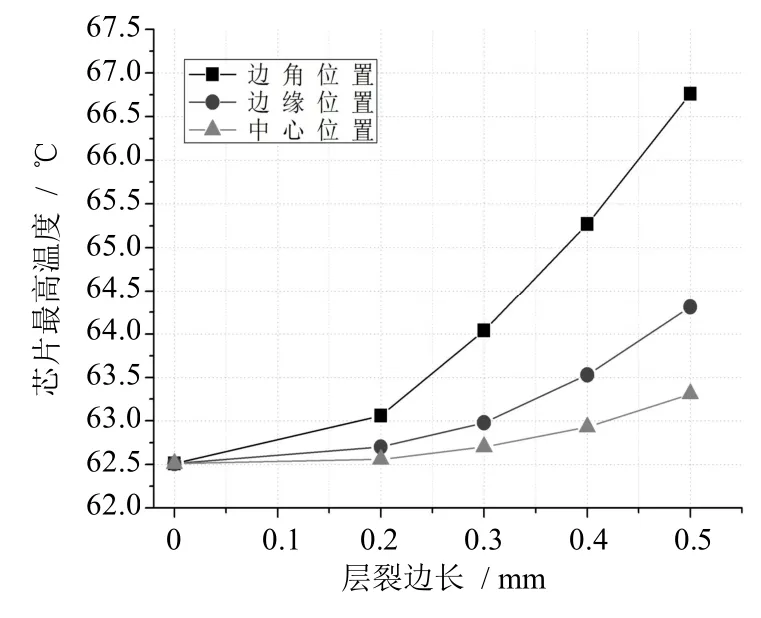

层裂边长与温度关系见图6,从图中曲线增长情况可见,当层裂边长小于0.2 mm时,芯片最高结温升高幅度较小;随着层裂边长不断增大,处于边角位置的层裂相比其他两个位置的芯片结温增幅更大。其中,当层裂边长达到0.5 mm时,处于边角位置的层裂的芯片最高温度为66.76 ℃,相比最初无界面层裂升高了6.8%。而相同层裂边长条件下,层裂处于边缘和中心位置,芯片结温分别升高2.9%和1.2%。由此可见,相同层裂大小时,分布在边角位置的层裂对芯片的结温影响最大,边缘位置次之,中心位置影响最小。文献[11]和文献[12]分别指出,拐角空洞对芯片最高温度影响最大,其次是中心空洞;分布在粘结层边缘的大空洞比中心和其他位置的大空洞对热阻升高贡献更大,本文结论与其试验结果一致。

图6 正方形层裂分布在不同位置Fig.6 Square delamination distribution in different locations

2.2.2 层裂分布在DA层的不同界面

如前文分析表明,对于同一界面处三种不同层裂的分布,处于边角位置的层裂对芯片温度分布影响最大。因此,本节针对出现在边角位置的正方形层裂,对比分析分布在DA层上、下两个不同界面的层裂对界面的热传递影响。

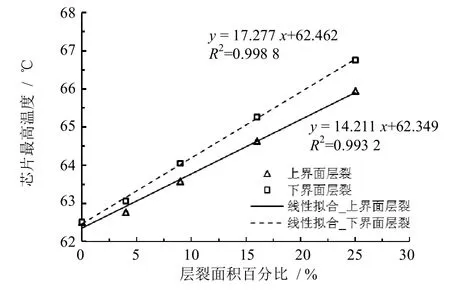

如图7所示,随着界面层裂面积的增加,LED芯片结温与之呈正比例增长,以14 ℃/mm2以上的速率逐渐增大,特别是当层裂缺陷处于DA层的下界面时。当层裂处于粘结层上界面且层裂面积为25%时,LED芯片最高温度约为65.94 ℃,相对于无层裂情况芯片温度升高了3.4%。然而,当层裂处于DA层下界面且具相同层裂面积时,LED芯片最高温度约为66.76 ℃,相对层裂出现在粘结层上界面提高了1.2%。可见,同等大小的层裂分别出现于DA层下界面和上界面时,下界面的层裂会比上界面对芯片温升的危害性更大。因此,为提高器件的热可靠性,应尽可能地减少DA层下界面的层裂缺陷。

图7 层裂分布在粘结层上下界面的芯片最高温度Fig.7 The highest temperature of chipwahen the delaminations distribute in the upper and lower inter face of die attach layer

2.3 层裂形状对温度分布的影响

为了简化分析,本节在DA层的边角位置引入两种规则的且具有相同面积的层裂模型,即正方形层裂和长方形层裂作为研究对象,如图8所示,16%的正方形和长方形层裂分别布置在边角位置。由前文可知,层裂位于下界面的边角位置对芯片结温的影响最大,所以本节主要比较不同形状的界面层裂位于DA层下界面对芯片最高温度的影响。正方形层裂面积分别选取4%,9%,16%,25%和36%。由于长方形的面积属性问题,为了便于将其与相同面积的正方形层裂比较,长方形层裂面积对应选取4%(0.1×0.4),9%(0.1×0.9),16%(0.2×0.8),25.2%(0.3×0.84)和36%(0.4×0.9)作为模型研究对象。

图8 正方形和长方形层裂分布在边角位置Fig.8 The distributions of square and rectangular delamination in the corner of die attaches

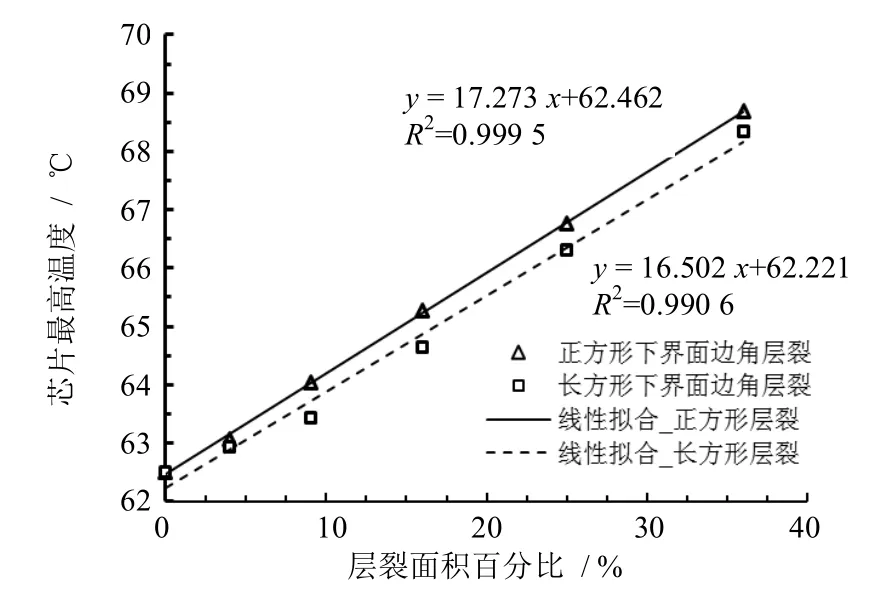

不同层裂形状对温度的影响见图9,不论是正方形层裂还是长方形层裂,芯片最高温度随着层裂面积线性增大,正方形层裂以17.27 ℃/mm2的速率增长,而长方形层裂则以16.50 ℃/mm2的速率增长。由此可见,具有相同层裂面积且分布于同一位置的正方形层裂比长方形层裂对散热的阻碍性更大。因此,不同形状的界面层裂对芯片结温也有不同的影响,与长方形层裂相比,正方形层裂对芯片传热影响更大。正方形层裂应该受到更大的关注。

图9 粘结层下界面不同层裂形状对芯片结温分布的影响Fig.9 Effect of different delamination shape on the temperature distribution of the chip

2.4 集中层裂与分散层裂对温度分布的影响

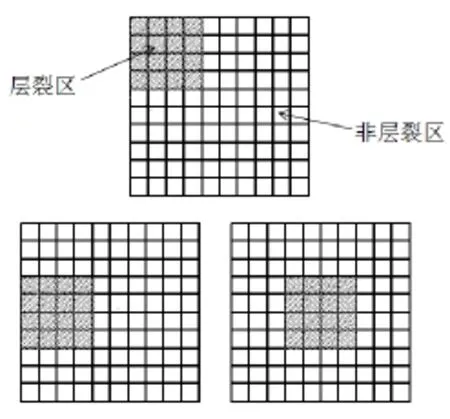

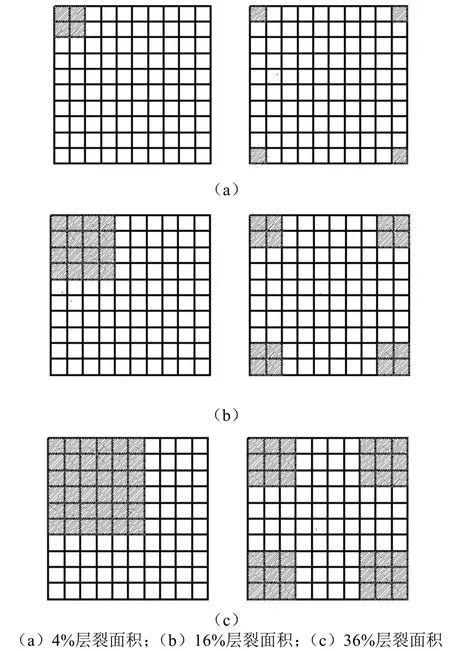

为了便于定量地比较集中层裂与分散层裂对温度分布的影响,选取形状规则的正方形层裂,分布在边角位置。对于单个大层裂,层裂面积分别选取4%,16%和36%。在相同层裂面积下,分散型小层裂选取4个均匀分布在边角位置的层裂。如图10所示,其中图10(a)、(b)、(c)分别为4%,16%和36%层裂面积的集中层裂与分散层裂示意图。

图10 正方形边角位置的集中层裂与分散层裂Fig.10 The concentrations and dispersions of delaminations

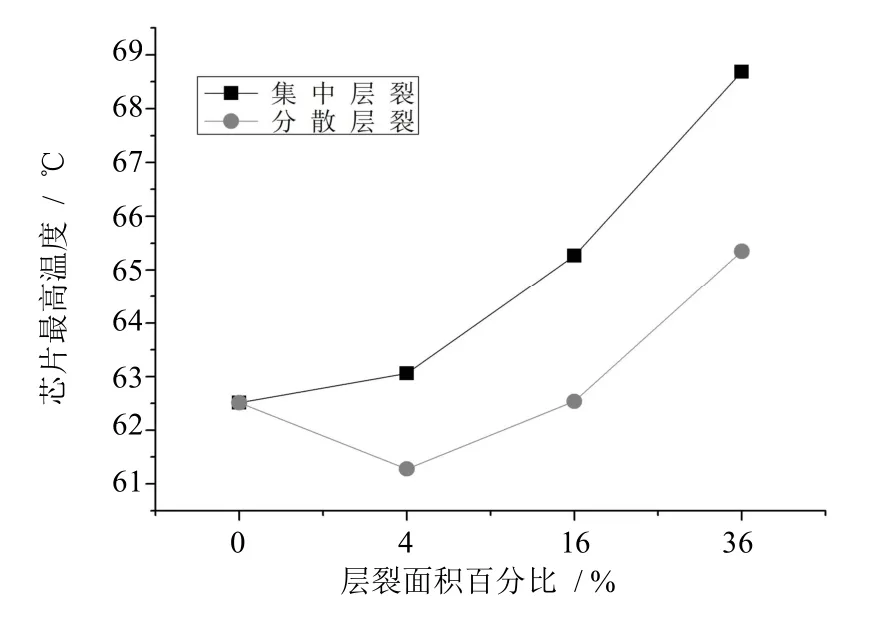

集中与分散层裂对温度的影响见图11,分散层裂对芯片结温的影响是先减少后增加,相比于集中层裂,分散层裂对芯片最高温度的增长比较缓慢;集中层裂则是随着层裂面积的增大,芯片最高温度快速升高。当层裂面积为36%的正方形集中层裂时,芯片最高温升为68.68 ℃,相比无层裂时温度升高了约9.8%,而对应的分散层裂,芯片最高温度为65.35 ℃,相比无层裂时引起温升只有4.5%。由此可见,与分散层裂相比,集中层裂引起更大的芯片结温温升,因此,在提高器件的热可靠性等方面,更应该避免集中层裂的产生。文献[13]中指出,在LED封装中,较低的空洞率显示了较低的结温,同理,芯片结温随粘结层的空洞率增加会有明显上升,而且在文献[12]中表明,单个大空洞对器件结温和热阻升高的影响远大于相同空洞率的离散小空洞,其仿真结果与本节结论一致。

图11 集中层裂与分散层裂对结温的影响Fig.11 Effect of concentration and dispersion delamination on junction temperature

3 结论

本文针对大功率LED封装DA层的界面层裂失效引起的封装传热性能退化问题,采用有限元热仿真分析,探索层裂形状、位置及分布情况对封装结构热传递过程的影响规律。结果表明:1)随着界面层裂面积的增加,LED芯片结温以14 ℃/mm2以上的速率增大,且在DA层内,远离中心位置,芯片温度逐渐降低;2)DA层外边缘,层裂对结温影响复杂,相对于边缘位置和中心位置,相同面积的界面层裂时,封装边角位置的层裂对整体LED封装热传输能力的阻碍作用更明显;3)针对同一界面的层裂缺陷,下界面出现的层裂会比上界面出现的层裂对界面热量的传递阻碍性更大。此外,对比相同面积的分散小层裂,单个大层裂缺陷对LED芯片结温的影响更大。可见,LED封装层裂对结温、热阻等热参数的影响,不能仅靠层裂的大小来衡量,还需考虑层裂位置、形状和分布情况等因素,特别要注意DA层下界面的层裂。在大功率LED封装的热设计过程中,为提高器件的热可靠性,应可能地减少DA层下界面边角处和边缘处的层裂缺陷。

[1] 苏永道, 吉爱. LED封装技术 [M]. 上海: 上海交通大学出版社, 2010: 2-7.

[2] 崔元日, 潘苏予. 第四代照明光源——白光LED [J]. 灯与照明, 2004 (2): 31-34.

[3] TAN L, LI J, WANG K, et al. Effects of defects on the thermal and optical performance of high-brightness light-emitting diodes [J]. Electron Packg Manuf, 2009, (4): 233-240.

[4] HE F, CHEN Q, LIU J, et al. Thermal analysis of COB array soldered on heat sink [J]. Int Commun Heat Mass Trans, 2014, 59: 55-60.

[5] YAN X, FENG S, SHI D, et al. Degradation of the die attach layer in chip-on-board packaged light-emitting diodes during temperature cycling[C]// International Conference on Electronic Packaging Technology. Changsha, China: The Conference Organizer, 2015: 980-984.

[6] ZHANG G, FENG S, ZHU H, et al. Determination of thermal fatigue delamination of die attach materials for high-brightness LEDs [J]. Photon Technol Lett, 2012, 24(5): 398-400.

[7] 陈颖, 孙博, 谢劲松, 等. 芯片粘接空洞对功率器件散热特性的影响[J]. 半导体技术, 2007, 32(10): 859-862.

[8] OTIABA K C, BHATTI R S, EKERE N N, et al. Numerical study on thermal impacts of different void patterns on performance of chip-scale packaged power device [J]. Microelectron Reliab, 2012, 52(7): 1409-1419.

[9] 苏喜然, 杨道国, 赵鹏, 等. FCOB器件在热循环载荷下的界面层裂研究 [J]. 电子元件与材料, 2008, 27(1): 62-64.

[10] ZHANG B, YANG D. Delamination modeling in LED package by cohesive zone method [C]// International Conference on Electronic Packaging Technology. Dalian, China: The Conference Organizer, 2013: 1217-1221.

[11] 谢鑫鹏, 毕向东, 胡俊, 等. 空洞对功率芯片粘贴焊层热可靠性影响的分析 [J]. 半导体技术, 2009, 34(10): 960-964.

[12]吴昊, 陈铭, 高立明, 等. 粘结层空洞对功率器件封装热阻的影响[J].半导体光电, 2013, 34(2): 226.

[13] LIU Y, LEUNG S Y, ZHAO J, et al. Thermal and mechanical effects of voids within flip chip soldering in LED packages[J]. Microelectron Reliab, 2014, 54(9): 2028-2033.

(编辑:陈渝生)

Effect of interface delamination on heat transfer performance of high power LED package

YANG Daoguo, MO Yuezhu, NIE Yaoyao, CAI Miao, LIU Dongjing

(School of Mechanism and Electrical Engineering, Guilin University of Electronic Technology, Guilin 541004, Guangxi Zhuang Autonomous Region, China)

Thermal simulation analysis of interface delamination of high power LED package device was carried out. Different interface delamination models were constructed on die attach layer, and influences of the different shapes, positions and distributions of delamination on heat transfer of the chip were explored. The results show that with the increase of interface delamination area, the junction temperature in LED chip increases with the rate of more than 14 ℃/mm2. When the delamination area is 36%, the maximum temperature of the chip is 68.68 ℃, which is 9.8% higher than that of the non-delamination interface. In addition, temperature distribution of the chip whose delamination occurs at the underside (die attach-to-metal substrate interface) of the die attach layer is larger than that of the upside (chip-to-die attach interface). For the same interface, that delamination occurs at edge angle position is more harmful for blocking heat transfer in the overall LED package than that at the edge position and the center position.

high power LED; die attach layer; interface delamination; finite element analysis; thermal simulation; heat transfer performance

10.14106/j.cnki.1001-2028.2016.08.018

TN604

:A

:1001-2028(2016)08-0076-05

2016-06-22

:蔡苗

国家自然科学基金资助(No. 51366003);广西研究生教育创新计划资助(No. YCBZ2015037);广西中青年教师基础能力提升项目资助(No. KY2016YB148)

蔡苗(1981-),男,广西玉林人,助理研究员,主要从事微电子封装可靠性方面研究,E-mail: caimiao105@163.com;莫月珠(1990-),女,广东阳江人,研究生,研究方向为微电子封装可靠性,E-mail:moyezhi747@163.com 。

时间:2016-08-03 22:36

: http://www.cnki.net/kcms/detail/51.1241.TN.20160803.2236.018.html