“高分四号”卫星凝视相机视频电路设计与实现

郭宇琨 王衍 王建宇

(北京空间机电研究所,北京 100094)

“高分四号”卫星凝视相机视频电路设计与实现

郭宇琨 王衍 王建宇

(北京空间机电研究所,北京 100094)

“高分四号”卫星是中国首颗地球静止轨道遥感卫星,其携带的凝视相机系统能够实现在36 000km的地球静止轨道拍摄到50m分辨率的图像信息。高轨道、高分辨率光学拍摄任务所带来的问题是,面阵CMOS图像传感器模块将以极快的速度产生大量的并行图像数据。这对以CMOS图像传感器模块为核心的视频电路提出了更高的要求。而传统的视频电路设计方法不仅会产生一些信号完整性问题,且并不能完全适用于基于这种大数据量的面阵CMOS图像传感器模块的视频电路设计。文章通过仿真分析和实验验证,对比常规的设计方法,结合CMOS图像传感器模块的特点和输入输出特点,对基于这种面阵CMOS图像传感器模块的相机视频电路提出了新的设计方案,并证明了文章所提出的设计方案正确可行,且效果优于常规的设计方案。文章提出的设计方案已成功应用在“高分四号”卫星,在要求日趋复杂的遥感领域亦有广阔的应用前景。

视频电路 图像传感器 遥感卫星 地球静止轨道

0 引言

随着民用减灾、国土资源、环境与气象等卫星应用领域对卫星遥感数据的高时间、高空间分辨率的需求越来越紧迫,中低轨道遥感卫星越来越难以全面满足遥感用户对高空间分辨率的连续侦察监视需求。地球静止轨道遥感技术是国际航天遥感技术的一个重要方向,但它的技术研制难度大,文献[1-3]介绍了法国和欧空局的三颗地球静止轨道高分辨率遥感卫星的具体技术指标、所搭载的平台等基本信息,但均尚未在轨运行。文献[4]介绍了目前国际上地球静止轨道卫星的发展动态及发展趋势。“高分四号”卫星不但是我国第一颗地球静止轨道遥感卫星,更是世界首颗高轨道、高分辨率光学遥感卫星。其设计目标是能够实现在36 000km的地球静止轨道拍摄到50m分辨率的图像信息。而这样的系统要求使得CMOS图像传感模块具有极高的像素,因此输出的图像数据不仅数据量庞大,且速率很高[5-6]。这对 CMOS图像传感器模块工作所需要的外围电路设计的难度提出了更高的要求。本文主要介绍了一个成功应用在地球静止轨道遥感卫星上,高分辨率凝视相机CMOS视频电路的设计方案,是整个“高分四号”卫星的关键技术之一。本文首先给出了针对CMOS图像传感器模块所设计的系统方案,然后针对各个模块在设计中遇到的具体难点,通过与常见的设计方法对比后提出了更优的详细设计方案;采用仿真对比和实验验证的方法,指出常见的设计方法所存在的问题,并证明本文所提出的设计方案可以达到系统要求;最终给出成像结果。

1 视频电路系统设计

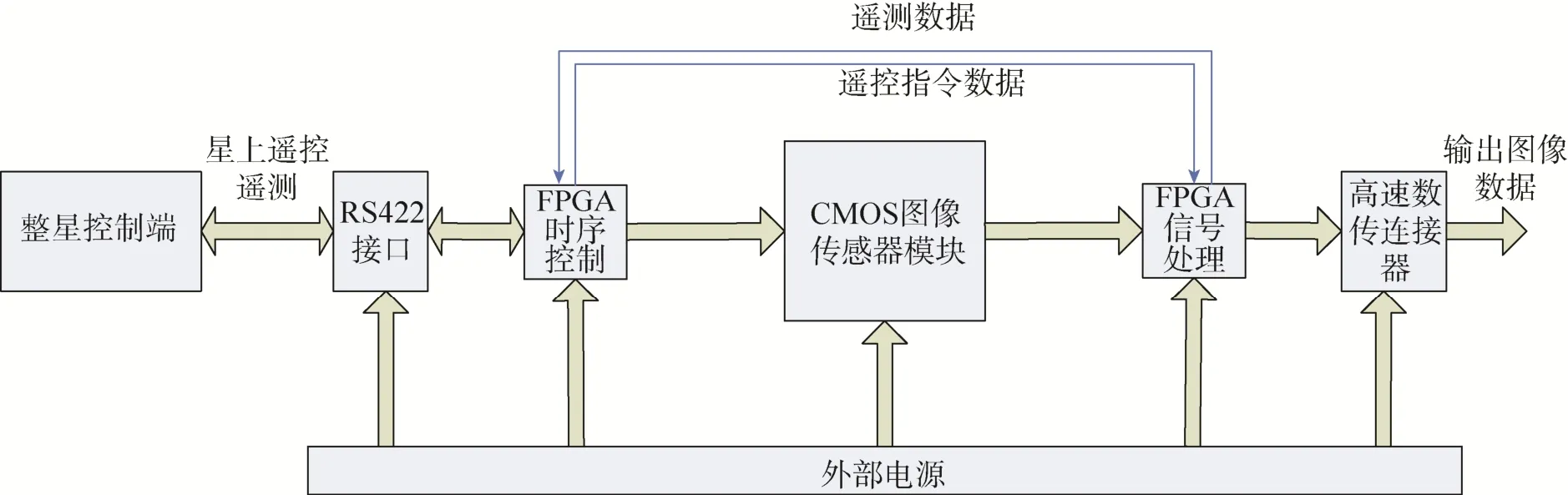

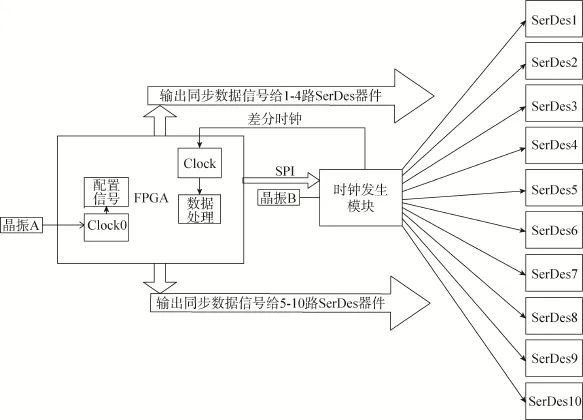

本文提出了一种应用在地球静止轨道遥感卫星上的凝视相机视频电路设计方案,系统框图如图 1所示。

图1 视频电路系统Fig.1 Video circuit system chart

系统以CMOS图像传感器为核心,以时序控制模块、信号处理模块为主要组成模块,构成了整个视频系统的核心部分。时序控制模块主要完成设置该CMOS图像传感器模块的工作模式,控制其曝光和读出;信号处理模块主要完成对CMOS图像传感器模块输出的图像数据按照约定格式编码,并输出给高速数传连接器;电源模块则是为整个单板的所有元器件提供所需的工作电压。系统通过RS422与整星的控制端交互遥测遥控信号,最后通过高速数传连接器将图像信息实时传输给后端处理器。

CMOS图像传感器可以用于地球静止轨道卫星对地实时监控,传感器具有静止电子快门功能,积分时间可调,因此更适合应用在地球静止轨道卫星对固定区域进行长时间不间断的监测[7-9]。CMOS图像传感器模块内集成有模拟信号处理电路、I2C总线控制接口、曝光/白平衡控制、视频时序产生电路、数字转换电路、行选择、列选择及放大和光敏单元阵列[10-11]。CMOS图像传感器模块提供了一系列控制寄存器,通过总线编程(如PC总线)来对自增益、自动曝光、白色平衡、校正等功能进行控制,编程简单、控制灵活[12-14]。因此本文的CMOS图像传感器模块接受时序控制电路的控制指令,时序控制电路接收来自星上或地面的指令,解析指令,然后根据指令要求对CMOS图像传感器模块内部的一系列控制寄存器进行编程,灵活控制模块按照要求输出图像数据[15]。具体电路设计方式参看本文2.1节。CMOS图像传感器模块内的模拟信号处理电路主要执行相关双采样(Correlated Double Sampling,CDS)功能。每一个感光阵列有一个A/D转换器。模块直接输出的数字图像信号可以很方便地传输给后续处理电路,供数字信号处理器对其进行处理。因此本文通过信号处理模块接收并转发CMOS图像传感器模块输出的数字图像信号,同时对其进行信号处理,具体电路设计方式参看本文 2.2节。电源模块需要提供的电压有十几种,这需要由单独的电源电路板对输入电压进行分压稳压处理。由于电源数量众多,需要保证每个电压稳定且噪声最小。

本节详细介绍了围绕CMOS图像传感器模块提出的视频电路系统设计方案。并且重点阐述了本文第2节将介绍的时序控制模块和信号处理模块的功能。这两个模块作为本系统设计的重点和难点将在第 2节中给出详细的设计方案,并通过仿真和实验验证与传统设计方法作比较,给出结论。

2 视频电路详细设计

针对本系统CMOS图像传感器模块的结构特点及输出信号的特点,本文设计视频电路时,按照本文第1节系统设计的框架,分别对时序控制模块和信号处理模块的设计重点和难点进行了分析,并与两种常见的设计方案,通过仿真结果对比。

2.1 时序控制模块的电路设计

时序控制模块主要为CMOS图像传感器模块提供控制信号。根据本系统CMOS图像传感器的特点,CMOS图像传感器模块内部行译码区域工作时钟数量众多,数量大于20,时序控制FPGA(可编程逻辑阵列)需要为CMOS图像传感器模块提供同源的多路时钟,且时钟品质的好坏直接影响芯片获取的图像品质。因此主要设计重点和难点在于CMOS芯片行译码区域工作时钟信号的网络拓扑设计。本节首先给出了两种常见的时钟网络设计方案,通过原理图仿真验证了其存在的问题,并提出了本文所采用的设计方案,给出仿真结果。

传统的时钟网络设计方案有两种设计方法:一种是FPGA的工作时钟由晶振产生,CMOS图像传感器模块各个区域的工作时钟都由FPGA提供,其输出一路时钟信号,由近及远采用菊花链的方式连接到各个区域的时钟信号管脚上;另外一种设计方法是,FPGA的工作时钟由晶振产生,FPGA输出多路时钟信号,分别连接到CMOS图像传感器模块的各时钟域。为了节省FPGA输出时钟扇出数量,且尽可能保证时钟信号品质,每个时钟信号最多可分别输出给两个相邻时钟域。

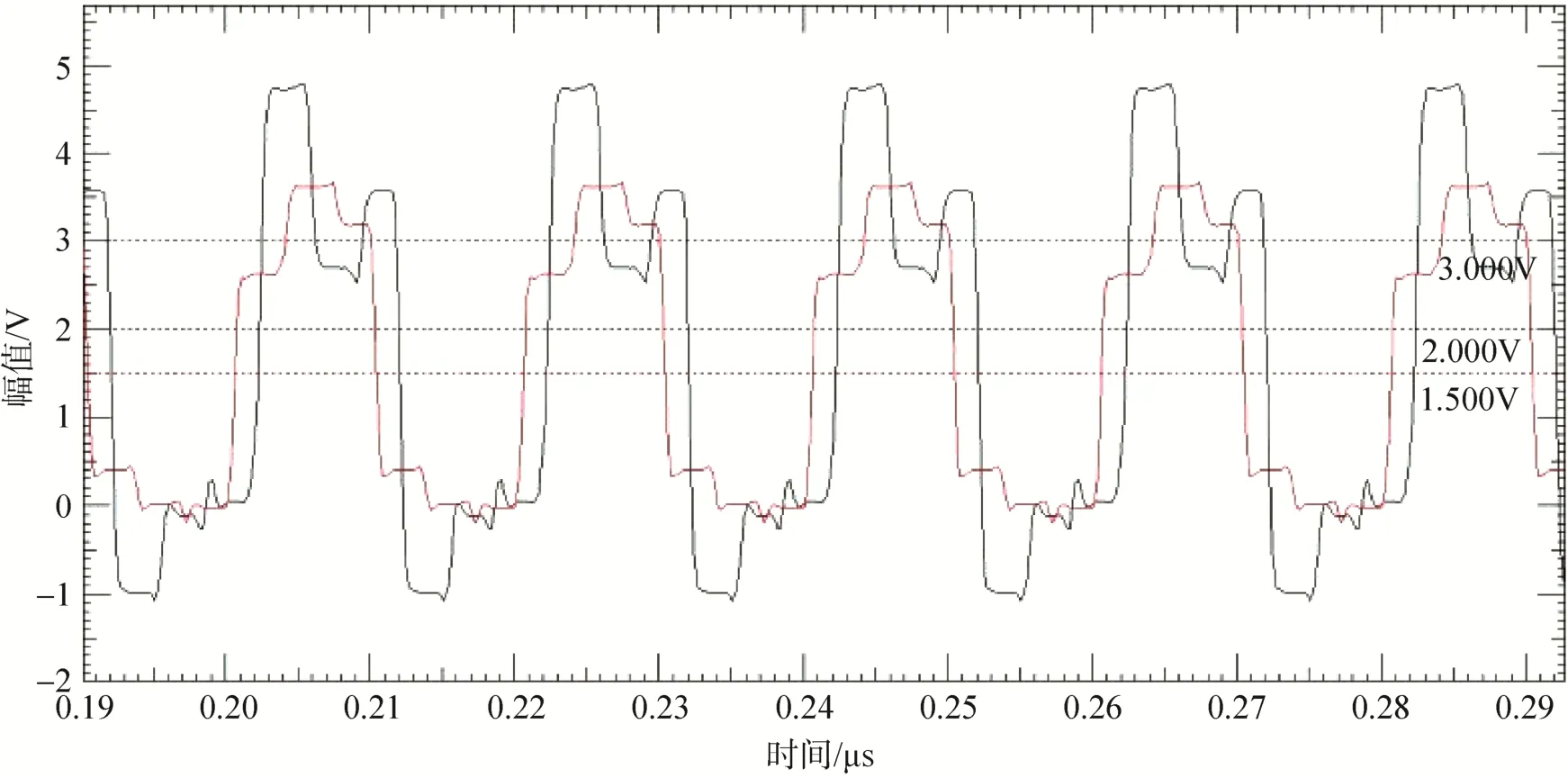

第一种设计方法得到的时钟信号会产生严重的信号完整性问题,离得最近的时钟信号由于受到来自远端的反射,品质最差。使用SigXplorer软件对原理图进行仿真,仿真时钟频率为50MHz,其中一路时钟信号的仿真结果如图2所示(其中源端匹配电阻50Ω)。图中黑色线条是FPGA输出端的时钟信号,输出电压为3.3V,红色线条是菊花链第一个节点接收端的时钟信号,可以看到由于反射出现了毛刺信号,源端信号的品质也出现了严重的失真,而终端信号高电平无法达到3.3V,因此可能造成采样错误。

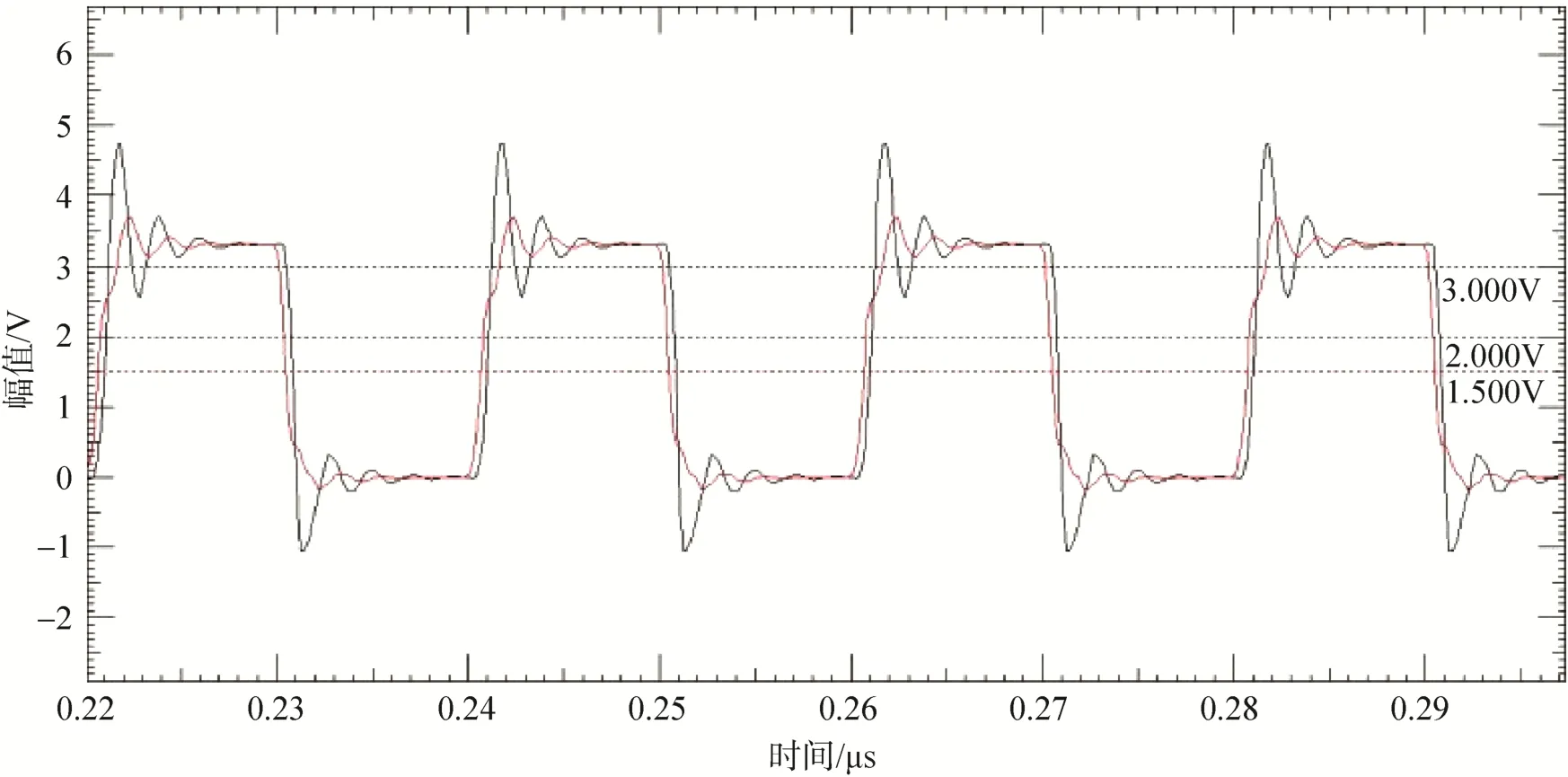

第二种设计方法,由于时钟信号在源端做了很多分岔,到达各个时钟域的信号由于无法匹配都有很大的反射,严重影响了信号品质。使用SigXplorer软件对原理图进行仿真,仿真时钟频率为50MHz,其中一路时钟信号的仿真结果如图3所示。图中黑色线条是FPGA输出端的其中一路时钟信号,输出电压为3.3V,红色线条是其中一路接收端的时钟信号,可以看到即使在理想的模型条件下,源端信号和终端信号都出现不同程度的振铃现象,而终端信号电平的波动可能造成采样错误。

图2 常见时钟网络设计方案一的时钟仿真结果Fig.2 The scheme 1 simulation results of common clock network design

图3 常见时钟网络设计方案二的时钟仿真结果Fig.3 The scheme 2 simulation results of common clock network design

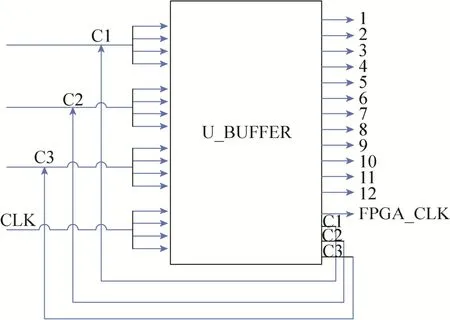

综上,本文提出了一种新的时钟网络设计方案,时钟信号的设计采用星型拓扑结构,如图4所示。图中CLK时钟信号由晶振直接提供,把晶振提供的时钟信号经过驱动模块一拖四输出,一路供给时序控制FPGA芯片,另外三路C1、C2、C3再分别经过驱动模块一拖四输出12路时钟信号。每个时钟信号分别输出给两个相邻时钟域。由于驱动模块增强了时钟信号的驱动力,也避免了时钟信号在源端有较大的分岔,得到的信号品质较好。解决了时序控制FPGA为CMOS图像传感器模块提供同源的多路时钟的问题。

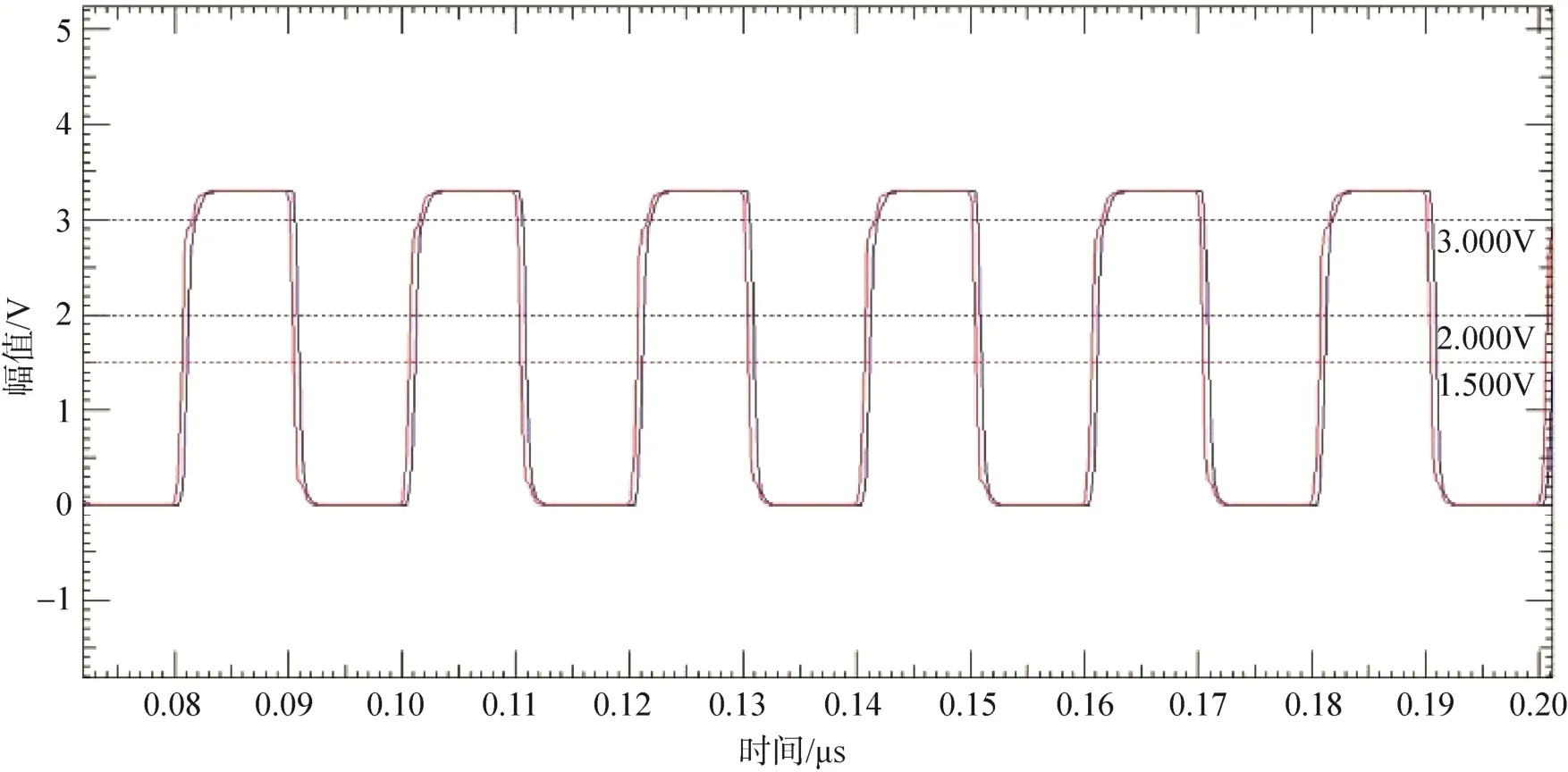

图 5是本文提出的时钟网络设计方案对其中一路时钟信号的原理图仿真结果,仿真时钟频率为50MHz。图中黑色线条是FPGA输出端的其中一路时钟信号,输出电压为3.3V,红色线条是其中一路接收端的时钟信号,可以看到在理想模型下,源端没有反射,接收端的信号品质也保持完整。

图4 本文提出的时钟网络设计方案拓扑结构Fig.4 The clock network design scheme proposed in this paper

图5 本文提出的时钟网络设计方案的时钟仿真结果Fig.5 Simulation results of the clock network design scheme proposed in this paper

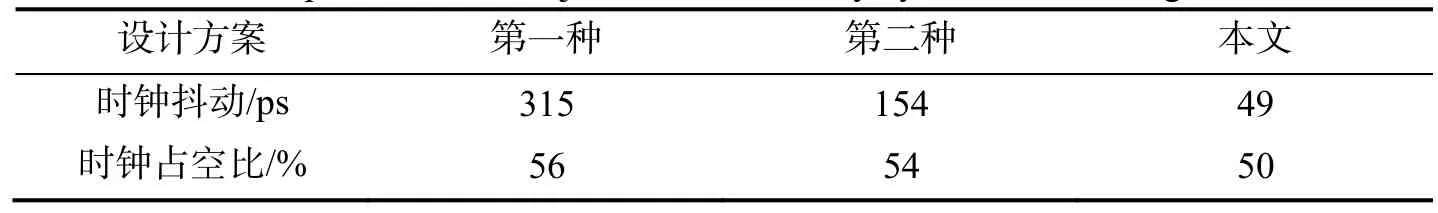

对比图3、4、5可以看出,本文所采用的时钟设计方案得到的时钟信号波形品质最优,三种方案下得到的时钟抖动和时钟占空比如表1所示(仿真时钟频率均为50MHz)。

表1 三种设计方案时钟抖动和时钟占空比结果对比Tab.1 Comparison of clock jitter and clock duty cycle of three design schemes

其他的控制信号,如帧同步、行同步、控制总线信号,由于速度很慢,可以采用菊花链结构,以减少FPGA的扇出。

2.2 信号处理模块的电路设计

根据本系统CMOS图像传感器模块的特点,信号处理模块电路设计的重点和难点是多路高速数据信号的并行传输问题。CMOS图像传感器模块输出10路并行高速图像数据,到对应的10片高速数传芯片(Serdes器件),每片Serdes器件实现数据位的并串转换之后,经高速数传连接器输出给接收端,并由接收端解析完成后实时显示图像。信号流如图1所示。

每个Serdes器件需要一路数据同步时钟作为采样时钟,信号处理模块需要同时产生10路同步时钟给每个Serdes器件。这有两方面设计要求。首先根据Serdes器件对时钟品质的严格要求,输入Serdes器件的时钟抖动必须小于100ps,占空比必须不大于55%。而常规的设计难以保证在真空高低温实验和震动实验中满足该设计要求。其次,本系统输出的10路并行图像数据要以2Gbit/s的高速速率传输到接收端,而要想在接收端解析后恢复拼接成一幅完整的图像,要求10路数据必须严格同步并行输出。

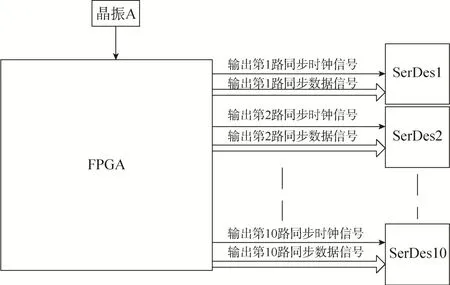

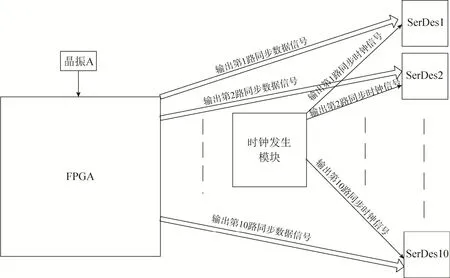

文献[16-19]给出了常见的两种设计方案,第一种方案FPGA输出10路时钟信号,与对应的数据信号一起输出给对应的Serdes器件,如图6所示。第二种方案FPGA的工作时钟由晶振产生,其他Serdes器件的时钟由驱动力更强的带有去抖动功能的时钟发生模块提供,如图7所示,图中每两路相邻的Serdes器件接收到的信号互为主、备份信号。

图6 多路数据并行收发方案一的结构Fig. 6 The program 1 structure of multiple data parallel transmitting and receiving

图7 多路数据并行收发方案二的结构Fig. 7 The program 2 structure of multiple data parallel transmitting and receiving

第一种方案由于CMOS图像传感器模块的结构限制,所有数据都从CMOS图像传感器模块的一侧输出,导致所有10片Serdes器件都集中分布在PCB板的一侧。这样的PCB布局必然无法紧凑。因此,时钟传输的距离就不可避免会增大。根据实验验证,晶振所产生的时钟抖动为50ps左右,占空比50%。但经过FPGA变换后,最长的时钟走线会带来时钟信号占空比变化和抖动增大等问题。实际测试结果显示,FPGA输出100MHz的时钟信号,其终端的时钟抖动为300ps左右,占空比53%。经过高低温实验和振动实验后,时钟信号的占空比还会进一步恶化,最终无法达到Serdes器件对时钟占空比和抖动的要求。第二种方案数据信号与同步时钟不同源,因而造成后端图像不能正确恢复。

本文提出了一种新的多路数据并行收发方案:FPGA的工作时钟和Serdes器件的采样时钟均由时钟发生模块产生。但由于时钟发生模块需要收到来自FPGA的SPI总线配置信号才能工作,因此FPGA必须首先由晶振产生的时钟信号驱动,通过SPI总线给时钟发生模块提供配置信号,从而产生10路数传时钟和1 路FPGA工作时钟。实验证明该方案有效可行的解决了10路图像数据和时钟同时准确传输给Serdes器件的问题。

其电路关系如图8所示,图8中每两路相邻的Serdes器件接收到的信号互为主、备份信号。

图8 本文提出的多路数据并行收发方案的结构Fig. 8 Structure of multiple data parallel transmitting and receiving program proposed in this paper

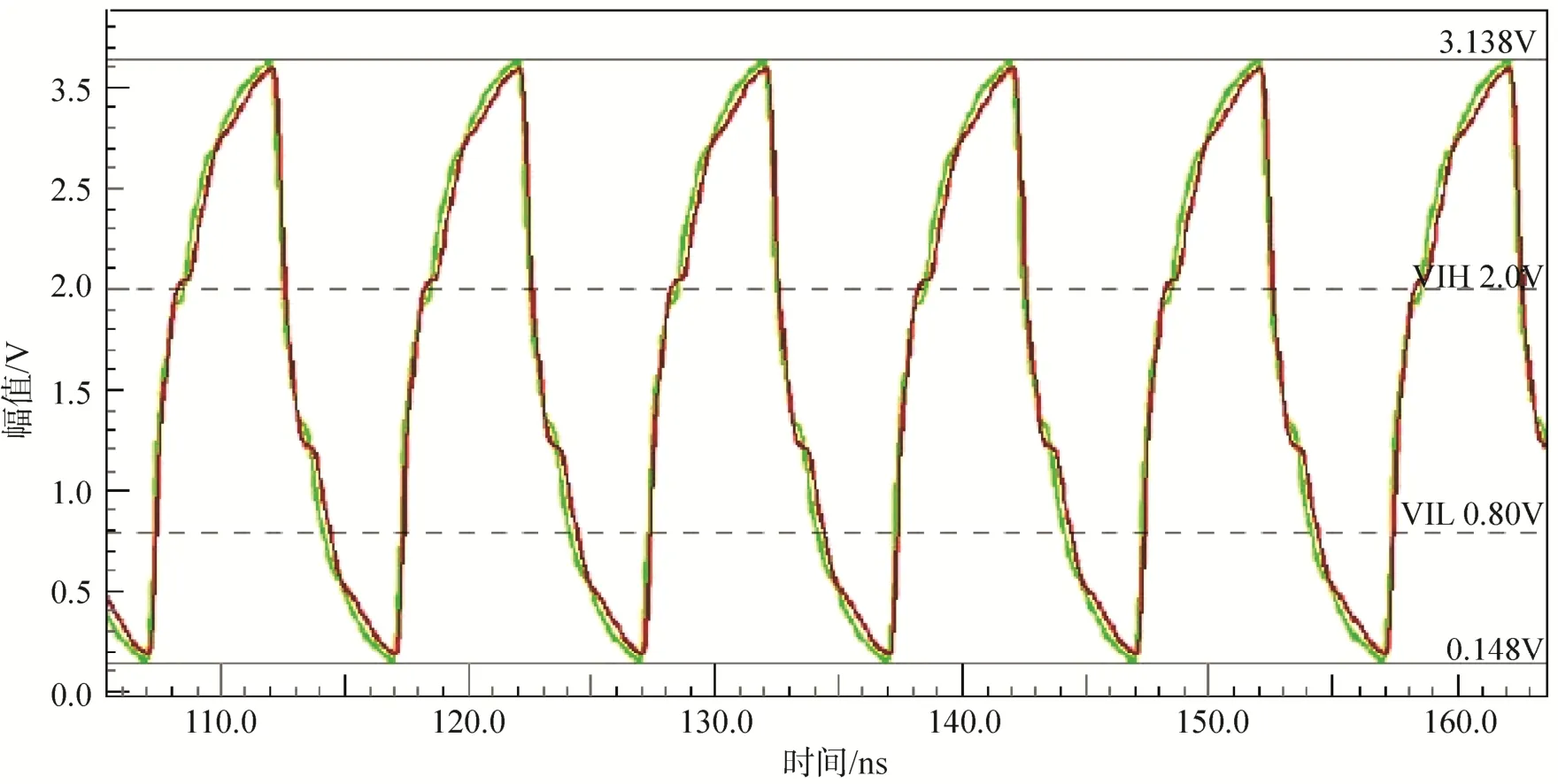

按照本文的方案设计思路进行 PCB设计,并对所设计的视频电路进行后仿真。任意选取时钟发生模块产生的两路主、备份时钟信号进行后仿真,结果如图9所示。其中虚线部分为所对应高低电平的判断标准,(VIH:高电平;VIL:低电平)可以看出时钟信号满足信号完整性要求。

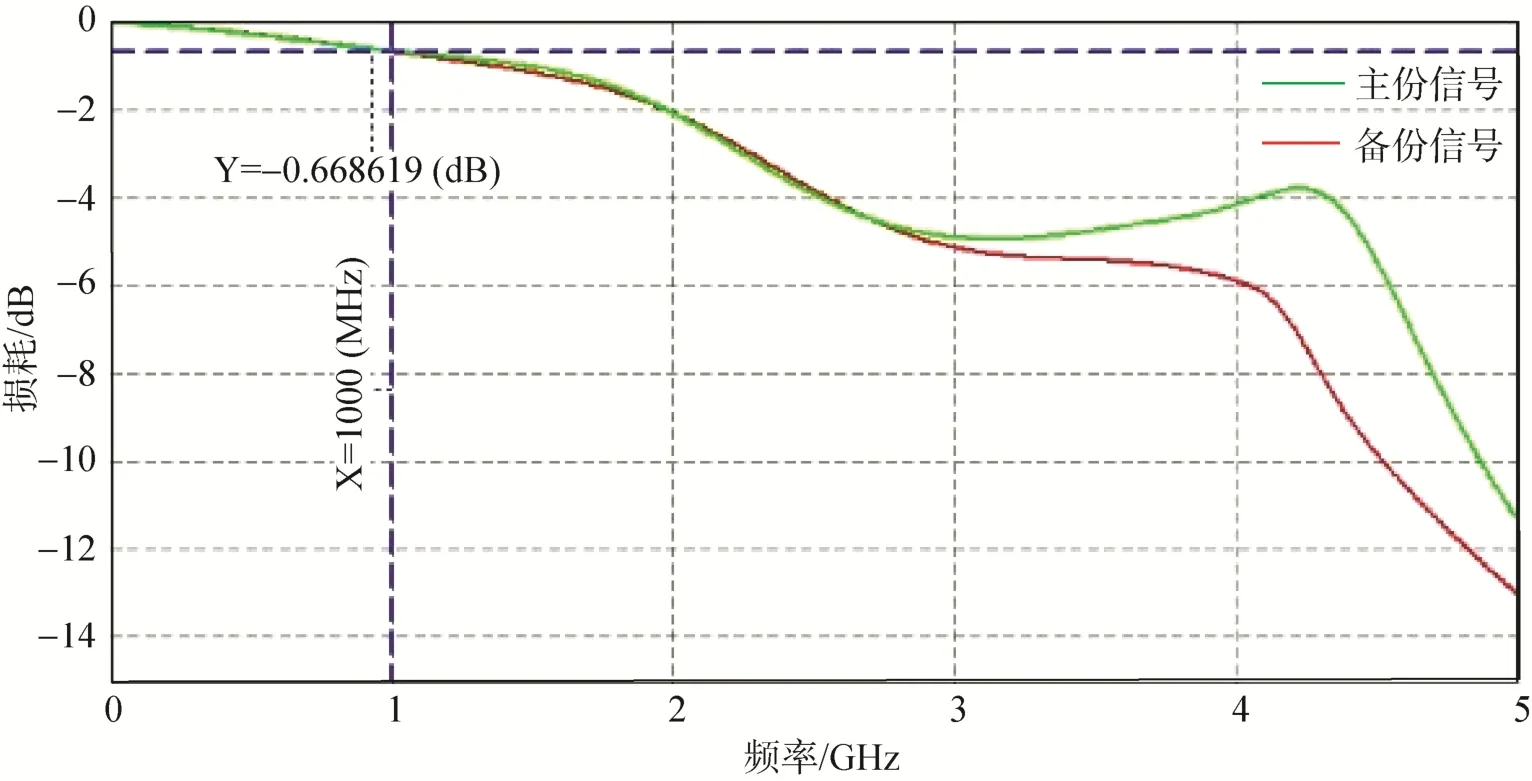

任意抽取 10路高速数传信号中的两路主、备份信号,对其进行后仿真,视频电路终端输出的差分信号的损耗情况如图10所示:

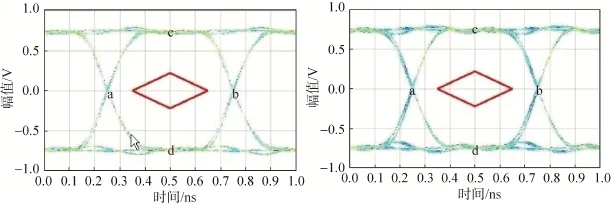

从图10中可以看出,在1GHz的频率带宽下(2Gbit/s的传输速率),从Serdes器件到高速数传连接器的高速差分信号损耗为0.67dB,损耗非常小。主、备份信号在接收端的眼图如图11所示:

图9 本文提出的多路数据并行收发方案时钟信号后仿真结果Fig. 9 Simulation results of multiple data parallel transmitting and receiving program proposed in this paper

图10 本文提出的多路数据并行收发方案高速数传差分信号的损耗情况Fig. 10 High speed digital transmission loss of multiple data transmission scheme proposed in this paper

图11 本文提出的多路数据并行收发方案高速数传差分信号的眼图Fig. 11 The eye pattern of the scheme proposed in this paper

从图11中可以看出所抽取的该路高速差分信号的主份信号和备份信号眼高分别为1.417V和1.391V,眼宽分别为495ps和492.5ps(图中a、b点之间的距离为眼宽,c、d点之间的距离为眼高)。该信号的信号噪声较小,信号品质可以达到正确传输的要求。

2.3 误码率测试

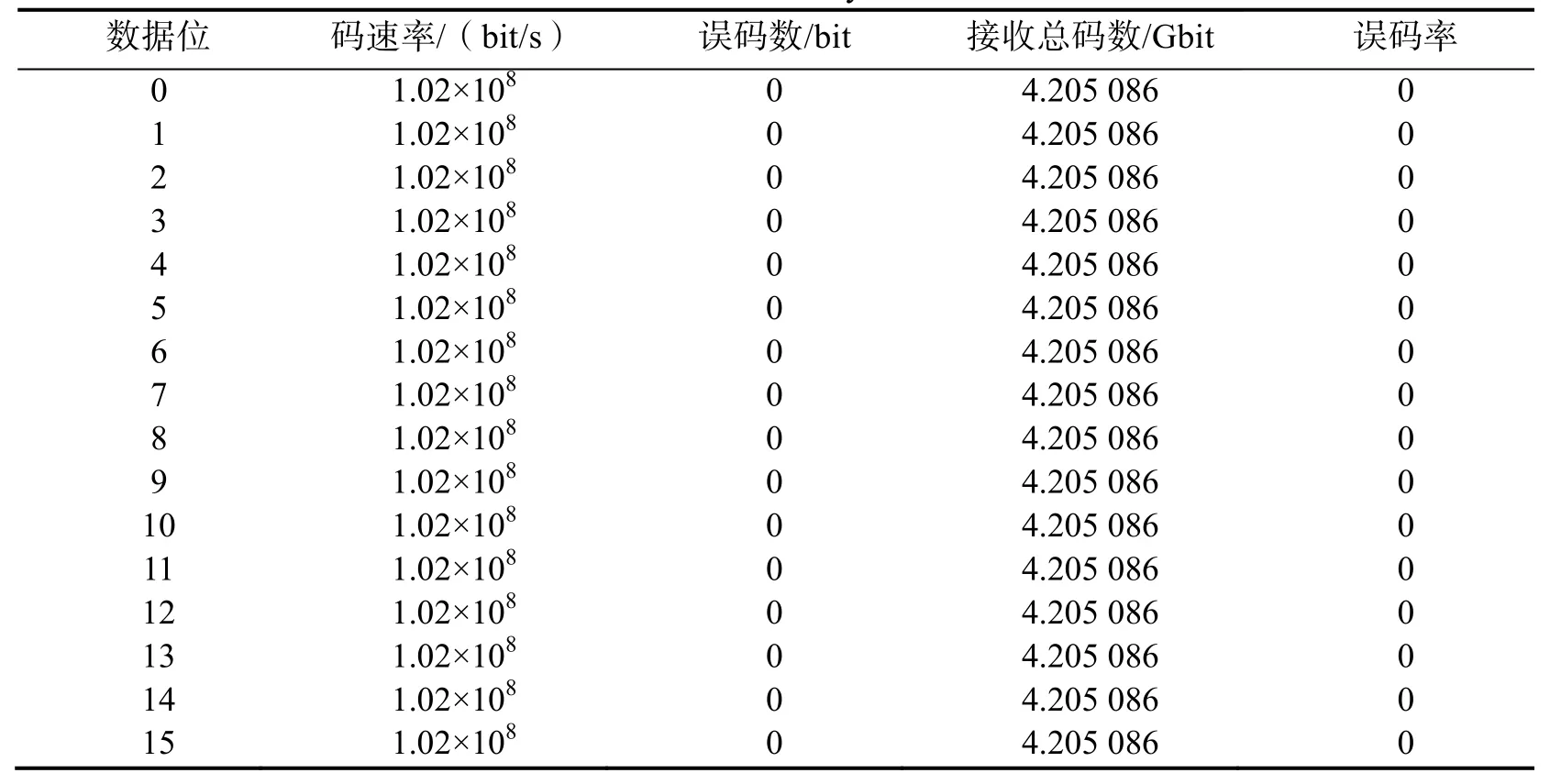

经过误码分析仪测试,本文所设计的视频电路传输数据的误码率(BER)[20]如表2所示。从测试结果表2中可以看出测试验证的总bit数量达到1012数量级时,出现的总的错误bit数仍然为0,可见其误码率此时已经达到10-12量级。

表2 系统传输数据误码率测试结果Tab.2 BER of the system tests

3 结束语

本文提出的基于面阵CMOS图像传感器的相机视频电路的设计方案解决了对CMOS图像传感器模块输出的高速、多通道、超大数据量的快速实时处理技术难点。其中时序控制模块的设计方案解决了由时序控制FPGA为CMOS图像传感器模块提供同源的多路时钟的问题,且数量不小于20个。信号处理模块的设计方案解决了多路、高速图像数据信号的并行接收和并行输出问题,且数据速率高达2Gbit/s。系统最终实现了“高分四号”卫星在36 000km的高轨拍摄到50m分辨率的图片信息,填补了我国高轨遥感卫星领域高分辨率凝视相机的空白。且其地面测试的系统误码率可以达到10-12量级。

References)

[1] XAVIER R.From Meteorology Globle Observation to High Resolution Permanent Surveillance[C]. 2007. IAC-07-B1.2.06.

[2] CYRILLE T. A Dedicated African Space Observatory[C]. 2009. IAC-09-B1.2.3.

[3] GOC T, KNIGGE T, SCHULL U, et al. A Mission for Real-time Monitoring Through High-resolution Imaging from Geostationary Orbit Final Report[R/OL]. [2009-05-13]. http://gsp.esa.int/document-view/-/wcl/wlGiHTp4j7JC/10192/geooculus-a-mission-for-real-time-monitoring-through-high-resolution-imaging-from-geostationary-orbit-executive-summary.

[4] 郭玲华, 邓峥, 陶家生, 等. 国外地球同步轨道遥感卫星发展初步研究[J]. 航天返回与遥感, 2010, 31(6): 23-30. GUO Linghua, DENG Zheng, TAO Jiashen, et al. Preliminary Research on Development of Foreign GEO Remote Sensing Satellites[J]. Spacecraft Recovery & Remote Sensing, 2010, 31(6): 23-30. (in Chinese)

[5] 陈瑞明, 吴松波, 王建宇, 等. 对地观测高分相机视频电子学集成化技术[J]. 航天返回与遥感, 2013, 34(3): 34-41. CHEN Ruiming, WU Songbo, WANG Jianyu, et al. Camera Video Electronics Integration Technology for High SpatialResolution Earth Observation Sensor[J]. Spacecraft Recovery & Remote Sensing. 2013, 34(3): 34-41. (in Chinese)

[6] 王庆友. 图像传感器应用技术[M]. 北京: 电子工业出版社, 2003, 9: 207-218.

WANG Qingyou. Image Sensor Application Technology[M]. Beijing: Publishing House of Electronics Industry, 2003, 9: 207-218. (in Chinese)

[7] 熊平. CCD与CMOS图像传感器特点比较[J]. 半导体光电. 2004(1): 1-4. XIONG Ping. Comparison of CCD and CMOS Image Sensors[J]. Semiconductor Optoelectronics. 2004(1): 1-4. (in Chinese)

[8] 宋勇, 郝群, 王占和, 等. 基于CMOS图像传感器的成像系统设计[J]. 光学技术, 2002, 28(3): 253-256.

SONG Yong, HAO Qun, WANG Zhanhe, et al. Imaging System Design Based on CMOS Image Sensor[J]. Optical Technology. 2002, 28(3): 253-256. (in Chinese)

[9] 余国华, 冯启明. 基于 CMOS图像传感器的视频采集系统设计[J]. 武汉理工大学学报(交通科学与工程版), 2004, 28(1): 145-147.

YU Guohua, FENG Mingqi. Design of Video Capture System Based on CMOS Image Sensor[J]. Journal of Wuhan University of Technology(Transportation Science and Engineering). 2004, 28(1): 145-147. (in Chinese)

[10] 侯雨石, 何玉青. 数码相机CMOS图像传感器的特性参数与选择[J]. 光学技术, 2003, 29(2): 174-176.

HOU Yushi, HE Yuqing. Specific Parameters and Selection of CMOS Image Sensor for DSC Designing[J]. Optical Technology. 2003, 29(2): 174-176. (in Chinese)

[11] 李东, 许家恺, 孔令红. 新型CMOS图像传感器及其应用[J]. 电子元件与材料, 2002, 21(10): 35-37.

LI Dong, XU Jiakai, KONG Linghong. New-type CMOS Vision Sensors and its Application to PCS[J]. Electronic Components and Materials. 2002, 21(10): 35-37. (in Chinese)

[12] BIGAS M, CABRUJA E, FOREST J,et al. Review of CMOS Image Sensors[J]. Microelectron, 2006, 37: 433-451.

[13] 程开富. CMOS图像传感器的最新进展及其应用(续)[J]. 电子与封装. 2003, 3(3): 45-48.

CHENG Kaifu. The Latest Development and Application of CMOS Image Sensor(Continued)[J]. Electronics and Packaging. 2003, 3(3): 45-48. (in Chinese)

[14] 程开富. CMOS图像传感器的最新进展及其应用(续)[J]. 半导体情报. 2003, 3(4): 47-51.

CHENG Kaifu. The Latest Development and Application of CMOS Image Sensor(Continued)[J]. Semi-Conductor Information. 2003, 3(4): 47-51. (in Chinese)

[15] 甘玉泉, 高伟, 董钊. 基于CPLD的面阵CMOS图像传感器的驱动时序设计[J]. 电子器件, 2009, 32(3): 500-503.

GAN Yuquan, GAO Wei, DONG Zhao. Design of Driving Timing for Array CMOS Image Sensor Based on CPLD[J]. Chinese Journal of Electron Devices, 2009, 32(3): 500-503. (in Chinese)

[16] 武亦楠, 吕增明, 张宇, 等. 基于FPGA的多通道面阵CCD成像系统设计[J]. 光机电信息, 2011, 28(6): 39-43.

WU Yinan, LYU Zengming, ZHANG Yu, et al. Design of Multi-port Area CCD Imaging System Based on FPGA[J]. Optical Mechanical and Electrical Information, 2011, 28(6): 39-43. (in Chinese)

[17] 张达, 徐抒岩. 基于TLK2711的高速图像数据串行传输系统[J]. 微计算机信息, 2009, 25(2): 284-286.

ZHANG Da, XU Shuyan. High-speed Serial Transmission System for Image Data Based on TLK2711[J]. Control and Automation, 2009, 25(2): 284-286. (in Chinese)

[18] 张达, 徐抒岩. 高速CCD图像数据光纤传输系统[J]. 光学精密工程, 2009, 17(3): 670-673.

ZHANG Da, XU Shuyan. High-speed CCD Image Data Fiber Transmission System[J]. Optics and Precision Engineering, 2009, 17(3): 670-673. (in Chinese)

[19] 张贵祥, 金光, 郑亮亮, 等. 高速多通道CCD图像数据处理与传输系统设计[J]. 液晶与显示, 2011, 26(3): 397-403.

ZHANG Guixiang, JIN Guang, ZHENG Liangliang, et al. Design of High-speed and Multi-channel CCD Image Data Processing and Transmission System[J]. Chinese Journal of Liquid Crystal and Displays, 2011, 26(3): 397-403. (in Chinese)

[20] GEROGE J, YU P, KOGA R. Single Event Effects and Total Does Test Results for TI TLK2711 Transceiver[J]. IEEE REDW, 2008: 69-75.

Design and Implementation of Staring Camera Video Circuit on GF-4 Satellite

GUO Yukun WANG Yan WANG Jianyu

(Beijing Institute of Space Mechanics & Electricity, Beijing 100094, China)

GF-4 satellite is the first China’s GEO remote sensing satellite, whose camera system can obtain 50m resolution image information from a 36 000km GEO. An area array CMOS image sensor module quickly generates a large number of parallel data, which puts forward higher requirements for video circuit that is the core of an image sensor module. The traditional design method is unable to produce signal integrity, and not suitable for the higher requirements. In this paper, through simulation analysis and experimental verification, by comparison with the conventional design method and according to sensor module characteristics and input and output characteristics, an area array CMOS image sensor camera video circuit is advanced based on the proposed new design scheme. It is proved correct and feasible, and better than the conventional one. The proposed approach has been successfully applied in GF-4 satellite and has wide application prospect in the remote sensing field where the requirements are increasingly complicated.

camera video circuit; image sensor; remote sensing satellite; geostationary earth orbit (GEO)

V443+.5;V474

: A

: 1009-8518(2016)04-0049-10

10.3969/j.issn.1009-8518.2016.04.007

郭宇琨,女,1987年生,2012年获北京理工大学通信与信息系统专业硕士学位,工程师。研究方向为视频电子学信号处理与视频相机系统。E-mail: sandra0507@sina.com。

(编辑:刘颖)

2016-03-23

国家重大科技专项工程