单区JTE加场板终端结构的优化设计

潘晓伟,冯全源,陈晓培

单区JTE加场板终端结构的优化设计

潘晓伟,冯全源,陈晓培

(西南交通大学 微电子研究所,四川 成都 611756)

为了提高芯片面积利用率,采用单区结终端扩展(JTE)与复合场板技术设计了一款700 V VDMOS的终端结构。借助Sentaurus TCAD仿真软件,研究单区JTE注入剂量、JTE窗口长度和金属场板长度与击穿电压的关系,优化结构参数,改善表面和体内电场分布,提高器件的耐压。最终在120.4mm的有效终端长度上实现了838 V的击穿电压,表面最大电场为2.03×105V/cm,小于工业界判断器件击穿的表面最大电场值(2.5×105V/cm),受界面态电荷的影响小,具有较高的可靠性,且与高压深阱VDMOS工艺兼容,没有增加额外的掩膜和工艺步骤。

结终端扩展;复合场板;VDMOS;击穿电压;表面最大电场;界面态电荷

随着器件击穿电压的升高,采用传统场限环(Field Limit Rings, FLRs)技术与场板(Field Plate, FP)技术的终端结构长度迅速增加[1-3],而结终端扩展(Junction Termination Extension, JTE)技术为同时实现高击穿电压与较短终端长度提供了可能性[2]。迄今为止,已有不少文献对JTE终端结构进行报道。JTE注入剂量、JTE窗口长度、JTE结深以及JTE区数或者JTE区横向掺杂分布等参数影响JTE终端击穿电压及电场分布[4-7]。而JTE结构对界面电荷十分敏感,掺杂又会引入新的电荷。场板与结终端扩展复合结构能够减弱击穿电压对注入电荷的敏感性[5]。但目前对这种复合结构的分析和设计方法偏于理论或理想化,对影响其击穿电压的因素缺乏深入研究。

本文结合JTE、金属和多晶硅复合场板技术,分析了离子注入剂量、JTE窗口长度及界面态电荷对这种复合终端击穿电压的影响,同时设计了一款700 V功率VDMOS终端结构,其击穿电压达到了838 V,有效长度仅为120.4 µm。与其他文献对比,在保证耐压的要求下终端长度缩小了20%左右。

1 单区JTE终端结构及原理

1.1 单区JTE结构

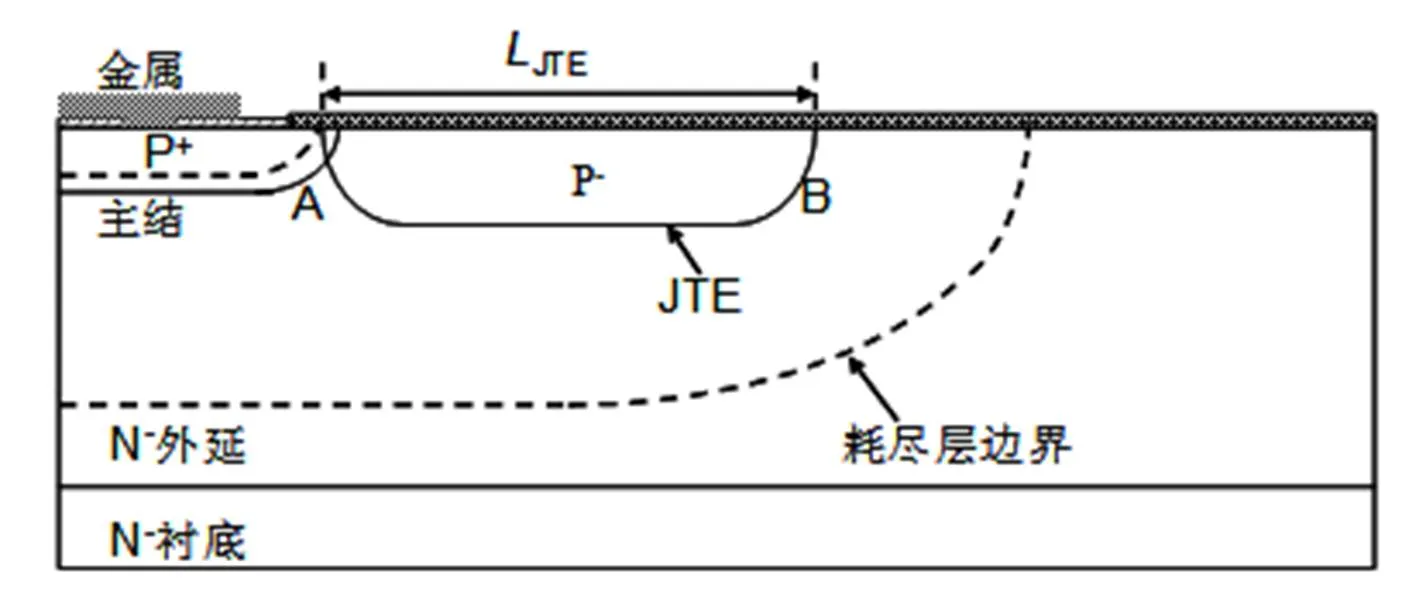

JTE技术是在主结边缘处(常是弯曲的)选择性地进行注入离子,通过一定的退火工艺,形成延伸结构,如图1结构示意图中的P-型区。JTE实际上是一种电荷补偿技术,对引入的电荷十分敏感。注入剂量过低,则电荷量过小,补偿效果不明显,电场峰值出现在主结处(如图1中的A点所示),不能有效地提高耐压;反之,注入剂量过高,即补偿过量,电场峰值出现JTE区的边沿(如图1中的B点所示),JTE区不能有效耗尽,无法充分发挥JTE结构的作用,造成器件提前击穿[4-5]。为实现最大击穿电压,需要精确控制JTE区电荷,以保证施加反向偏置时注入区的电荷被完全耗尽。

图1 结终端扩展(JTE)结构示意图

理想情况下,JTE区电荷与掺杂浓度A及最大电场max存在以下关系[7]:

最大击穿电压BR是JTE窗口长度JTE的函数[7]:

式中:BR,ideal和是平行平面结击穿电压和最大耗尽层宽度;为电子电荷量(1.6×10–19C);S是半导体的介电常数。但JTE大于两倍时,击穿电压不再增加[7]。基于此,调节JTE剂量和JTE窗口长度,优化电场分布,使得击穿电压达到最大。

另外,JTE结深较浅,对改善主结曲面部分的电场分布不大理想。设计时需采用高温退火工艺使JTE结深等于或大于主结结深[8]。

离子注入退火和硅表面热生长氧化物过程中引入的电荷改变硅体内空间电荷分布[1],使耗尽层发生相应地变化,从而改变JTE区的电场分布,影响击穿电压。所以,优化JTE参数,氧化层中固定电荷也是必不可少的因素。

1.2 复合场板JTE结构

常用的场板有金属场板和阻性场板[8],阻性场板又称之为多晶硅场板。在实际应用中常将两者结合起来形成复合场板结构。复合场板结构中,金属场板覆盖多晶硅场板的边缘,两者在硅表面产生的横向电场方向相反,互相削弱,从而减小界面态电荷产生的表面最大电场[9]。

为缓解JTE结构对电荷的敏感,在图1中的结构上添加复合场板,改进后的结构如图2所示。该结构中新增加一个击穿点C,JTE注入剂量和界面态电荷的变化可能导致击穿在此处发生。

图2 复合场板加JTE结构示意图

2 700 V VDOMS仿真设计

2.1 单区JTE终端结构参数

基于上述理论分析,本文在Sentaurus TCAD仿真平台上以700 V VDMOS为例对以上两种结构进行仿真优化。两种结构采用在厚度为55 μm、电阻率为19 Ω·cm的外延层,Pbody区覆盖5.3 μm长的JTE区,保证主结能够较好地由浅阱向深阱过渡。JFET注入剂量和Pbody注入剂量分别为2.0×1012cm–2和4.4×1013cm–2,形成6.3 μm深阱结深(JTE结深)和18.2 μm宽、4.6 μm深的主结。

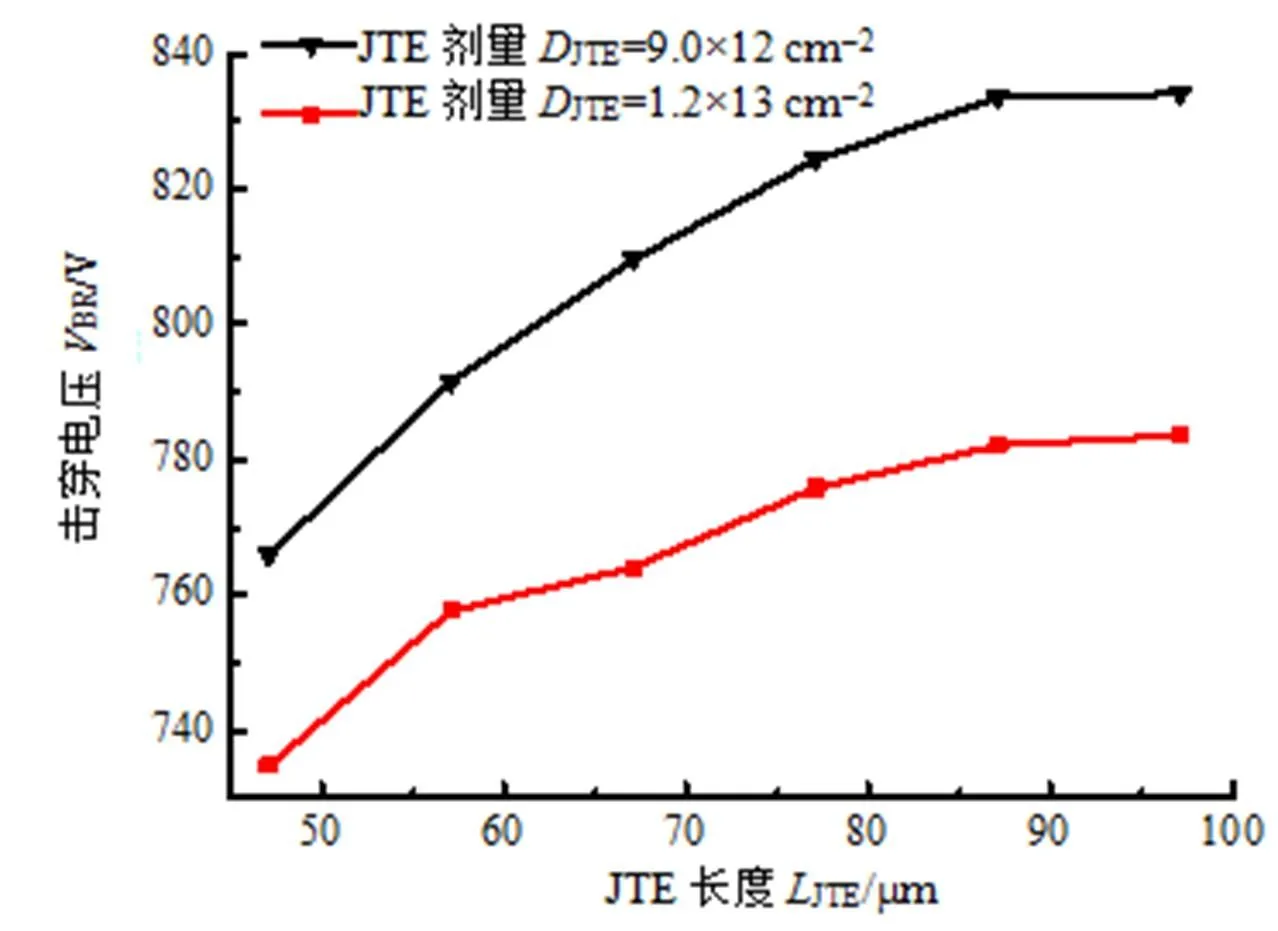

根据图1结构,分析JTE掺杂注入剂量和JTE窗口长度与耐压的关系,如图3所示。JTE剂量一定时,耐压随JTE窗口长度增加而增加,但JTE窗口长度增大到90 μm左右时耐压增加幅度很小。这是因为足够长的JTE窗口长度能够有效地降低结边缘表面电场。考虑到器件芯片面积大小,将JTE窗口长度取为78 μm。为便于分析,将两种结构的JTE窗口长度取为相同值。

图3 JTE掺杂剂量和JTE窗口长度与击穿电压的关系

为了保证JTE区电荷完全耗尽时主结处的耗尽层收敛到硅表面,将金属场板左端靠近主结,但不与源电极相连。金属场板完全覆盖多晶硅场板,以减小界面电荷的影响。图4给出了图2结构金属场板长度对耐压的影响。金属场板长度越长,其末端的电势线越靠近结边缘,电势线密集,造成电场集中,使得击穿点向结边缘(B点)靠近,击穿电压降低;金属场板长度太短,电势线靠近多晶硅场板末端,不利于击穿电压的提高。此例中调整复合场板,优化表面电场,最终确定金属场板长度M为40.9 μm,多晶硅场板长度P为8.3 μm,金属场板覆盖住多晶硅场板,两者末端间距离26 μm。

图4 单区JTE击穿电压随金属场板长度的变化

图5给出不同JTE剂量对两种结构的击穿电压的影响。由图可知,对于无场板的JTE结构,击穿电压随着JTE区P型掺杂剂量的增大而增大,JTE区补偿电荷被完全耗尽;达到最大值后JTE剂量继续增大,因电荷补偿过量而迅速下降。而有复合场板JTE结构减小界面电荷产生的表面最大电场,击穿电压在JTE剂量为8×1012~1×1013cm–2内基本保持不变;但JTE剂量超过1×1013cm–2后电荷补偿过量不能被完全耗尽,故不能有效发挥JTE结构的作用,击穿电压会迅速下降。因此,无场板的JTE结构最优化剂量为1.1×1013cm–2;有复合场板的JTE结构最优化剂量在8×1012~1×1013cm–2范围内,此例中取8.5×1012cm–2。

图5 有无场板结构下JTE击穿电压随JTE剂量的变化

2.2 仿真结果与对比

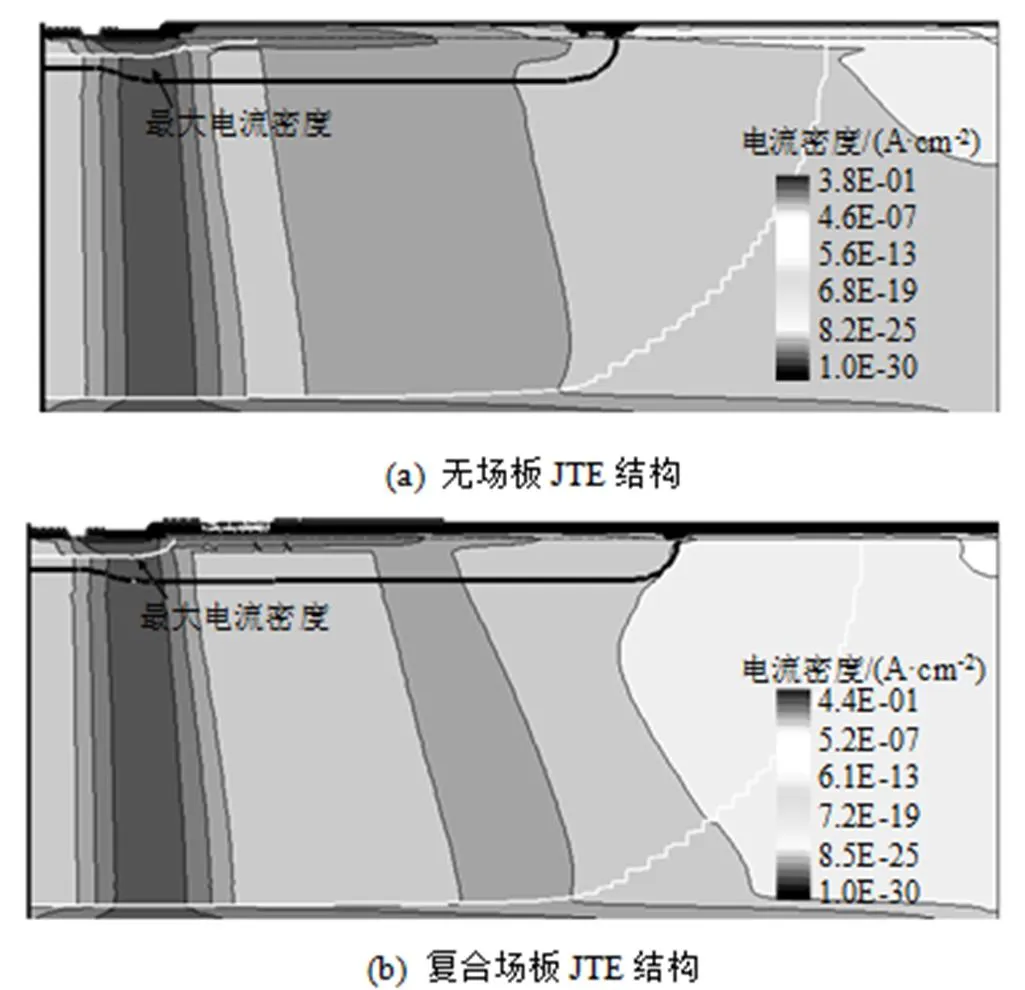

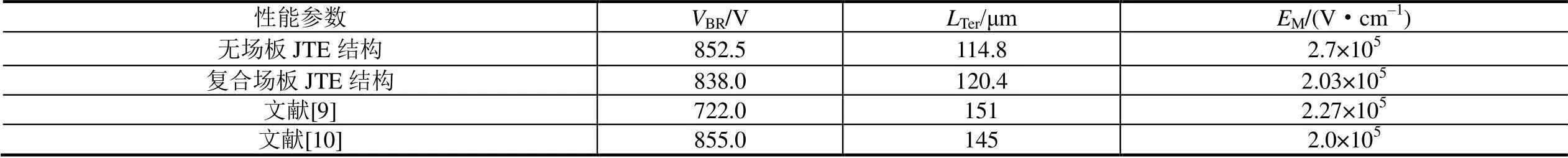

经优化后两种终端结构的主要参数如表1所示,其中M和Ter分布表示表面最大电场和有效终端长度。无场板JTE结构击穿电压达到852.5 V,表面最大电场2.7×105V/cm,超过工业界判断器件击穿时表面最大电场2.5×105V/cm这一安全值[8],而有复合场板JTE结构表面最大电场为2.03×105V/cm,小于此安全值,可靠性较高,其击穿电压达到838 V,满足了设计要求。图6所示为两种终端结构的电流密度分布模型,击穿均发生在电流密度最大处。

表1 两种终端结构的主要参数

Tab.1 Parameters of the two termination structures

图6 两种JTE结构的电流密度分布模型

为了更好地说明复合场板JTE结构的可靠性,图7给出了界面态电荷对优化后两种结构击穿电压的影响。相比无场板的JTE结构,有复合场板的JTE结构能很好地消除电荷的影响,击穿电压受界面态电荷的影响较小;而无场板JTE结构的击穿电压随界面态电荷增加急剧下降,ss达到8.0×1011cm–2,击穿电压不能满足700 V的要求。

图7 有无场板结构下JTE击穿电压受界面态电荷的影响

将本文与其他文献中终端结构的仿真结果列于表2进行对比。文献[9]采用复合场板与场限环终端结构,调整场板长度、场限环环宽和环间距,优化电场分布,表面最大电场为2.27×105V/cm,有效终端长度为151 μm,均高于本文;文献[10]采用类似文献[9]的终端结构,表面最大电场为2.0×105V/cm,耐压达到855 V,有效终端长度却比复合场板JTE结构的多了24.6 μm,芯片面积占用很大。综上所述,本文设计的复合场板JTE结构有效终端长度和最大表面电场均有所降低,提高击穿电压的同时改善了器件的可靠性。

表2 不同终端结构的比较

Tab.2 Comparison of different terminal structures

3 结论

本文采用单区JTE技术及复合场板技术设计了一款700 V VDMOS的终端结构,Pbody区覆盖5.3 μm长的JTE区,保证了主结由浅阱向深阱过渡。通过优化JTE注入剂量、JTE长度和金属场板长度,在120.4 μm的有效终端长度上实现了838 V的耐压。其表面最大电场为2.03×105V/cm,减小了界面态电荷的影响,具有较高的可靠性且工艺步骤简单,与高压深阱VDMOS工艺兼容,在提高击穿电压的同时,较好地提高了芯片面积的利用效率。

[1] BALIGA B J. Fundamentals of power semiconductor devices [M]. USA: Springer, 2008, 149-154.

[2] 张彦飞, 吴郁, 游雪兰, 等. 硅材料功率半导体器件结终端技术的新发展[J]. 电子器件, 2009, 32(3): 538-546.

[3] LIAO C N, CHIEN F T, TSAI Y T. Potential and electric field distribution analysis of field limiting ring and field plate by device simulator [C]//International Conference on Power Electronics and Drive Systems. NY, USA: IEEE, 2007: 451-455.

[4] DENG X C, XIAO H, WU J, et al. Design, fabrication and characterization of mesa combined with JTE termination for high-voltage 4HeSiC PiN diodes [J]. Superlatt Microstruct, 2015, 88: 167-173.

[5] WU Z L, GAO Y M, LIANG S J, et al. Analysis of the FP-JTE planar junction termination [J]. Solid-State Electron, 1998, 42(11): 2097-2100.

[6] RONG H, MOHAMMADI Z, SHARMA Y K, et al. Study of breakdown characteristics of 4H-SiC Schottky diode with improved 2-step mesa junction termination extension [C]//European Conference on Power Electronics and Applications. NY, USA: IEEE, 2014: 1-10.

[7] MAHAJAN A, SKROMME B J. Design and optimization of junction termination extension (JTE) for 4H-SiC high voltage Schottky diodes [J]. Solid-State Electron, 2005, 49(6): 945-955.

[8] 高玉民. 平面终端技术[J]. 半导体技术, 1992(5): 13-20.

[9] 李宏杰, 冯全源, 陈晓培. 一款700 V VDMOS结终端结构设计[J]. 电子元件与材料, 2014, 33(10): 89-92.

[10] 干红林, 冯全源, 王丹, 等. 700 V VDMOS终端结构优化设计[J]. 半导体技术, 2014, 39(4): 274-278.

(编辑:陈渝生)

Optimization design of single-zone JTE termination with field plate

PAN Xiaowei, FENG Quanyuan, CHEN Xiaopei

(Institute of Microelectronics, Southwest Jiao Tong University, Chengdu 611956, China)

To improve availability of die size,a 700 V VDMOS termination structure was designed by using single-zone junction termination extension (JTE) and multiple field plate. The relationships among JTE’s injection dose, its length and metal-plate length with breakdown voltage were analyzed by using simulation software Sentaurus TCAD. The parameters were optimized to improve the distribution of electric field at the surface and bulk of the termination. At last, the termination possesses advantages of breakdown voltage up to 838 V with the length of 120.4mm, meanwhile, the peak of surface field achieves 2.03×105V/cm, less than the criteria (2.5×105V/cm) of device breakdown in industry. And interface charge has less effect on the termination. Therefore, this termination structure improves the utilization efficiency and reliability of the terminal area with good compatibility and no more extra processes.

JTE; multiple field plate; VDMOS; breakdown voltage; peak of surface field; interface charge

10.14106/j.cnki.1001-2028.2016.11.009

TN386

A

1001-2028(2016)11-0038-04

2016-09-20

冯全源

国家自然科学基金重点项目资助(No. 61531016);国家自然科学基金面上项目资助(No. 61271090);四川省科技支撑计划项目资助(No. 2015GZ0103;No. 2016GZ0059)

冯全源(1963-),男,江西景德镇人,教授,博士,主要从事数字、模拟及射频集成电路设计,E-mail: fengquanyuan@163.com ;

潘晓伟(1989-),男,湖北潜江人,研究生,研究方向为功率半导体器件的研究与设计,E-mail: 1092493207@qq.com ;

陈晓培(1982-),女,河南漯河人,博士研究生,研究方向为功率半导体器件工艺与设计,E-mail: xpch2010@163.com。

2016-10-28 14:04:40

http://www.cnki.net/kcms/detail/51.1241.TN.20161028.1404.009.html