24GHz防撞雷达抗干扰任意波形设计

马玉贞,陈够喜,崔成林,徐艺伟

(1.中北大学 计算机与控制工程学院,山西 太原030051;2.成均馆大学 情报通信学院,韩国 水原440746)

0 引 言

由于普通毫米波雷达频带有限,FMCW 信号形式单一,随着驾驶辅助系统(advanced driver assistance systems,ADAS)的普及,在多雷达同时工作的场合,雷达信号相互干扰概率增大,无法高分辨率地观测目标物体的速度和距离,使雷达系统虚警率提高,灵敏度降低,影响ADAS系统的安全性。从而,雷达间相互干扰近年来成为国内外学者研究的热点问题[1-4],针对新体制雷达的干扰问题,多在信号处理阶段采用匹配接收和相干处理等抗干扰技术,同时提出多种傅里叶变换算法来抑制干扰。上述消除干扰的方法使得硬件实现变得困难,并降低了信号处理模块的处理速度,使得系统探测目标的实时性减弱。

在分析文献 [5-7]的基础上,利用DDS芯片AD9958和ARM 微控制器Arduino DUE[8]提出一种任意波形设计方法,此信号波形可根据需求由软件设计产生,区别于传统FMCW 信号,可降低虚警率。利用24GHz防撞雷达系统进行测试,该信号可降低信号间干扰程度,相位噪声低,开发周期短,提高了防撞雷达系统的安全性。

1 设计原理

1.1 FMCW 基本原理

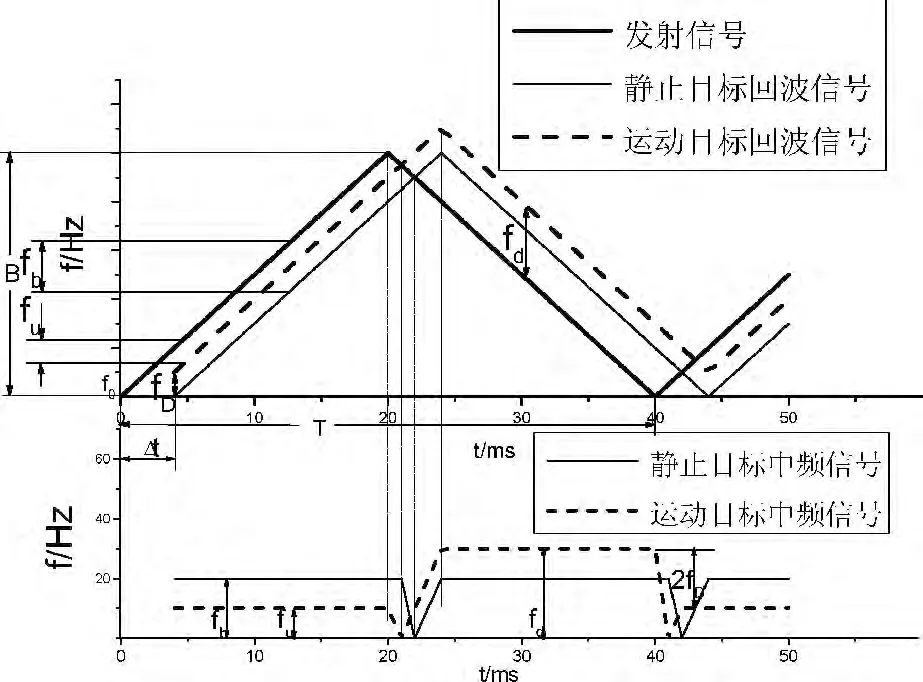

FMCW 雷达通过天线向外发射一系列调频连续毫米波,并接收目标的反射信号,然后通过混频、滤波等处理得到中频信号,根据多普勒频移原理对中频信号进行分析,计算出目标物体的距离和速度,FMCW 一般采用三角波调制信号。FMCW 测速测距原理如图1所示。根据多普勒原理,可以算出目标与雷达的相对速度和距离

式中:c——光速,fD——多普勒频移量;fu——三角形上升沿差频;f0——调频初始频率;T——信号周期;B——信号带宽。回波信号与发射信号通过混频器后得到的是时域中频信号,进行快速傅里叶变换 (fast Fourier transform,FFT)计算得到频率值,将其带入式 (1)、式 (2)计算出目标相对距离和速度。

图1 FMCW 基本原理

1.2 任意波形设计原理

FMCW 毫米波测速测距基本原理被广泛应用于汽车防撞雷达系统中,具有构造简单,带宽较大,发射功率低等优点。在雷达信号源设计中,越来越多的采用数字技术设计信号源,其中DDS 芯片在数字信号源设计占据重要地位[9-11]。但由于雷达系统的普及以及FMCW 信号带宽有限,雷达传感器间相互干扰程度加重,造成系统误判,虚警率增大。为提高信号抗干扰性能,采用DDS芯片AD9958和ARM 微处理器Arduino DUE,提出一种任意波形设计方法。该设计利用AD9958线性调频特性,由Arduino DUE微控制器设置控制字,控制字经由简单的SPI通信总线,存入SPI缓存器中,然后置低I/O_UPDATE 信号线,控制字由I/O缓存器写入各寄存器中。P2引脚负责DDS线性扫频模式开启和结束,在ARM 微控制器的程序设计中改变AD9958中P2的变化频率,使其动态控制AD9958线性扫频模式的上升和下降时间,从而控制DDS信号形式,输出任意波形。图2为抗干扰任意波形的一种形式,后续将该信号输入24 GHz雷达收发系统,进行雷达系统测试。

图2 信号波形

该信号周期为700 ms,带宽为100 MHz,其中包括4个梯形信号。利用第4个波形的特殊性,在多雷达传感器环境中可明显区分该发射信号,可降低信号互扰程度。进行数字信号处理时,经由地杂波滤除[12]操作后雷达系统可正确识别目标,抗干扰性能提高。

2 软硬件设计

2.1 硬件设计

24GHz防撞雷达抗干扰任意波形的硬件设计模块如图3 所示,主要由PC 机、Arduino 微控制器、DDS 芯片AD9958、SPI通信接口等组成。由于动态改变分频器值N电路结构复杂、锁频效果不理想,此处固定PLL 模块锁相环整数倍分频数值N,设定为512,采用动态改变基带信号频率的方法,使得雷达系统输出FMCW 波形。测试时将AD9958产生信号先经过放大器,然后经由雷达发射机进行射频发射。PC机通过Arduino提供的开发环境,为硬件设置所需的信号参数,Arduino DUE 通过USB 接口与PC 机通信,下载程序到微控制器,USB同时为Arduino DUE 提供电源,然后使用SPI通信总线向AD9958 写入控制字,使其工作在线性调频模式,输出线性调频信号。

相位噪声作为信号源设计中的主要指标,来源较广,此设计中他们来自DDS内部结构、DDS外部电路、参考信号源、参考时钟等,其中DDS芯片内部影响因素包括累加器相位截断、ROM 存储器有限字长、DAC 有限分辨率和内部噪声,此设计采用25 Mhz晶振作为参考时钟信号,512次倍频后相位噪声将会恶化26.02dB。DDS采用的相位截断技术、波形幅度量化及DAC的非理想性特征引起的杂散抑制差是DDS的一大缺点,本设计采用文献 [13]的DDS杂散抑制技术,同时在后续测试中测试相位噪声大小。

图3 AD9958-PLL设计结构

2.1.1 直接数字频率合成器AD9958

DDS芯片的高集成度、频率相应速度快等特性,使得DDS在信号源设计方面得到广泛应用[14]。AD9958是美国ADI公司的CMOS型DDS集成电路,采用高级DDS技术,AD9958由两个直接数字频率合成器内核构成,其32bit频率控制字使得该芯片具有很高的频率分辨率,最小扫频步进为0.12Hz;具有较高的频率转换速度,最小驻留时间为8ns;简单的串行口控制;最高时钟频率为500 MHz。

AD9958 的SPI通信总线使用简单、传输速度高达800 MHz,能够有效提高雷达调频信号的生成速度,相比于传统频率合成技术更快速、灵敏。串行I/O 端口控制,具有调相、调幅功能,可以实现多片AD9958 同步,在MIMO 雷达的波形设计中也越来越广泛。

2.1.2 Arduino DUE与AD9958接口电路设计

作为本频率合成器的控制部分,Arduino DUE 基于Atmel公司SAM3X 系列微控制单元ARM Cortex-M3,是首位32位Arduino ARM 核微控制器,SAM3X 支持SPI通信。本设计将Arduino作为SPI的主设备,芯片AD9958为从设备。基本过程为:通过USB接口将上位机程序下载到Arduino DUE微控制器中,Arduino DUE 通过其SPI通信总线控制AD9958芯片,使其产生任意波形,如单频信号、调频连续波形信号。Arduino DUE 微控制器输出电压为3.3V,AD9958要求输入电压为同样为3.3 V,接口不需要增加额外电路进行降压,图4为SPI接口电路连接框架。

图4 Arduino和AD9958接口连接

2.2 软件系统实现

使用DDS产生扫频信号,需要配置各寄存器值,系统软件采用模块化设计,对DDS和控制板进行初始化,然后对需配置的寄存器写入控制字,AD9958初始化后默认进入单频模式。为保证最小的非线性失真须确保信号波形有最小的扫频步进或最小的驻留时间,在本设计中增加一自动计算模块,根据输入波形参数自动选择最小扫频步进或者最小驻留时间,并计算出最佳扫频步进及相应驻留时间。软件设计思想如图5所示。

图5 软件设计

3 实验测试

3.1 应用测试

所设计任意波形信号将作为24GHz防撞雷达的输入,实验测试分两组:AD9958 直接线性调频信号和连接24GHz雷达收发机后的射频发射信号。测试采用130nm CMOS工艺设计集成的24GHz雷达收发机[15],测试环境所用雷达模块如图6所示。直接线性调频信号接入24GHz雷达收发机,设置频率范围为47.167 97MHz~47.363 28MHz,输出信号经过放大器放大,然后调频到24.15 GHz~24.25GHz,达到24GHz雷达收发机的输入标准,此时系统消耗功率为1.53 W,连接雷达收发机512次倍频后射频发射,此时系统消耗功率为2.376 W,射频信号范围为24.15GHz~24.25GHz。此测试环境在韩国境内实现,与国内24GHz频段短距离车载雷达设备使用频率略有偏差。

图6 测试硬件外观

图7和图8是利用频谱分析仪对两组信号进行分析的结果图。可以看出,信号输出范围严格满足系统要求,经由雷达收发机后信号锁频,能够达到24GHz防撞雷达的频率范围,同时相位噪声也满足要求。两种测试结果的相位噪声见表1。

图7 直接线性调频信号 (左)和相位噪声 (右)

图8 雷达射频发射信号 (左)和相位噪声 (右)

表1 相位噪声

3.2 性能分析

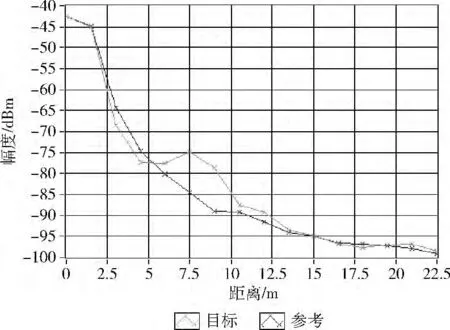

将设计的任意波形信号应用于24GHz雷达系统,采集系统信号进行分析处理,结果如图9所示,与图2进行对比,可见,此信号能满足设计标准,较好的达到设计要求。在雷达系统7.5m 处放置一待测物体,对接收的信号进行FFT 变换,分析处理结果。如图10所示,在多干扰雷达系统环境中,应用该设计信号可准确测出目标物体,系统抗干扰性能提高。

图9 设计信号的采集波形

图10 雷达系统测距频谱

4 结束语

基于DDS采用Arduino DUE设计的任意波形,测试信号频率步进为0.12Hz,驻留时间为24ns。由实验结果可以看出,该信号源频率响应时间快、分辨率高、相位噪声低,通过程序设计控制产生任意波形,抗干扰性能提高,被应用于24GHz防撞雷达系统进行测试与分析。基于Arduino DUE微控制器使得开发周期缩短,电路设计简洁,为新型雷达的研制节约时间成本,在车载防撞雷达系统的应用中具有广阔前景。

[1]Hasch J,Topak E,Schnabel R,et al.Millimeter-wave technology for automotive radar sensors in the 77 GHz frequency band [J].IEEE Transactions on Microwave Theory and Techniques,2012,60 (3):845-860.

[2]Goppelt M,Blocher HL,Menzel W.Analytical investigation of mutual interference between automotive FMCW radar sensors[C]//Microwave Conference(GeMIC),2011:1-4.

[3]Schipper T,Harter M,Mahler T,et al.Discussion of the operating range of frequency modulated radars in the presence of interference[J].International Journal of Microwave and Wireless Technologies,2014,6 (3-4):371-378.

[4]Torres F,Frank C,Weidmann W,et al.The norm-interferer-An universal tool to validate 24and 77GHz band automotive radars[C]//9th European Radar Conference,2012:6-9.

[5]Schipper T,Mahler T,Harter M,et al.An estimation of the operating range for frequency modulated radars in the presence of interference[C]//European Radar Conference,2013:227-230.

[6]Luo TN,Wu CHE,Chen YJE.A 77-GHz CMOS automotive radar transceiver with anti-interference function [J].IEEE Transactions on Circuit and Systems,2013,60 (12):3247-3255.

[7]Li Mu,Tong Xiangqian,Shen Ming,et al.Research on key tchnologies for collision avoidance automotive radar[C]//Intelligent Vehicles Symposium,2009:233-236.

[8]Arduino DUE 中文介绍 [EB/OL].[2012-10-23].http://www.arduino.cn/thread-2216-1-1.html.

[9]Ayhan S,Vu-Duy V,Pahl P,et al.FPGA controlled DDS based frequency sweep generation of high linearity for FMCW radar systems [C]//7th German Microwave Conference,2012:1-4.

[10]Zhang J,Yang H,Huang B,et al.Design and implementation of DDS signal generator based on Verilog HDL [C]//4th Electronic System-Integration Technology Conference,2012.

[11]Jia L,Sun W,Ma X,et al.The design of signal generator with DDS based on FPGA [J].Applied Mechanics and Materials,2014 (644-650):4427-4430.

[12]SHAO Wei,CHENG Hao,LIU Guoqing.Rejection of ground clutter based on wavelet transform [J].Computer Engineering and Design,2012,33 (2):793-797 (in Chinese).[邵伟,程浩,刘国庆.基于小波变换的雷达信号地杂波滤除[J].计算机工程与设计,2012,33 (2):793-797.]

[13]ZHANG Haitao,MIAO Pu,LI Zhen.Research and simulation on DDS spurious suppression [J].Computer Simulation,2011,28 (2):397-401 (in Chinese). [张海涛,苗圃,李珍.DDS杂散抑制技术研究与仿真 [J].计算机仿真,2011,28 (2):397-401.]

[14]DENG Yueping,XIAO Tiejun.Design and implementation of parallel DDS signal generator based on FPGA [J].Computer Engineering and Design,2011,32 (7):2319-2323 (in Chinese).[邓岳平,肖铁军.基于FPGA 的并行DDS信号发生器的设计与实现 [J].计算机工程与设计,2011,32 (7):2319-2323.]

[15]Kim Seong-Kyun,Cui Chenglin,Kim Byung-Sung,et al.A fully-integrated low power k-band radar transceiver in 130nm CMOS technology [J].Journal of Semiconductor Technology and Science,2012,12 (4):426-432.