CMOS全集成低压低功耗锁相环设计概述

徐 伟,黄乐天,丁召明,李 强

(1.上海华虹宏力半导体制造有限公司,上海201203;2.电子科技大学 微电子与固体电子学院,四川 成都610054)

CMOS全集成低压低功耗锁相环设计概述

徐 伟1,黄乐天2,丁召明2,李 强2

(1.上海华虹宏力半导体制造有限公司,上海201203;2.电子科技大学 微电子与固体电子学院,四川 成都610054)

锁相环是现代电路系统尤其是通信系统中非常重要的一个部分,通常锁相环的性能指标很大程度上影响着整个系统的整体性能。随着人们对低压低功耗的需求日益增长,低压低功耗锁相环的研究也成为了非常热门的方向。总结了近年来在低压低功耗锁相环研究方向具有代表性的技术和解决方案。低压下电荷泵电路电流的匹配、低压低功耗的压控振荡器的实现以及低压下较快速度的分频器设计都成为低压低功耗锁相环设计必须要面对的难题。

低压;低功耗;锁相环

0 引言

由于近年来生物电子、物联网的发展,可穿戴设备以及超小型物联网终端等对于中短距离通信提出了越来越高的要求。因为这些设备都不具有有线的电源,一般采用电池、无线充电、自然能量收集等方式给系统提供能量。所以低压低功耗成为这些设备需要克服的首要问题。而锁相环的功耗在整个系统能量损耗里面占有非常大的比例,减小锁相环的功耗已经成为一个迫在眉睫的瓶颈。为了减少锁相环的功耗,也为了适应数字电路供电电压降低的发展趋势,低压锁相环成为了研究人员共同的兴趣。

锁相环主要由鉴频鉴相器、电荷泵、环路滤波器、压控振荡器以及分频器几大部分组成,低压低功耗的设计要求对电荷泵、压控振荡器以及分频器的设计提出了新的要求和挑战。本文主要归纳了近年来国际上针对于低压低功耗锁相环的实现提出的新的技术和电路。

1 低压电荷泵

电荷泵电路的发明对锁相环的发展起到了至关重要的作用,在电荷泵正常的工作电压范围内,可以将电荷泵的增益看作是无限大。正常电压工作的电荷泵为了保证电流源和电流沉能够对后续电路进行等电流的充放电,需要使用共源共栅的电流镜,才能保证流入和流出的电流不会有较大的失配。如果使用共源共栅结构,加上开关的两个MOS管,整个电荷泵从电源到地则需要串联6个MOS管,所以在低压条件下是不被允许的。

用于低压下的电荷泵电路一般都放弃共源共栅电流镜结构带来的匹配上的优势,这样就可以在电源到地的通路上减少两个MOS管对电压的损耗。

1.1 运放反馈补偿电荷泵

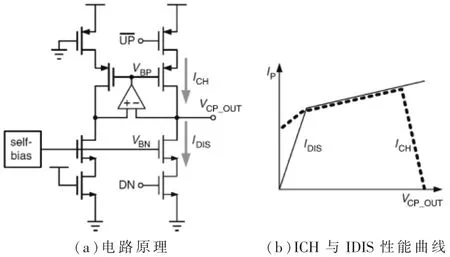

由于低电源电压限制了共源共栅电路的使用,必须要有其他的技术来保证电荷泵电路中对环路滤波电路的充放电匹配。文献[1,2]则提出了用运算放大器对电荷泵的偏置电路进行补偿的技术。图1(a)[1]中相对于普通电荷泵引入了一个运算放大电路,对电荷泵因为输出电压不同导致ICH和 IDIS电流的不匹配进行补偿。从图中可以看出,反馈运放通过控制VBP来达到使电荷泵输出相匹配的效果。虽然通过图1(b)中可以看出,电荷泵的ICH和 IDIS的电流得到了匹配,但是 ICH和 IDIS的电流会随着电荷泵的输出电压的不同而变化。

图1 单端补偿的电荷泵电路

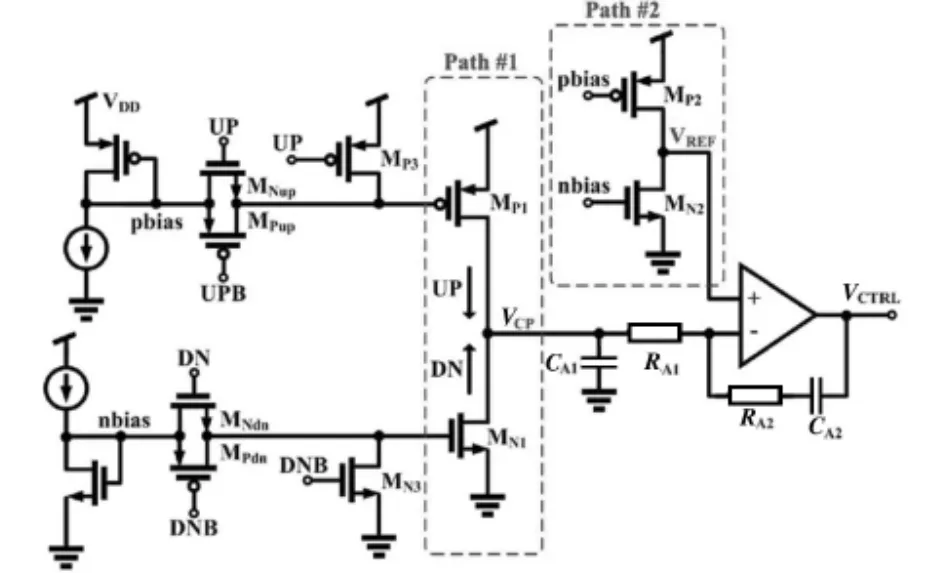

为了解决 ICH和 IDIS电流随输出电压变化的问题,文献[3-5]中新提出电荷泵的二级补偿电路。图2[5]中二级补偿电路的引入不仅仅减少了ICH和IDIS的电流的不匹配情况,还保证了ICH和IDIS的电流不会随着电荷泵的输出的不同而变化。图中电荷泵电路有两级复制反馈电路,第一级补偿电路控制 VBP2,使得充电电流 ICH2与放电电流 IDIS1相同;第二级补偿电路控制 VBN2,使得放电电流IDIS2与充电电流ICH1相同,所以最终所有的充放电电流都相同。

图2 二级补偿的电荷泵电路

1.2 运放隔离电荷泵

为了避免电荷泵因为输出电压不同导致对后续电路的充放电电流的不匹配,一种直观的解决方案就是保证电荷泵输出电压不变。文献[6]中提出使用有源滤波电路,将压控振荡器控制电压 Vctrl和电荷泵输出隔离。电路原理如图3所示。

图3 运放隔离的电荷泵电路

图3中电荷泵电路的第二部分(Path#2)是第一部分(Path#1)的复制,它们拥有相同的 NMOS偏置和 PMOS偏置,因为在第二部分电路中的开关(MP2,MN2)都一直处于导通状态,并且 VREF电压使得通过 MP2和 MN2的电流与通过 MP1和 MN1的电流相同。由于运放的原因,VCP和 VREF保持相同,所以使得第一部分的 UP和DN的电流在不同的工艺、电压和温度下保持匹配。不过值得注意的是在设计电荷泵时,需要保证第一部分的MOS管尺寸与第二部分完全一致,并且画版图的时候需要格外小心。这样才可以减小因为第一部分与第二部分不匹配所产生的锁相环输出参考噪声。

1.3 开关配对技术

由于没有了共源共栅结构的电流偏置,并且因为电源电压较小,给开关的导通过驱动电压也很小,致使开关要做得较大才能保证开关有较小的导通电阻。所以,开关信号的馈通就成了一个比较严重的问题。为了消除信号馈通对电路造成的影响,文献[7]引入了开关配对技术。开关配对技术能够产生一个与时钟信号对偏置电路产生的时钟馈通相反的信号,能从一定程度上抵消时钟馈通对偏置电路的稳定性的影响。开关配对技术的电荷泵电路如图4所示。

图4 开关配对技术的电荷泵电路

2 低功耗压控振荡器

压控振荡器作为锁相环的核心模块之一,其工作频率范围决定整个锁相环能够输出的频率区间,它的频率增益影响整个锁相环的带宽和相位裕度。而压控振荡器主要分为两个大类,一类为电感电容压控振荡器,另一类为环路压控振荡器。电感电容压控振荡器具有噪声性能好、频率增益小的特点,而环路压控振荡器则占用面积小、工作频率范围宽。两类压控振荡器各有所长,在不同的应用场合下,研究人员会选择不同类型的压控振荡器。由于需要实现低压低功耗的压控振荡器,普通结构已经不能满足人们的需求,各类新型结

构的压控振荡器也逐一被研发出来。

2.1 基于体驱动的环路振荡器

体驱动技术是解决低压下阈值电压限制最有效的技术之一,并且体驱动最典型和常见的应用是低压下运算放大器的设计。体驱动最大的好处是它允许输入的电压可以为零值、负值甚至少量的正值。所以体驱动技术可以使电路的输入电压范围达到普通电路所无法满足的宽度,并且在超低电压(<300 mV)下应用体驱动技术的电路的输入范围可以达到轨到轨。

图5[6]中所示的压控振荡器电压则是应用了体驱动技术,压控振荡器的控制电压由图中PMOS管MP1与MP2的体端输入,从而控制各个延迟单元的时延,达到控制压控振荡器频率的作用。不过由于基于体驱动的环路振荡器频率增益不高,为了避免由于工艺、电压和温度变化使压控振荡器无法在需要的频率范围工作,一般需要用到控制振荡器偏置电流的方式粗略地调整压控振荡器频率范围(图5中 VAFC)。

图5 基于体驱动技术的环路振荡器

2.2 基于可变电容的环路振荡器

绝大多数环路振荡器都用了控制偏置电流的方式来改变压控振荡器的频率,但是对于低压下的环路振荡器而言,阈值电压的限制使振荡器的输入范围变得非常窄。解决这种问题的方法一为用2.1中介绍的体驱动技术,另一种是用可变电容负载控制每一级压控延迟单元的时延[7]。图6中的压控振荡器不仅仅是像传统压控振荡器一样用了偏置电流去控制压控振荡器的频率,而且还在每级延迟单元用了可变电容负载。图6(a)中的NMOS电流偏置阵列给整个压控振荡器提供电流,并且由5位的控制字来补偿由于工艺、电压和温度差异引起的变化(粗调)。而每一级延迟单元的可变电容则是对压控振荡器的输出电压进行较为精细的调整。

图6 基于可变电容的环路振荡器

2.3 变压器反馈电感电容压控振荡器

传统电感电容压控振荡器的交叉NMOS管直接连在了地上,所以压控振荡器的输出电压范围极限为正负电源电压。并且电压很低的情况下,VCO振荡的过程中MOS管有较长一段时间处于截止状态,且导通状态下也没有较高的过驱动电压。

使电感电容压控振荡器能够在低压下使用,一种命名为变压器反馈的结构被研发了出来[8]。在变压器反馈的压控振荡器中(如图7),交叉 NMOS对的源端接在了变压器上。由于变压器的原因,VS可以变化到比地还要低的电压,以至于使压控振荡器的输出电压范围大大增加。所以,对于同样的输出电压范围,这种类型的压控振荡器可以工作在更低的电压条件下。

图7 变压器反馈LC压控振荡器

3 低压下高速分频电路设计

一般为了满足D触发器的速度需求,单相位时钟技术得到了较为广泛的应用,如图8,这种电路的优点为:不需要输入差分信号,只需单一相位的时钟信号即可;并且此电路相较于普通的D触发器而言,所使用MOS管数量有明显减少,且每个信号的负载减小,使得整个电路的速度得到较大提高。但是,这个电路由于是基于电荷存储的,在MOS管关断时会有一定的漏电流,所以电路需要有一定的刷新周期才能保证正常工作。即是,电路不能工作在很低的频率下,需要工作在至少10 MHz以上频率的电路。扩展单相位时钟技术的二分频器如图9所示。

图8 单相位时钟D触发器

从图8的相位时钟D触发器可以看出,从电源到地串联着3个MOS管,为了进一步提高整个电路的工作速度,扩展单相位时钟技术被提出[9]。从图9的扩展相位时钟技术的二分频电路中可以看到,从电源到地的通路上只串联了两个MOS管,这样大大提高了电路的充放电能力,使整个电路的速度得到提高。

4 结论

本文总结了近年来的实现低压低功耗锁相环的一些关键技术,这些技术解决了目前实现低压低功耗所面临的电荷泵电流失配、压控振荡器控制电压输入范围窄、压控振荡器输出电压范围小以及分频电路工作速度低等一系列的问题。

[1]LEE J S,JIN W K,CHOI D M,et al.A wide range PLL for 64x speed CD-ROMs and 10x speed DVD-ROMs[J]. IEEE Trans.Consumer Electronics,2000,46(3):487-493.

[2]LEE J S,KEEL M S,LIM S I,et al.Charge pump with perfect current matching characteristics in phase-locked loops[J].Electronic Letters,2000,36(23):1907-1908.

[3]BOU-SLEIMAN S,ISMAIL M.Dynamic self-regulated charge pump with improved immunity to PVT Variations[J]. IEEE Trans.Very Large Scale Integr.(VLSI)Syst.,2014,22(8):1716-1726.

[4]HA K S,KIM L S.Charge-Pump reducing current mismatch in DLLs and PLLs[C].in Proc.EEE Int.Symp.on Circuits and Systems,2006.

[5]HWANG M S,KIM J,JEONG D.-K.Reduction of pump current mismatch in charge-pump[J].Electronic Letters,2009,45(3):135-136.

[6]MOON J W,CHOI K C,CHOI W Y.A 0.4-V 90-350-MHz PLL with an active loop-filter charge pump[J].IEEE Trans. Circuits Syst.I,Reg.Papers,2014,61(5):319-323.

[7]CHEN W H,LOKE W F,JUNG B.A 0.5-V,440-μW frequency synthesizer for implantable medical devices[J]. IEEE J.Solid-State Circuits,2012,47(8):1896-1907.

[8]KWOK K C,LUONG H C.Ultra-Low-Voltage High-Performance CMOS VCOs using transformer feedback[J].IEEE J.Solid-State Circuits,2005,40(3):652-660.

[9]SOARES J N,VAN NOIJE W A M.A 1.6-GHz dual modulus prescaler using the extended true-single-phaseclock CMOS circuit technique(E-TSPC)[J].IEEE J.Solid-State Circuits,1999,34(1):97-122.

Design techniques for low-voltage low-power phase-locked loops

Xu Wei1,Huang Letian2,Ding Zhaoming2,Li Qiang2

(1.Shanghai Huahong Grace Semiconductor Manufacturing Co.Ltd.,Shanghai 201203,China;2.School of Microelectronics and Solid-State Electronics,University of Electronic Science and Technology of China,Chengdu 610054,China)

Phase-Locked Loop(PLL)is one of the most important modules in communication systems.The characteristic of the PLL affects the performance of the whole system.With the increasing requirement of low-voltage and low-power,research on lowvoltage and low-power PLL becomes famous.This work sums some of the recent outstanding methods and techniques in low-voltage and low-power PLL.Some difficult issues must be solved when someone wants to design a low-voltage and low-power PLL,such as the mismatch current of charge pump,voltage-controlled oscillator and fast-speed divider,which are much more difficult under the strict of low voltage and low power.

low-voltage;low-power;PLL

TN432

A

0258-7998(2015)05-0021-04

10.16157/j.issn.0258-7998.2015.05.001

2015-03-06)

徐伟(1957-),男,高级工程师,主要研究方向:集成电路设计、超大规模集成电路制造与工艺。

黄乐天(1984-),男,博士研究生,讲师,主要研究方向:混合信号集成电路设计、新型片上异构系统。

李强(1979-),男,博士,教授,主要研究方向:低压低功耗集成电路设计、生物医疗电子、模数转换器等。