维持电压和失效电流线性可调节的高压ESD器件

鄢永明,曾 云,夏 宇,张国梁(湖南大学物理与微电子科学学院 长沙 410082)

YAN Yong-ming,ZENG Yun,XIA Yu,and ZHANG Guo-liang(School of Physics and Microelectronics Science,Hunan University Changsha 410082)

维持电压和失效电流线性可调节的高压ESD器件

鄢永明,曾 云,夏 宇,张国梁

(湖南大学物理与微电子科学学院 长沙 410082)

为了研究可控硅结构的静电释放保护器件结构尺寸与性能的关系,采用0.5μm的5V/18V CDMOS工艺流片两组SCR ESD器件,使用传输线脉冲测试系统测试器件的性能参数。实验结果表明,随着N阱内P+区和P阱内N+区间距从6μm增加到22μm,ESD器件的维持电压线性增大,从2.29V升高到9.64V,幅度达421%;单位面积的失效电流线性减小,幅度约为63%。分析与仿真结果表明,该线性关系具有普遍适用性,可用于调节器件的健壮性和功率耗散能力,满足智能功率集成电路的高压ESD防护需求。另一组随着P阱内P+区和N+区间距增大,维持电压和失效电流呈现非线性的变化,但触发电压迅速降低,可用于实现高压SCR ESD器件的低触发电压设计。

静电放电;失效电流;维持电压;可控硅

由于具有强大的电流泄放能力,SCR(silicon controlled rectifier)结构的ESD(electrostatic discharge)器件常被用于智能电源集成电路的高电压电源ESD保护电路[1]。但是,SCR结构的寄生PNP BJT管和NPN BJT管之间的正反馈,在漏极和源极之间形成了一个的准中性区域和相对低的电场,从而极大地减少了维持电压,产生了闩锁风险,降低了器件的鲁棒性[2]。为了提高维持电压,研究人员提出了一些基于SCR结构的改进设计,如插入一个P+区[3],增加一个N型注入层[4],增加衬底与漏极的镇流器电阻[5]等,器件仿真也得到了广泛的应用[6]。此外,使用更大的阳极-阴极间距能增加器件的维持电压[7],延长P阱中的P+注入区长度增强器件的功率耗散能力[8],加大漏区到栅极间距有更高的二次击穿电流[9]。由此可见,改变SCR ESD器件的区域间距也可用于调节器件的健壮性或者放电能力,满足智能电源集成电路的高压ESD防护需求。为了研究高压SCR ESD器件的结构尺寸与器件性能的关系,本文设计了两组高压SCR ESD器件,采用标准的0.5μm 5V/18V的CDMOS工艺流片,使用传输线脉冲(TLP)测试系统获取器件工作的I-V特性曲线、维持电压和失效电流,并对测试结果进行了器件鲁棒性和放电性能分析。

1 器件结构和测试方法

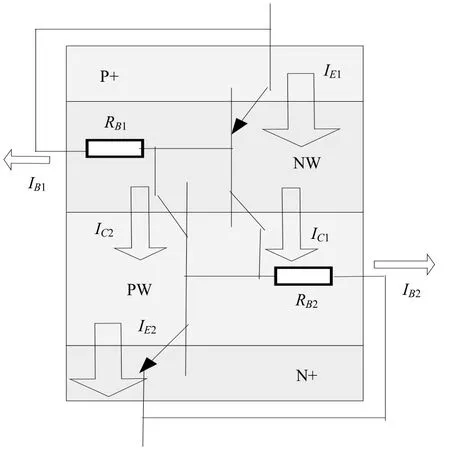

高压SCR ESD器件的横截面示意图如图1所示。每个器件测试区域的I-V特性曲线、维持电压Vhold和失效电流由Thermo Celestron-I传输线脉冲(TLP)测试系统测量,脉冲的上升/下降时间都是10ns,脉冲宽度为100ns,以模拟实际的ESD应力。维持电压是评估器件鲁棒性的重要指标,因为相对其他结构的ESD器件,SCR结构器件的维持电压非常低,正常工作条件下,衬底上的小噪声电流有可能使SCR ESD器件导通,产生破坏性的闩锁现象。很大程度上,SCR ESD器件的泄放性能由器件的二次击穿电流来确定,此时器件失效,二次击穿电流也称为失效电流。测试过程中,随着所加脉冲电压增大,器件的漏电流增大,规定检测到漏电流的值超过初值的30%为软击穿,此时的放电电流为软失效电流。如果检测到漏电流大于1μA,认为器件硬击穿损坏,此时的放电电流为硬失效电流。失效电流除以器件面积求得单位面积的失效电流(mA/μm2),使用单位面积的软失效电流Isoft和硬失效电流Ihard衡量器件的泄放效率和保护水平。

图1 高压SCR ESD保护器件横截面

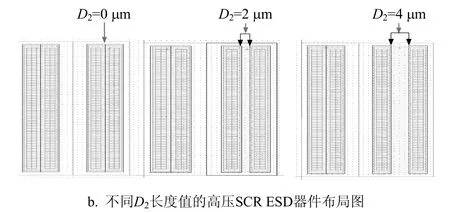

如图1所示,D1是N阱内P+注入区和P阱内N+注入区间距,D2是P阱内P+区和N+区间距。采用标准的0.5μm的5V/18V CDMOS工艺制造了二组高压SCR ESD保护器件,第一组中3个器件D1长度不同,面积分别为:1 251、1 675、2 099μm2,其他参数相同,ESD器件的布局顶视图如图2a所示。第二组中3个器件D2长度分别为0、2、4μm,面积为:1 177、1 251、1 357μm2,其他参数不变,布局顶视图如图2b所示。

图2 不同长度值的高压SCR ESD器件布局图

2 D1长度对器件性能的影响

2.1 实验结果

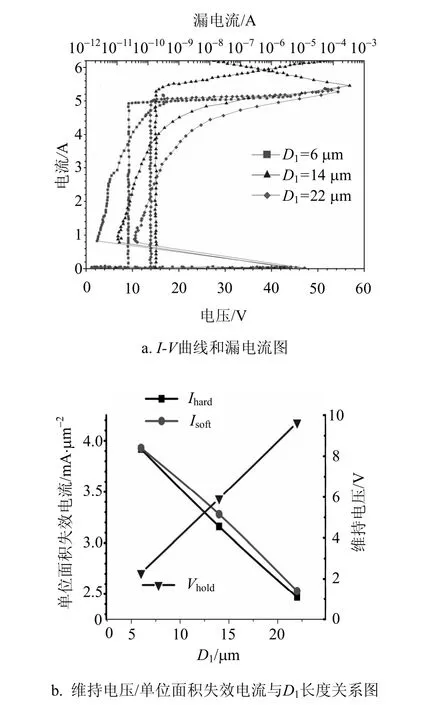

TLP测试的I-V曲线和漏电流如图3a所示。当D1长度从6、14μm增加到22μm,ESD器件的维持电压从2.29、5.92V升高到9.64V,如图3b所示,维持电压近似线性的增长,求得斜率约为0.465V/μm。采用失效电流除以器件面积求得单位面积的失效电流,经计算,单位面积的硬失效电流值Ihard分别为:3.92、3.28、2.53mA/μm2,单位面积的软失效电流值Isoft为3.92、3.16、2.47mA/μm2。单位面积的软失效电流曲线与硬失效电流曲线基本重合,随D1增长近似线性的递减,斜率测算约为−0.09mA/μm2·μm。

图3 不同D1长度器件的TLP测试图

2.2 理论分析

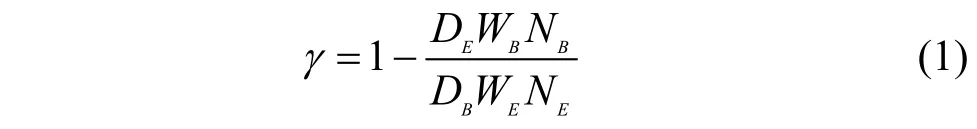

如图4所示,维持电压Vhold由载流子从发射区注入寄生BJT管的程度决定[10],因此,降低了寄生的BJT管发射效率可以增加维持电压。发射效率为:

式中,NB、NE是基区和发射区的载流子浓度;DB、DE是基区和发射区的少数载流子扩散系数;WB、WE是基区和发射区的宽度。如图1、图2a所示,随着D1增加,寄生NPN BJT和寄生PNP BJT基区宽度线性增大,由式(1)可知,两个寄生晶体管的发射效率线性降低,表明发射区载流子注入程度线性降低[11],维持电压随D1长度线性增长。Vhold增大加强了ESD器件的稳定性,器件的鲁棒性增强。

器件失效电流与D1长度关系可以从器件结构及热学原理方面分析。高压SCR ESD器件工作原理如图4所示,P阱、N阱之间的PN结是两个寄生BJT管的集电结,SCR ESD器件放电产生的能量主要耗散在集电结上。设Pcm(Ta)是环境温度Ta时器件集电结的最大耗散功率,最高结温为Tjm,当环境温度为T时,集电结最大耗散功率为:

由式(2)可知,集电结最大耗散功率Pcm与环境温度是负线性关系。

图4 器件的工作原理示意图

另一方面,集电结位于阱区内部,它的环境温度就是阱区(N阱与P阱的统称)温度T,由于ESD放电时间很短,可设器件为绝热体,同时采用单位面积失效电流值为评估值,可以不考虑器件体积变化导致的热容变化。如图4所示,ESD放电时,阱区有大电流流过,阱区电阻RB1和电阻RB2上消耗的能量转化为焦耳热,引起阱区温度(T)升高,当器件为绝热体并且不考虑热容变化时,温度值随焦耳热增加线性增长。进一步分析可知,D1长度就是阱区宽度,D1长度增长,阱区电阻RB1、RB2正比增大,器件工作时电流产生的焦耳热也正比增大(W=I2R),引起阱区温度(T)线性升高。因此阱区温度与D1长度也是正线性关系。

当器件为绝热体并且不考虑热容时,可以认为器件的失效电流值随Pcm值增大而线性增长,根据Pcm与T、T与D1长度关系,可知Pcm与D1长度是负线性关系。因此,器件的失效电流值与D1长度是负线性关系,随D1长度增大而线性减小。

2.3 应用与仿真分析

为了验证上述结论的普遍性,根据文献[12]的研究成果,采取拟合和仿真的方式,本文对实验结果进行了验证和深入研究。

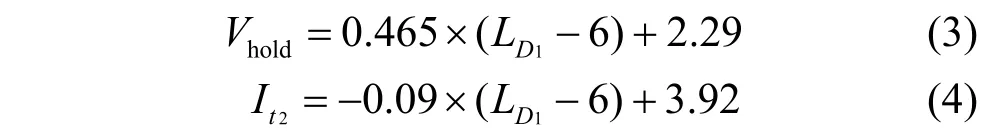

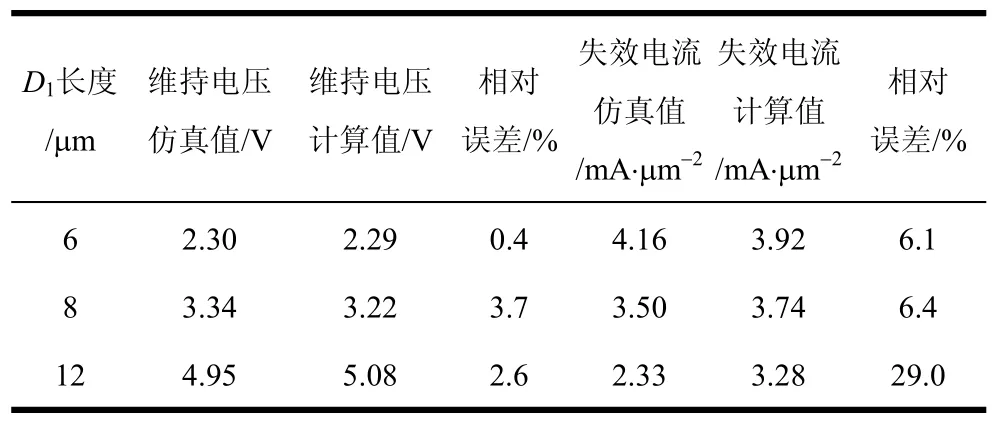

由于硬失效电流曲线与软失效电流曲线基本重合,采取软失效电流值为器件的二次击穿电流测量值,根据维持电压和单位面积的失效电流随D1长度线性变化的规律,拟合得到如下等式可得:

式中,It2是单位面积的二次击穿电流值,单位为mA/μm2。为了研究式(3)、式(4)的普遍性和适用范围,本文通过silvaco TCAD和spice仿真,得到3个器件工作时I-V曲线,如图5所示。

图5 不同D1长度器件的ESD放电I-V曲线仿真图

如图5所示,维持电压是器件第一次回扫路径的最小值,器件的二次击穿发生在曲线的顶点位置,电流值分别为:12.5、10.5和7mA/μm,除以电极宽度(3μm)得到单位面积失效电流值,维持电压和失效电流如表1所示。

如表1所示,维持电压的仿真结果和式3的计算结果基本吻合,可以在实际设计中通过改变此间距得到预计的维持电压,从而调控高压ESD保护器件的健壮性。失效电流仿真值与计算值相比较,在D1长度较小时误差小,但在D1长度较大时误差较大,原因如图2a所示,D1大,器件体积大,器件的热容增大,热传递效应不能忽略,因此式4适用于D1长度较小范围。

表1 D1长度变化时的维持电压和失效电流值

3 D2长度对器件性能的的影响

图6 不同D2长度器件的TLP测试图

TLP测试结果如图6a所示。随着D2长度增加,器件维持电压Vhold分别是2.4、2.29、3.689V,单位面积的软失效电流Isoft为3.81、3.92、2.70mA/μm2,单位硬失效电流Ihard为3.81、3.92、2.84mA/μm2,由图6b可知,单位面积的失效电流与维持电压与D2长度无线性关系,两者随D2长度变化正好相反,因此D2长度变化对器件的ESD鲁棒性和泄放性能的影响是相反的。但触发电压Vt1从44.48、44.02V减小到41.65V,随D2增加单调降低。原因如图4所示,D2长度的变化将导致NPN寄生管基区电阻RB2的变化,RB2阻值随D2长度增长而增加,小的雪崩电流就可以使NPN管的基-射极电压达到导通值(V=IRB2RB2≈0.6V),因此需要的雪崩击穿电压变小,导致器件进入放电保护工作状态的启动触发电压减小。

4 结论

根据实验结果和理论分析,高压SCR ESD器件的重要性能参数与结构尺寸密切相关,随着N阱内P+区和P阱内N+区间距增大,ESD器件的维持电压线性增大,而单位面积的失效电流线性减小,表明此间距变化对器件鲁棒性和泄放能力的作用相反。拟合得到维持电压和单位面积失效电流的线性公式,并软件仿真验证公式的准确性,结果表明,维持电压的计算值与仿真值误差很小,但失效电流计算值在间距较大时与仿真值偏差较大。另一方面,P阱内N+区和P+区间距增大,器件的触发电压单调下降,可用于高压SCR ESD器件的低电压触发设计。

[1]BART K,MERGENS M P J,TRINH C S,et al.ESD protection solutions for high voltage technologies[J].Microelectronics Reliability,2006,46:677-688

[2]TAZZOLI A,MARINO F A,CORDONI M,et al.Holding voltage investigation of advanced SCR-based protection structures for CMOS technology[J].Microelectronics Reliability,2007,47:1444-1449

[3]YANG Liu,WANG Yang,ZHOU Acheng,et al.Design,fabrication and test of novel LDMOS-SCR for improving holding voltage[J].Solid-State Electronics,2015,103:122-126

[4]PAN Hong-wei,LIU Si-yang,SUN Wei-feng.A novel latch-up free SCR-LDMOS with high holding voltage for a power-rail ESD clamp[J].Journal of Semiconductors,2013,34(1):53-57

[5]LIN Li-juan,JIANG Ling-li,FAN Hang,et al.Impact of parasitic resistance on the ESD robustness of high-voltage devices[J].Journal of Semiconductors,2012,33(1):59-63.

[6]SALCEDO A,LIOU J,LIU Zhi-wei,et al.Vinson TCAD methodology for design of SCR devices for electrostatic discharge(ESD)applications[J].IEEE Transactions on Electron Devices,2007,54(4):822-832

[7]GUIDO N,FRED K,JAN M L.Using an SCR as ESD protection without latch-up danger[J].Microelectronics Reliability,1997,37(10/11):1457-1460.

[8]JIANG Ling-li,ZHANG Bo,FAN Hang,et al.ESD robustness studies on the double snapback characteristics of an LDMOS with an embedded SCR[J].Journal of Semiconductors,2011,32(9):34-37.

[9]CHANG W J,KER M D.The impact of drift implant and layout parameters on ESD robustness for on-chip ESD protection devices in 40-V CMOS technology[J].IEEE Trans Device Mater Reliability,2007,7(2):324-332.

[10]VASHCHENKO V A,CONCANNON A,TER BEEK,et al.High holding voltage cascaded LVTSCR structures for 5.5 V tolerant ESD protection clamps[J].IEEE Trans Device Mater Reliab,2004,4(2):273-280.

[11]MENEGHESSO G,TAZZOLI A,MARINO F A,et al.Development of a new high holding voltage SCR-based ESD protection structure[C]//IEEE International Reliability Physics Symposium.Phoenix,AZ,USA:IEEE,2008.

[12]LI Wang,RUI Ma,CHEN Zhang,et al.Scalable behavior modeling for SCR based ESD protection structures for circuit simulation[C]//IEEE International Symposium on Circuits and Systems(ISCAS).Melbourne,Australia:IEEE,2014.

编辑 黄 莘

Investigation of High Voltage Electrostatic Discharge Devices with Adjustable Holding Voltages and Failure Currents

Electrostatic discharge(ESD)properties of high voltage silicon controlled rectifier(HV-SCR)ESD devices can be adjusted by their key layout parameters.Two groups of HV-SCR ESD devices with particular layout parameters were fabricated in 0.5 μm 5 V/18 V CDMOS process,and their current-voltage curves,holding voltages,and failure currents were investigated and characterized by a transmission line pulse test system,respectively.Experimental data shows that with increasing layout spacing from P+ implant in N well to N+ implant in P well,the holding voltage grows linearly from 2.29 V to 9.64 V,as much as 421%,but the failure current per area decreases linearly about 63%.Using analysis and simulation results,two equations for the holding voltage and failure current were generalized properly.They can be used as a guideline to adjust ESD robustness and performance of HV- SCR ESD devices in smart power integrated circuits.However,with increasing layout spacing from P+ implant to N+ implant in P well,this phenomenon can’t be found,but the trigger voltages of the devices decrease sharply,which can be used for low trigger voltage design of HV-SCR ESD devices.

electrostatic discharge;failure current;holding voltage;silicon controlled rectifier

TN335

A

10.3969/j.issn.1001-0548.2015.05.011

YAN Yong-ming,ZENG Yun,XIA Yu,and ZHANG Guo-liang

(School of Physics and Microelectronics Science,Hunan University Changsha 410082)

2015-01-17;

2015-05-29

国家自然科学基金(61350007)

鄢永明(1968-),男,高级工程师,主要从事SOC集成电路设计及器件可靠性等方面的研究.