基于边界扫描的一种电路板测试技术

陈宝华,宋晓东,王新洲(.青岛雷达声纳修理厂,山东 青岛 66000;.海军青岛舰船器材仓库,山东 青岛 66000)

基于边界扫描的一种电路板测试技术

陈宝华1,宋晓东2,王新洲1

(1.青岛雷达声纳修理厂,山东 青岛 266000;2.海军青岛舰船器材仓库,山东 青岛 266000)

边界扫描技术是复杂电路板测试和维修的有效手段,但是由于被测试电路板结构的限制,使该技术的应用受到一定程度的制约。如果通过设计适配器,将边缘连接器上的所有数据融合到边界扫描链路中,则能够提高电路板测试的完备性,有效完成故障检测和隔离。文章就上述过程进行了描述并提出了实现方法。

边界扫描;测试性;故障检测;故障定位

现场可编程门列阵(FPGA)和复杂可编程逻辑器件(CPLD)等大规模可编程器件发展迅速,单片规模已达到千万门级,器件提供的资源丰富,通过编程就可灵活方便地实现不同的电路功能,这类器件已成为现代数字电路的基本要素,在新的电子装备中的应用也越来越广泛。

随着大规模集成电路门数增加,功能增强,每个集成电路所需要的引脚数目也急剧增加,目前几百个引脚的集成电路已非常普遍,而小型化技术的发展使电路的封装形式从传统的双列直插式封装(DIP)形式发展到带引线的塑料芯片载体(PLCC)、一种集成电路的封装形式(QFP)、球栅阵列结构(BGA)等高集成度的封装形式,器件引脚的数量急剧增加,引脚的间距越来越小,甚至在电路的外观看不到引脚的存在。这样的器件构成的电路板,除了边缘连接器,利用传统的探针采集电路板内部的信号已经变得不可能,也就难以得到支持故障器件定位的足够的信息,直接导致故障隔离率的直线下降。解决这类电路构成的电路板的测试问题,边界扫描测试(BST)技术是有效的手段。

1 边界扫描技术与测试性设计

1.1边界扫描技术[1]

边界扫描技术是美国联合测试工作组(JTAG)为解决超大规模集成电路(VLSI)等新型电子器件的测试问题,提出的一种先进测试和测试性设计技术,随着标准的发展和完善,边界扫描测试技术已不局限于集成电路自身的测试,在模块及系统级的测试中也得到了快速发展和应用,并日趋广泛和成熟。据相关资料介绍,这项技术作为美国新型航空电子设备内建测试(BIT)采用的主要测试手段,在F-22、RAH-66、波音777等系统中得到成功应用。

1.2测试性与测试性设计

在GJB 2547A—2012 《装备测试性工作通用要求》中,测试性的定义是:产品能及时、准确地确定其状态(可工作、不可工作或性能下降程度),并隔离其内部故障的一种设计特性。测试性是在产品设计之初,通过测试性设计而赋予产品的一种固有属性,不因外部激励和测试方法的改变而发生变化。测试性反映的是产品为故障诊断提供方便的特性,其满足测试的程度取决于测试性设计,通过有效的测试性设计能够提高产品自诊断和外部诊断能力,从而方便有效地确定产品状态和进行隔离故障。

边界扫描技术的测试性设计的主要特点。

1)测试性设计方案标准化程度高,有标准器件支撑,可得到各种相关资源的支持。

2)有效减少了测试引线,可实现数字、数模混合电路和数字网络测试,可实现在线检测。

3)利用多模板测试维护总线可实现板级、组合级测试性设计。

4)利用边界扫描描述语言(BSDL)支持,故障检测率高,直接诊断到元器件。

5)为测试而附加的元器件少,给被测试单元(UUT)固有可靠性带来的负面影响小。

6)与当前装备数字化、智能化、网络化发展趋势相适应。

7)与当前大规模、超大规模集成电路的应用相适应。

2 边界扫描技术与电路板的设计研发[2]

为了顺利地实现边界扫描的可测试性,在产品研发阶段,需考虑以下几个方面。

2.1元器件的选型

元器件的选用,优先考虑符合以下要求的器件。

1)兼容IEEE 1149.1标准。

2)支持强制的SAMPLE/PRELOAD,EXTEST 和BYPASS 指令,支持可选的HIGHZ IDCODE 指令。

3)CPLD 器件兼容IEEE 1532标准。

4)具有独立的而不是双功能的边界扫描端口。

2.2扫描链布局

扫描链的合理布局,能够简化测试过程,提高测试效率,在布局时需考虑以下几个方面。

1)边界扫描端口的方便可达。优先考虑将扫描端口引到主边缘连接器,减少电路板上有限的空间占用。连接器使用率高,不能提供需要的引脚时,要保证测试数据输入(TDI)、测试数据输出(TDO)、测试时钟输入(TCK)和测试模式选择(TMS)4个基本端口能够方便地连接。

2)合理分区。不同厂商的器件,分配到不同的扫描链中,保证器件和配置软件的良好匹配,不同电压供电的器件,分配到不同的扫描链中。

3)控制扫描链的长度。在结合自动测试设备(ATE)进行综合测试时,单个扫描链需要的测试向量长度,应在选用的ATE能够提供的测试向量的长度范围之内。

4)信号的阻抗匹配。对于TCK高于10 MHz时,需要通过增加RC网络或串接电阻,调整匹配阻抗和抑制反射。

5)信号的缓冲。通过使用缓冲器(如54244),提高边界扫描输入信号的驱动能力,根据缓冲器和边界扫描器件间导线的长度,合理设置负载个数。

2.3对非边界扫描元器件的控制

对非边界扫描逻辑控制信号的访问:为了防止测试时的信号竞争导致器件损坏或测试不可靠,非边界扫描器件的控制信号必须连到边界扫描单元,以实现对该器件的非使能控制。

时钟信号的控制,有时需要对同步存储器读写的时钟信号进行控制,用测试时钟替代或将时钟关断。

对连接器的测试,可将连接器的引脚接至边界扫描器件的扫描单元,通过在连接器上外接的短接器,实现直通测试。

3 边界扫描技术在电路板检测时的应用

边界扫描技术对于含有支持边界扫描功能的器件的电路板的测试,是一种快速有效的方法,但是由于受到电路板结构的限制,在实际应用有一定的局限性,通过采取一定的技术手段,打破这种局限性,能够提高边界扫描技术测试时的故障覆盖率和隔离率。

3.1边界扫描技术在复杂电路板检测时的局限性[3]

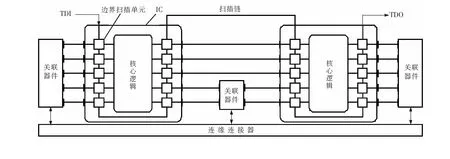

常见的包含边界扫描器件的复杂电路板核心功能由一只或几只支持边界扫描功能的复杂逻辑或功能器件构成,由于军用设备工作的环境相对恶劣,为提高其可靠性,电路板上核心器件与机箱总线之间往往有一些非边界扫描器件网络作为缓冲,直接与电路板的边缘连接器相连,如图1所示。

图1 复杂电路板的一般结构图

复杂电路板的一般结构中,边界扫描器件及其关联器件构成一个相对独立的网络,关联器件的部分引脚可以从边缘连接器到达,其状态能够通过边缘连接器来获取或改变;而另一部分引脚连接在边界扫描链路上(见图2),并且其状态与边界扫描器件核心逻辑相关,但是其状态能够通过边界扫描链路来获取或改变。

要达到电路板测试要求的故障覆盖率和隔离率,必须能够注入有效的激励和获取相应的响应。通过边缘连接器和边界扫描链路,均能获取部分信息,也能够通过这些信息分析电路板的某些工作状态,在实际工作时,由于关联器件与边界扫描接口和边缘连接器相连的两部分引脚的状态往往存在相互依赖的逻辑或时序关系,但这种关系由于边界扫描和ATE信号的不同步,难以反映出来,也就难以发现潜在的故障,不能满足预定的故障覆盖率和隔离率的要求。

3.2通过构建扫描链路实现电路板的全面测试

从上面的分析,可以看到,如果能够解决边界扫描和ATE信号的同步问题,将通过边界扫描链路和边缘连接器得到的电路板状态信息统筹处理,就能够实现电路板的全面测试。

实现同步的方法有2种,一种是将边界扫描链路和边缘连接器均连接到ATE的数字测试端口(见图3),用ATE来模拟边界扫描信号,从原理上来讲,方法简单方便,能够实现ATE和边界扫描严格的同步,便于数据的交换和使用,在此基础上,结合使用LASAR(逻辑自动激励与响应)等电路仿真软件,能够精准地定位故障部位[4],包括边界扫面器件和外围的非边界扫描器件(一般被称为CLUSTER),故障覆盖率和故障隔离率较高,美国泰瑞达公司的victory边界扫描测试方案是这种方法的代表,这种方法需要特定的ATE和测试软件,在现有的ATE上实现比较困难。

实现同步的另一种方法是,将边缘连接器上所有与器件连接的引脚,通过一个或数个支持边界扫描的器件,构成边界扫描扫描链路,通过这个增加的链路,来激励电路板上与边缘连接器相连器件,并获取器件的响应。如果考虑严格的时序,则可以将增加的链路和电路板上原有的链路“串接”起来,实现所有信号的同步发送和接收,如图4所示。

图3 测试同步实现方法一

图2 边界扫描器件及关联器件的连接图

图4 测试同步实现方法二

通过增加2个边界扫描器件,将所有边缘连接器上的信号融合到边界扫描链路中,通过边界扫描软件,透过边界扫描单元,方便地激励关联器件并读取其响应。当然,关联器件之间还会存在一些相互连接,这些节点通过边界扫描链路无法控制或获取其状态,但是,这些连接往往只有简单的一级或两级简单逻辑关系,在原始输入已知的情况下,使用多用表或示波器等简单工具,结合电路结构分析,很容易判断这些节点状态是否正确。

4 结束语

含有FPGA、CPLD等大规模且支持边界扫描技术的电路板,应用边界扫描技术进行测试是一种有效的故障诊断定位手段。在实际的使用过程中,根据电路结构,设计适配器,将边缘连接器上的信号融合到边界扫描链路中,能够极大地提高电路测试的完备性,有效完成故障的检测和隔离。如果通过研制专门的软件,将边界扫描的串行数据,变成并行数据,则可以将数据输入到LASAR仿真软件中,进行激励的有效性评价,并且提高故障定位的自动化程度。

[1] 赵红军,杨日杰,崔坤林. 边界扫描测试技术的原理及应用[J].现代电子技术,2005(11):20-24.

[2] 田仲,石君友.系统测试性设计分析与验证[M].北京:北京航空航天大学出版社,2003.

[3] 陈岩申,王新洲,张波.基于FPGA的电路板自动测试技术研究[J] . 计算机测量与控制,2010(7):1500-1502.

[4] 王新洲,张波.FPGA器件构成的复杂电路板的自动测试[C].宜昌:第十二届全国测试与故障诊断技术研讨会论文集,2011.

Boundary scanning is an effective measure for the test and maintenance of the complicated circuit board.But the technique is restricted in some degree because of the limitation of the tested circuit board structure.In this paper,a measure is put forward together with the course described.An adapter is designed and all the data on edge connector are mixed into the link circuit of boundary scanning,which can raise the completeness of circuit board testing and achieve fault testing and segregation effectively.

boundary scanning;testability;fault testing;fault position

U672

10.13352/j.issn.1001-8328.2015.06.005

陈宝华(1976-),男,山东沂南人,工程师,硕士,主要从事雷达装备维修保障方面的工作。

2015-06-16