基于SOPC的便携式频谱分析仪的研究

李新献

基于SOPC的便携式频谱分析仪的研究

李新献

李新献1李伟勤2施岱松2

1. 南阳医学高等专科学校;2.西南石油大学

李新献(1974)男,河南南阳,硕士研究生,毕业于西南石油大学研究生院,专业:计算机应用技术,方向:嵌入式系统;李伟勤(1976-)男,西南石油大学电信学院 通信工程教研室 副教授,现主要从事阵列天线设计、数字系统及优化算法等方面的研究工作。

本文采用可编程片上系统技术在FPGA中植入NIOSII软核作为系统的控制中心,利用FPGA中丰富的可编程逻辑资源和IP核来构成该嵌入式系统处理器的接口功能模块,再借助于AVALON总线,实现对外围模拟通道A/D转换器,存储器,LCD 显示器,键盘等硬件的控制。频谱分析核心算法是基于快速傅立叶变换(FFT)。通过傅立叶运算将被测信号从时域转换到频域,并分解成分立的频率分量,在频域中观测其频谱图,了解信号的特性,从而对信号进行分析诊断,这种基于数字信号处理的频谱分析已经应用于诸多领域并且发挥着重要作用。

概述

SOPC(System On Programmable Chip,可编程的片上系统) 是Altera 公司提出的一种灵活、高效的SOC解决方案,首先,它是片上系统(SOC),即由单一芯片完成整个系统的主要逻辑功能。其次,它是可编程系统,具有灵活的设计方式,可裁减,可扩充,可升级,并具备软硬件在系统可编程能力。结合频谱分析仪的原理,以ALTERA 公司提供的IP 核为基础,以分层次的硬件描述语言(VHDL) 作为系统功能和接口的主要描述手段,借助于 QUARTUSII 和 NIOSII ,MATLAB等EDA开发工具进行系统设计。根据实现的功能要求,用VHDL语言编写了整个系统的各个接口功能模块,在顶层模块中,对各个子模块进行了逻辑功能的连接,并对各个子模块及整体模块系统级的功能验证和仿真。最后生成系统,下载到开发板中,通过在NIOSII IDE环境中编写软件进行测试,并通过LCD显示,显示的结果与MATLAB中仿真的结果进行比较,验证结果的正确性。

系统总体设计

该系统从结构上分为AD采样单元,FFT运算转换单元,显示单元。系统使用FPGA内部实现的处理器NiosII作为系统嵌入式处理器,通过片上Avalon总线和高速A/ D采样芯片,FFT处理转换单元等相联系。A/D采样单元对外部的音频模拟信号每周期采样128点,再变换为左右声道分别是16位的数字量。FFT运算处理单元包括数据经FFT转换,转换后的复数经CORDIC算法求模及相位,最后再经过实数到整数的转换。此部分是由HDL语言编写的纯硬件电路来实现。它通过DMA方式将数据从TLV320AIC23接口中取出经FIFO缓存送到FFT处理单元,进行FFT变换,然后将转换后的实部和虚部经CORDIC算法求模,而指数保留,最后将求出的模和指数组成的实数再转化为整数,存到FIFO中,由DMA读出,送到LCD上显示,这样对应的音频信号的幅度频谱就可显示出来。 整个过程大部分使用硬件电路实现,CPU在其中的主要作用是任务调度,中断响应和启动DMA传输。

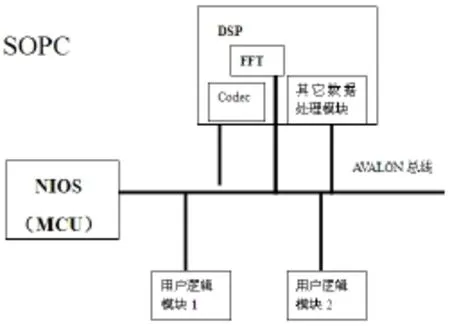

整个系统框图如图1。

图1 系统整体框图

图2 sopc 结构图

系统硬件设计

本设计是基于SOPC的思想来实现我们系统所要求的基本功能,随着可编程芯片的迅速发展,SOPC在数字信号处理方面的应用也越来越明显。其一般的结构框图如图2。

根据本设计的要求,结合SOPC技术的强大功能,我们利用片上系统的设计理念,定义了以下用户逻辑模块。

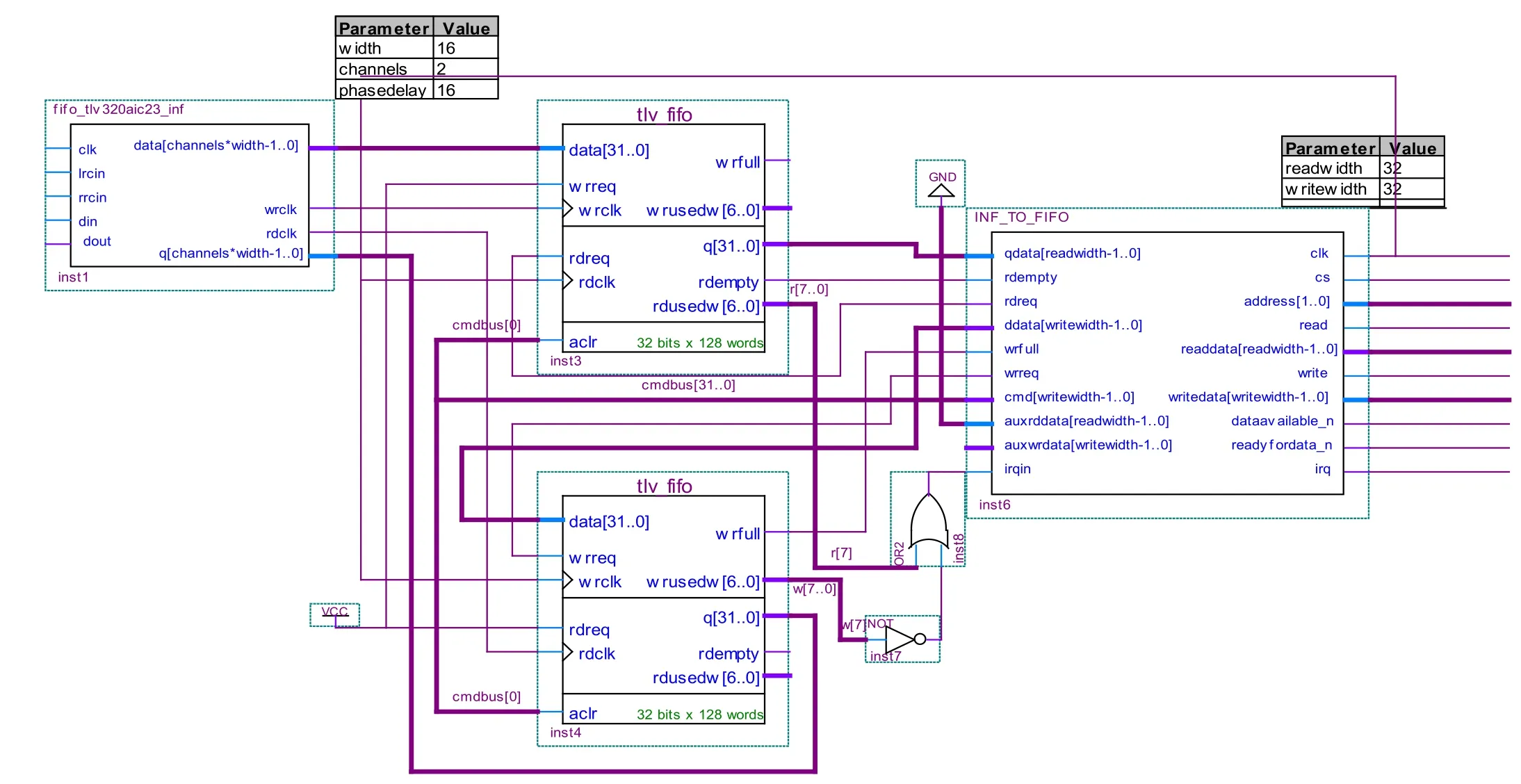

NiosII以DMA方式读取数据到FIFO中;其顶层模块FIFO_DMA如图3。

图3 FIFO_DMA 模块图

fifo 到 fft的接口模块fifo_fft

该接口模块是将数据传送到FFT运算单元,供FFT进行运算,经FFT转换后,又将转换后的数据取走,整个接口顶层模块有INF_TO_FIFO .bdf ,fft_fifo.bdf,fifo_to_fft.bdf, fft_to_fifo.bdf几个模块构成。因为FFT IP CORE是要付费的,因此不能将FFT IP CORE连同该接口模块一起加入到SOPC BUILDER 中。只能将该接口模块添加到SOPC BUILDER里面,而把FFT模块单独留在外面。这样在生成的cpu 中就留出了FFT 模块的接口,以便将FFT 模块同该接口模块相连。

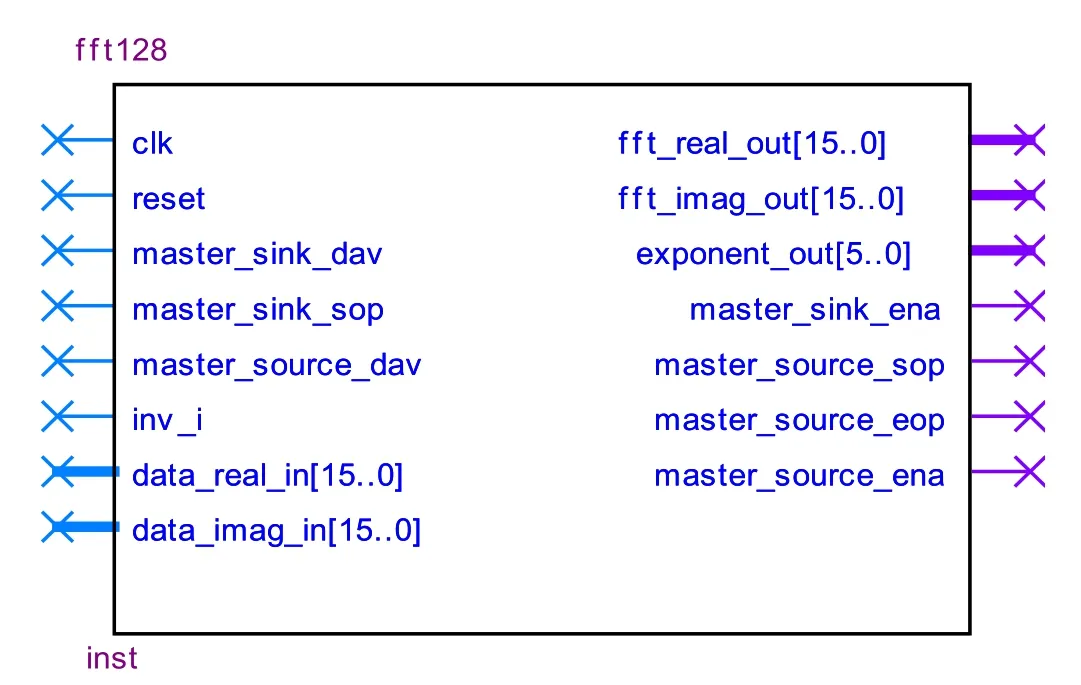

FFT 模块

在本设计中,为了缩短我们的开发周期,充分发挥ALTERA 公司提供的MegaCore的优势。我们采用了MegaCore 中的FFT IP CORE ,尽管它是要付费的,但是由于ALTERA的OpenCore Plus特性,即使不购买IP,也可以生成具有时效性的编程文件,通常在JTAG线拔掉一小时后,编程文件才会消失,这对验证此模块提供了很大的帮助,至少可以让我们看到它在硬件中的运行情况,其模块图如图4。

图4 FFT模块图

图5 FIFO_ CORDIC模块图

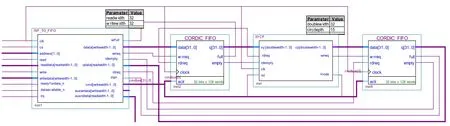

取模及相位模块

由于FFT转换后的数据是复数,我们要对其求模及相位,计算它的幅度频谱和相位频谱。在这里我们利用CORDIC算法 ,CORDIC(Coordinate Rotation Digital Computer)算法即坐标旋转数字计算方法,是J.D.Volder 于1959年首次提出,主要用于三角函数,双曲线,指数,对数的计算。该算法通过基本的加和移位运算代替乘法运算,使得矢量的旋转和定向的计算不再需要三角函数,乘法,开方,反三角,指数等函数。

其用硬件实现的模块图如图5。

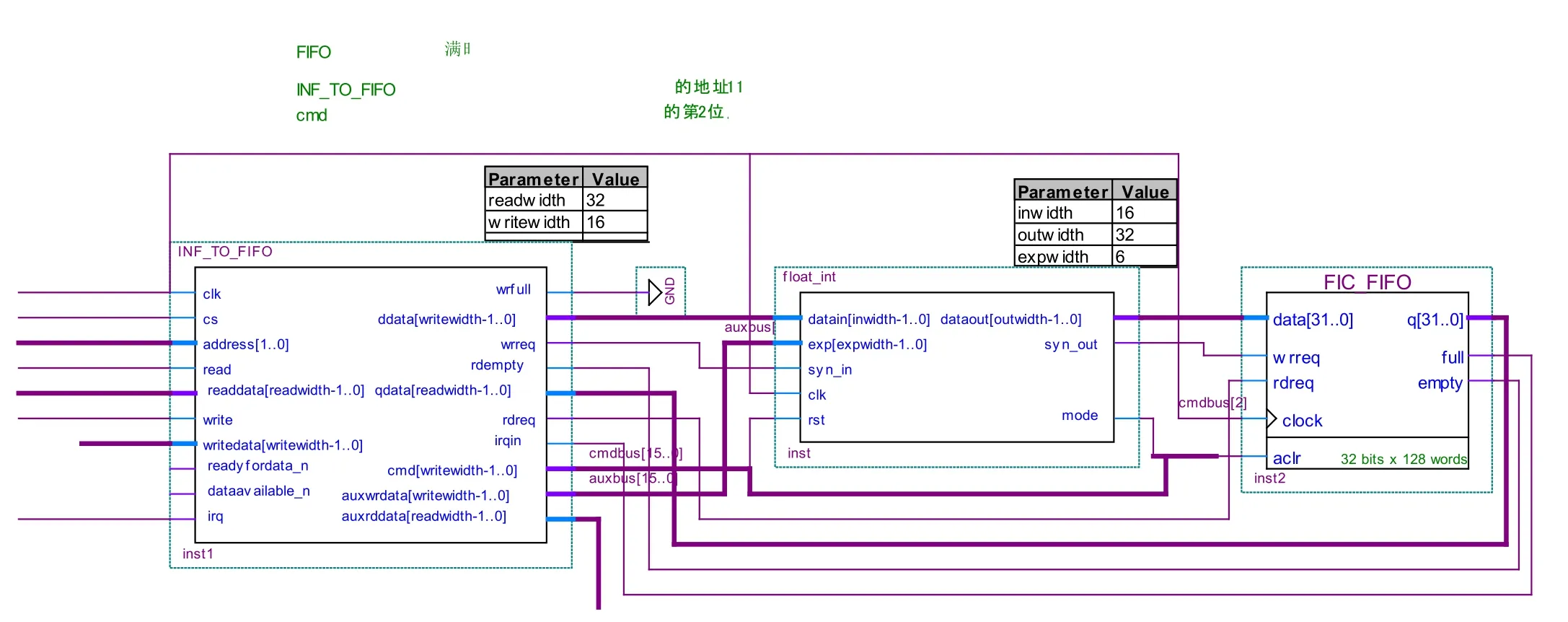

实数到整数转换模块

对于FFT转换后的实部,虚部和指数,其中实部和虚部在CORDIC模块中进行取模,指数部分保留起来。在这里我们通过该模块将求出的幅度连同指数组成的浮点数转化为整数,其模块图如图6。

图6 FIFO_FIC 模块图

AD 接口模块

此接口通过FIFO向上连接Avalon 总线并设为Slave模式,向下连接TLV320AIC23 数字音频接口DSP模式数据格式 。采用DMA方式传送数据,即每发送或接收到一个单元,都会自动触发DMA将其搬送到一个内部的Buffer,等FIFO半满时,再通过中断方式告诉CPU,启动DMA进行数据传输处理 。其顶层模块图FIFO_TLV320AIC23.bdf如图7。

图7 FIFO_TLV320AIC23 模块图

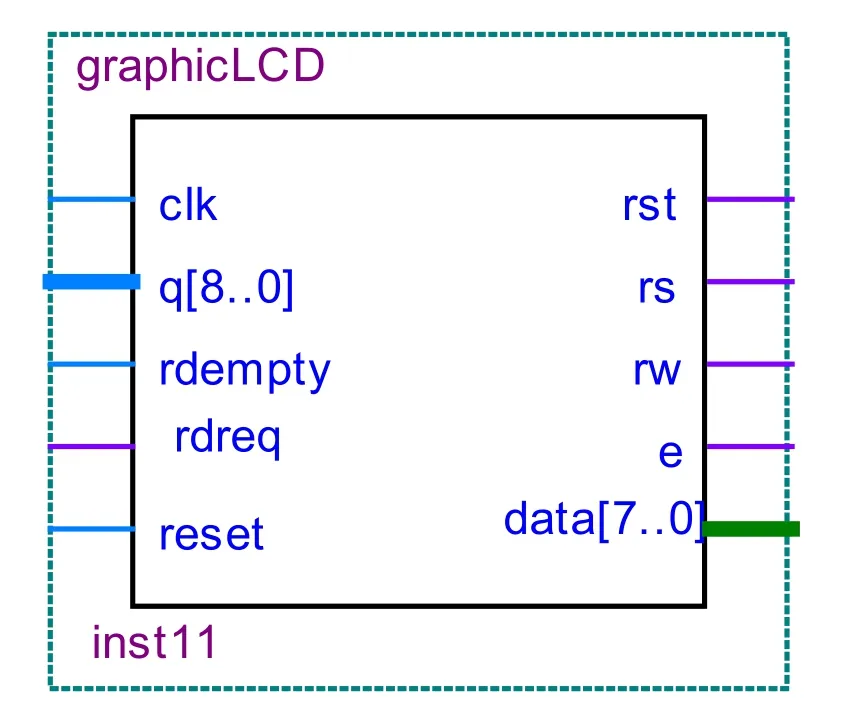

显示模块

本设计采用JDL 12864G型号液晶显示器,根据我们的功能要求,我们用VHDL语言编写了其硬件显示控制电路及接口模块,其显示接口模块如图8。

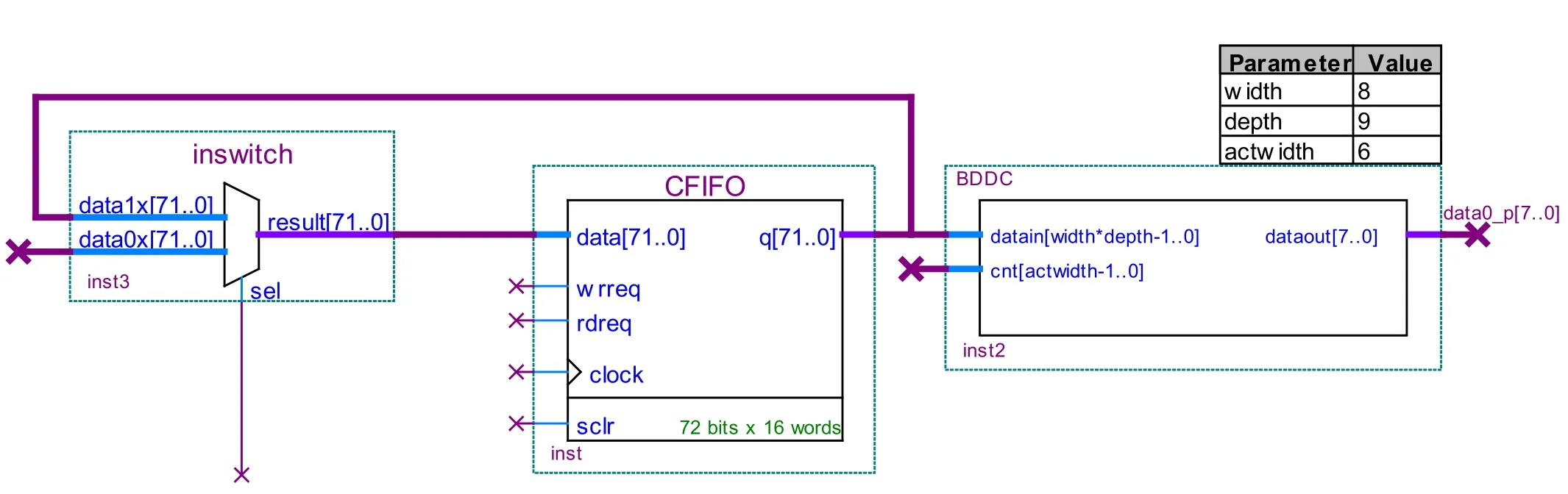

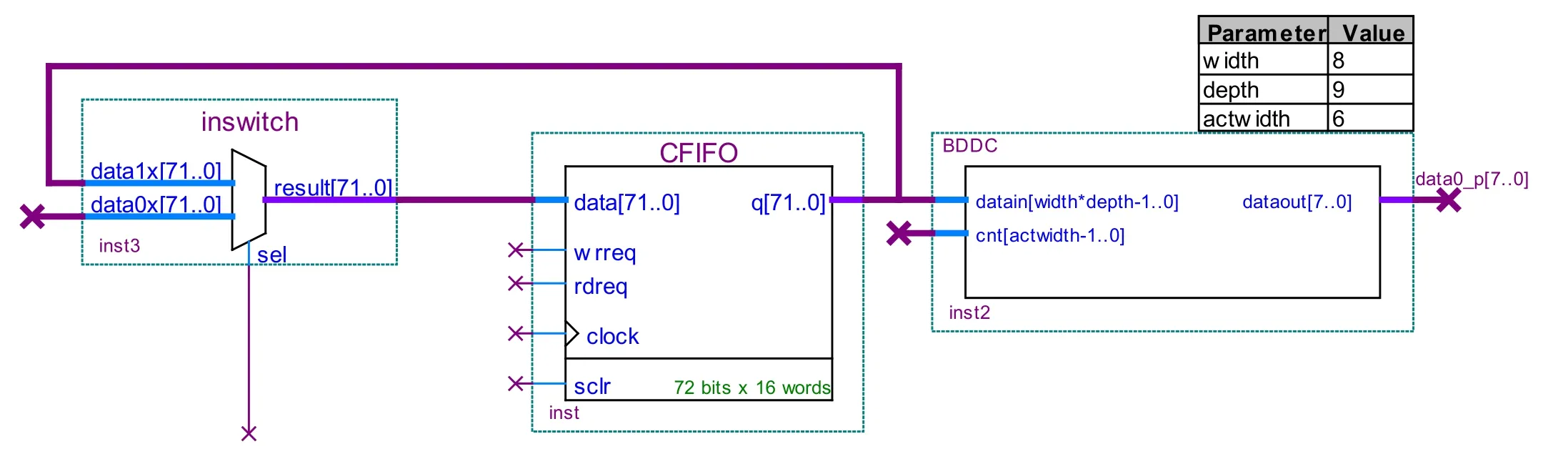

显示RAM中数据的产生方式我们采用全硬件实现,它以每8个数据为一组,为了循环利用输入的数据,我们在设计时,采用了一个选择电路如图9,当一帧数据未完全进入CFIFO 时,通道选择由CPU输入数据,并禁止CFIFO输出数据,当一帧数据完全进入时,通道选择CFIFO循环传送数据,并允许CFIFO输出数据。

图8 graphicLCD 模块图

图9 选择电路模块图

上面都是我们要用到的硬件电路模块,在SOPC BUILDER中,把FIFO_FFT.bdf , FIFO_ TLV320AIC23.bdf, FIFO_FIC.bdf ,FIFO_DDC_ LCD.bdf和FIFO_CORDIC.bdf 以添加新组件的方式加入到系统中。同时还要加入freedev_i2c,系统时钟,flash, sdram, dma等,并给它们分配基地址和中断,如图10所示。

图10 系统基地址、中断分配图

最后点击“generate”按钮,生成系统,生成的CPU顶层框图如图11。

系统软件设计

上电自检:系统上电后首先进行系统自检。查看设备是否正常。若有异常,通过LCD显示或报警。

系统初始化:若自检正常,检测系统是否允许启动,如允许启动,则系统初始化,首先设置AD采样芯片的工作参数为初始默认参数;清空FIFO保证不存在任何可能的错误数据;复位FFT;初始化LCD显示屏显示操作界面,然后系统处于接收命令状态,并且设置消息邮箱mbox1标识,它通知调度程序开始执行AD采样。

采样转换分析:调度程序开始等待消息mbox1,若一信号被置位,系统立即开始进行连续采样,将AD芯片采样的结果存放在FIFO中,当采样数据达到128个点后,FIFO发送HalfFULL信号给INF_TO_FIFO 接口单元,产生中断,并设置消息邮箱mbox2标识,它通知调度程序开始执行FFT转换,由CPU启动DMA传输,DMA将INF_TO_FIFO 接口单元的数据读到FFT的FIFO接口里面,由FFT处理单元进行数据转换,转换后的复数存到FFT的输出FIFO里面,指数单独存放在指定的寄存器里。当FIFO满时,产生中断,并设置消息邮箱mbox3标识,通知调度程序开始执行CORDIC模块,再由DMA通过INF_TO_FIFO 接口将复数数据读到CORDIC算法的FIFO里面,进行CORDIC求模及相位,求模后的数据存到CORDIC的FIFO里面,当FIFO满时,产生中断,并设置消息邮箱mbox4标识,通知调度程序开始执行实数到整数转换模块,同样,再由DMA通过INF_TO_FIFO 接口把幅度数据连同上面保留的指数送到实数到整数转换模块,转换后存到该模块的FIFO里面,当FIFO满时,产生中断,并设置mbox5标识,通知调度程序开始执行显示模块, 接着由DMA通过INF_ TO_FIFO 接口将转换得到的整数送到LCD显示控制器进行显示。显示完成后,再设置消息邮箱mbox1标识,它通知调度程序开始下一个循环调度。整个过程我们用统一的INF_TO_FIFO 接口,用DMA方式在两个模块之间进行数据传输,为我们下一步软件编程带来了很大的方便。使整个结构看上去也非常清晰。

图11 系统CPU模块图

停止运行:当系统接收到从键盘发出的停止分析命令时,系统首先停止AD采样芯片的采样工作,恢复为初始化参数,然后清空FIFO中所有数据,等FFT运算单元结束当前的FFT运算后读走数据。最后系统初始化等待下一个命令。

结合μc/os-II任务管理功能 ,在系统中创建了7个任务,包括主控响应任务,键盘扫描任务,AD采集任务,FFT转换任务,CORDIC算法任务,实数到整数转换任务,显示控制任务。其中主控相应进程优先级最高,它负责处理中断响应和中断响应进程的调用。采样控制进程负责管理采样控制。FFT管理进程负责数据传输到FFT IP core,进行FFT变换。CORDIC算法负责将复数求模及相位;实数到整数的转换负责将幅度和指数组成的浮点数转换为整数,显示控制进程负责数据的显示转换,控制LCD的显示。

系统结果验证

为了验证系统的正确性,我们把CYCLONE II EP2C8Q208C8 开发板上的LINE IN接口与我们PC机上的音频输出接口相连。通过PC机播放一段音乐,采集一帧音频数据,在Nios II IDE环境下,按照功能要求,进行编程,让该程序运行在我们设计的硬件基础上,最后通过LCD显示,可以看出采集信号的频谱图,如图12显示。为了验证显示结果的正确性,我们在Nios II IDE的调试窗口下,观察内存缓冲区中的音频数据,取此音频数据在MATLAB中进行仿真,图13是经过FFT变换后的频域仿真波形,即频谱图。与我们在LCD屏幕上看到的结果基本上是一致的,由此可见,该系统设计是符合我们的要求、是正确的。

图12 音频信号幅度频谱图LCD显示

图13 音频信号频域波形仿真图

10.3969/j.issn.1001-8972.2015.01.036