基于OMAPL138的嵌入式CNC控制器硬件平台开发*

左旭辉,高伟强,张伟文

(广东工业大学机电工程学院,广州 510006)

基于OMAPL138的嵌入式CNC控制器硬件平台开发*

左旭辉,高伟强,张伟文

(广东工业大学机电工程学院,广州 510006)

针对基于PC机和专用运功控制卡的传统数控系统的不足,以及基于ARM和DSP的多处理器在通信上的不足。提出基于多核异构的OMAPL138处理器的嵌入式处理方案,构建CNC控制器的硬件控制系统,同时利用FPGA的现场可编程特性完成控制器扩展模块设计。该设计解决了PC机所缺乏的实时性以及资源的专用性问题和多处理器通信数据丢失、易出错、难维护的缺陷,并实现了现代CNC系统所需求的高性能、模块化、柔性化以及开放性。

CNC控制器;多核异构;OMAPL138;FPGA;硬件平台

0 引言

数控系统正朝着开放性、可重构、多功能的高性能方向发展,所以中高档数控系统要求能够提供与用户交互的人机界面、执行操作的控制器件以及与控制部件通讯的设备接口。具体就是要求数控系统能够运行具有图形用户接口的实时性操作系统,提供友好的图形用户界面、NC图形编辑/编程及其仿真功能,丰富的NC传输接口,强大的网络通讯、监控能力;能实时地满足大量高速、高精度的浮点运算要求,实现多轴联动插补,五轴RTCP控制,3D空间刀补运算,速度前瞻及高性能加减速控制,误差控制补偿等复杂控制算法,同时要满足联动插补周期不大于500μs的条件;能够提供精确的插补周期、良好的计算能力、通讯能力和在线可编程能力,适应不同机床运动学模型的伺服驱动要求,满足机床运动控制结构的可重构、可扩展/裁剪要求。

硬件作为软件的载体,能满足这些条件的CNC运动控制器也是提高CNC系统性能的关键。目前,控制平台主要是采用PC+控制卡,包括PC+NC(分为PC嵌入NC、NC嵌入PC等)和PC全软集成NC等系统结构[1],基于ARM的控制平台和基于DSP的控制平台。但对于高性能CNC数控系统,PC机系统过于复杂,造成资源浪费;DSP能提供高速数据处理能力,但不能满足复杂加工需求;对于多线程控制、数据交互处理、人机界面操作,则是ARM处理器所擅长的;而对于系统的接口扩展与替换,弱实时任务处理则是FPGA处理器的优势。所以差异化的集成处理器将是高性能CNC控制器的最好选择。特别是多核技术的发展,使嵌入式处理器的性能不断完善。本文的方案是采用DaVinci系列的异构双核处理器OMAPL138为核心,以高性价比的CycloneII系列FPGA为辅助,构建高性能嵌入式CNC控制器的硬件平台。

1 控制单元结构和资源

充分利用了OMAPL138双核架构的优势和Cyclone FPGA的丰富资源,可进一步解决传统数控系统上的可靠性、开放性和可重构的局限问题。

(1)DaVinci系列化双核架构

DaVinci系列双核架构是将两个处理器核集成在单个硅片上,ARM与DSP之间的数据交互通过共享内存即可实现,大大增强了数据传输的稳定性和效率。OMAPL138处理器就是基于这样的一种结构,这种ARM+DSP的差异化集成模式,使应用模块和处理模块分开,能够同时满足应用在运算能力和控制能力上的要求,并且简化了系统设计的复杂性。在CNC系统中利用该一块芯片就可以使用ARM来实现系统管理、人机界面等弱实时任务;DSP来实现插补运算、数据处理等强实时任务。

(2)硬件浮点运算能力

OMAPL138处理器是同时包含有主频最高为300MHz的ARM9核和TMS320C6748DSP核的双核处理器[2]。C6748是一个具有32位运算精度的定点浮点数字处理器核,该内核频率可以支持DSP内核进行高精度的实时数据处理,浮点格式为高性能数控系统执行复杂控制算法并实现高精度、高动态范围和定点运算提供支持。

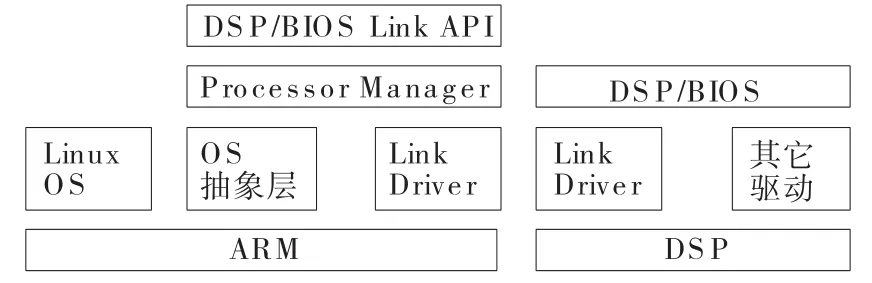

(3)ARM_DSP通信

DaVinci处理器的ARM_DSP核在通信方式上区别于传统意义上多处理器用外部布线及传输控制指令的通信方案,而采用共享内存和中断的方式。通过内存映射,处理器外设与内存统一编址,使ARM与DSP共享内存空间,共享内存提供了在任意数量的进程之间进行高效双向通信的机制[3];再通过中断方式,将数据放在共享内存上,然后给对方一个中断,对方在中断中接收数据,这样只需要通过函数操作就可以完成双核之间的通信。相比于独立的DSP与ARM之间通过总线的数据传输方案将更加可靠与稳定,减少了后期数据传输出错及维护的频率。具体是通过软件DSPLINK来实现,DSPLINK的软件架构[4]如图1所示。

图1 DSPLINK的软件架构

DSPLINK即DSP/BIOS Link是基于DaVinci架构处理器的通信软件,通过提供一套通用的API,从应用层抽象出ARM与DSP的物理连接特性,并实现ARM与DSP之间的通信。通信中一些关键数据,例如大块数据的地址指针等,是通过DSPLINK中的软件模块MSGQ(MSGQ可以实现轮询等待和中断方式)来实现的,大量数据交互则通过CMEM(CMEM用来实现内存分配或地址空间转化)来实现。在Linux系统操作中选择OS抽象层中包含DSPLINK需要的OS服务部件,运行DSPLINK中的软件模块,通过Link Driver进行ARM与DSP之间的数据传输和DSP的运行等操作。而Processor Manager层维护一个针对所有模块的Book-Keeping信息,通过API给用户提供Link Driver的控制操作。

(4)丰富的内部存储和外设资源

ARM核内有16KB的数据Cache和16KB的L1程序Cache;DSP核采用了二级缓存结构,包括32KB的数据Cache、32KB的L1程序Cache和256KB的L2统一映射SRAM,该二级高速缓存结构可以为载入、处理及存储请求提供服务,也可以为CPU提供高速、高效的数据共享。在ARM核和DSP核间还有可被ARM核和DSP核及片外存储器访问的128KB的片上RAM。

在外设资源上包含有1个EMIFA接口;一个EMIFB接口;2个SPI接口;2个IIC接口;3个UART接口;一个USB2.0和一个USB1.1接口;一个EMAC控制器;一个LCD控制器;一个UPP接口等。这些丰富的外设资源可以为控制器提供存储接口、与UART和USB等接口设备通信的接口,这样就减少了控制器外围电路的设计规模。

(5)FPGA芯片的丰富内部资源

FPGA选用Altera公司Cyclone II系列的EP2C8芯片,该芯片内有8256个逻辑单元,182个I/O口,多达18个18×18嵌入式乘法器等,可以满足系统对数据接口和逻辑处理的需求。同时还提供公共外部存储器接口、I/O协议和可参数赋值的IP[5],是外部接口的扩展和内部模块的编写设置更加方便。

2 CNC控制器功能设定

根据器件本身的软硬件结构特点和资源,将数控系统所要实现的功能分别在核心板和基础板上实现。

(1)核心板功能介绍

核心板要实现对整个数控系统的控制,利用OMAPL138中的ARM核作为控制部分,DSP核作为数据处理部分。具体过程是通过ARM端控制的界面层接收到用户输入的信息或者读取存储器里面的NC代码后,先进行预处理,再将处理后的数据发送到DSP核;DSP核作为数据处理模块对接收到的指令、数据进行译码、编译程序等工作,并对处理后的插补和控制信号进行速度处理和插补运算,再通过与伺服系统的速度、位置反馈信号比较,生成插补指令和数据,发送给伺服系统,完成对控制对象的控制[6]。

(2)基础板功能介绍

基础板要实现对数控系统外设的逻辑控制和部分非实时模块的设计。具体是利用多块FPGA分别进行高速设备和低速设备外部接口的扩展,以满足多轴联动高性能数控系统对大量同步接口的需求。利用FPGA的在线可编程特性,从硬件意义上实现对串口的多路扩展,并根据需要激活接口的IP模块,实现实现串口、并口还是总线通信的灵活转变。另外,利用VerilogHDL编写的IP模块,在FPGA内是并行处理的,加快了数据的处理速度。所以将电机联动控制的功能模块,数据的采集反馈模块,检测模块都在FPGA内实现。

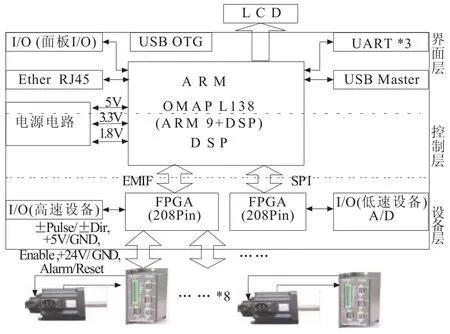

3 CNC控制器总体结构设计

通过对数控系统的功能划分,将该系统分成3个基本层次:界面层、控制层和设备层,分别提供人机界面操作、系统功能控制以及与控制部件通讯的设备接口。控制器硬件平台总体框架如图2所示。在本系统中界面层和控制层都是由处理器OMAPL138来进行控制,设备层与其他层的连接操作通过FPGA逻辑实现。

图2 数控系统平台总体框架

4 CNC控制器硬件结构设计

控制器在硬件结构上划分为核心板和基础板。核心板包含主控芯片OMAPL138及其外围模块,基础板包含FPGA芯片及其外围模块。核心板通过针脚连接完全嵌入在基础板上,而且多核芯片有不同的主频系列,并且管脚相互兼容[7],这样即可实现系统的模块化设计,也方便系统的硬件升级换代,满足不同系统的需求。

4.1 核心板硬件结构

核心板由OMAPL138处理器及其外围模块组成。外围模块有:电源模块、时钟模块、复位模块、存储模块和JTAG接口模块[8]。结构框图如图3所示。

图3 核心板及其外围模块结构图

(1)电源模块:因为内核和I/O都需要供电,并且对I/O的供电电压不同,所以采用TPS65032芯片作为电源电路的主芯片,该芯片是+5V输入,输出提供OMAPL138外设及内核多种形式电压需求。

(2)时钟模块:包括系统时钟和高精度的实时时钟。为OMAPL138系统时钟提供24MHz的外部晶振;为CycloneII时钟提供50MHz的外部晶振;为实时时钟提供32.768MHz的外部晶振;通过PLL(逻辑锁相环)的分频和倍频,提供系统及同步接口所需要的时钟信号。

(3)复位模块:根据电源芯片输出的复位信号或者复位按钮的动作,通过逻辑芯片输出复位信号,进行系统的复位。

(4)外部存储模块:为满足高性能数控系统对存储空间的需求,外扩了NandFlash和DDR2。NandFlash主要用于存储启动代码、操作系统内核映像、NC代码和应用程序,DDR2中主要用来存储程序运行时的指令及数据。

(5)JTAG接口:仿真器的JTAG接口都满足IEEE1149.1标准[9-10],与仿真器上的接口一致。本文中的JTAG接口电路也是采用14个引脚的接口,实现对芯片的测试、在线编程及对程序的调试。

4.2 基础板硬件结构

基础板由FPGA芯片及其外围模块组成。外围模块有:电源模块、网络通信模块、液晶显示模块和通用的输入输出接口模块。结构框图如图4所示。

图4 基础板及其外围模块结构图

(1)电源模块:基础板上布置2个独立的24V电源,分别为核心板和基础板上的I/O扩展模块供电。

(2)网络通信模块:采用以RJ45通信协议为基础的网络通信,实现数控系统的网络控制,利用MII(Media Independent Interface介质无关接口)实现微处理器对物理层的控制。

(3)液晶显示模块:采用16位总线收发器,进行电平信号变换。同时采用触摸屏控制器,对输入信号进行控制,控制器通过SPI接口和微控制器进行通信[11]。

(4)通用输入输出接口模块:主要包括USB接口、RS232接口、RS485接口。

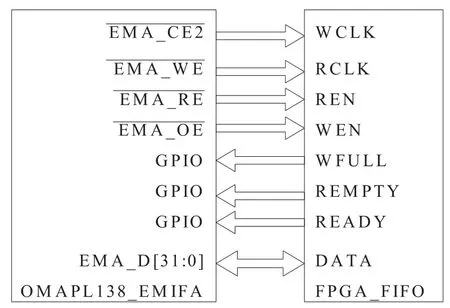

4.3 OMAPL138与FPGA的接口电路

OMAPL138内部集成的EMIFA控制器,共支持4个大小32M异步外部存储器,可以通过配置外接不同类型的存储设备,此处就是将CE2分配给FPGA作为OMAPL138的外部存储器进行使用,使得DSP和FPGA之间可以方便的进行大数据量的数据传输。引脚连接如图5所示。

图5 OMAPL138和FPGA接口电路图

(1)EMIFA的接口分析

片选信号EMA_CE2作为FPGA端的写时钟信号,写使能信号EMA_WE作为FPGA端的读时钟信号,读使能信号EMA_RE和FPGA端读使能信号相连,使能信号EMA_OE和FPGA端写使能信号相连,在DSP端选取3个通用GPIO作为握手信号和FPGA相连,最后将双向数据总线接口相连。在EMIFA的寄存器配置后,当EMA_CE2和EMA_RE同时为低电平时,表示DSP开始读取FPGA的FIFO,当EMA_CE2和EMA_ WE同时为低电平时,表示DSP开始往FPGA的FIFO里面写数据。

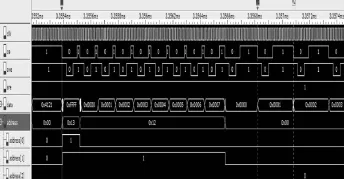

(2)通过EMIFA接口的读写时序图

图6 EM IFA写时序图

根据对EMIFA引脚的分析,在CCS中编写测试程序,向FPGA的FIFO中传输连续的数据。通过时序图可以看出(图6),EMIFA工作在100MHz的时钟下。通过FPGA端的地址解析模块,先向地址0x13发送数据0xFFFF初始化FIFO,再向地址0x12中写入计数数据,当计数到7以后,往地址0x00中写入连续增加的FIFO存储数据,该数据传输稳定,并且数据传输速率达到10mbps,可以满足数控系统对数据传输速率的要求。

5 总结

通过分析CNC系统的现状及存在的弊端,提出采用多核芯片OMAPL138作为高性能数控系统的硬件载体,并分析了该芯片用于数控系统的优势。给出了基于多核芯片的嵌入式开发平台总体框架设计及主要模块的设计,板级间的控制连接方案并实验验证了该方案满足数据传输速度要求。该CNC控制器方案集成度高、成本低、具备高性价比及市场竞争力,非常适合于实际工业产品开发。

[1]周祖德,龙毅宏,刘泉.嵌入式网络数控技术与系统[J].机械工程学报,2007,43(5):1-7.

[2]Texas Instruments.OMAP-L138 Applications Processor System Reference Guide[R].2009.

[3]陶宇.共享内存的几点总结[EB/OL].http://www.embedu.org/Column/Column250.htm.

[4]Texas Instruments.Building DSPLINK Applications version 1.65.00.02,2010.

[5]Altera.Cyclone II Device Family Data Sheet[R].2008.

[6]周凯.PC数控原理、系统及应用[M].北京:机械工业出版社,2006.

[7]赵艳秋.X86、ARM争夺嵌入式市场软件将是致胜砝码[N].中国电子报,20090709期(第5版).

[8]Texas Instruments.SEED-DIM138[M/CD],2010.

[9]宋玥,高伟强,阎秋生.基于DSP-TMS320C6713控制系统的最小系统板的设计[J].现代电子技术,2008(4):41-43.

[10]周文,和敬涵,毛志芳.TMS320VC33最小系统硬件设计[J].电气时代,2005(6):126-127.

[11]朱品伟,乔学亮,陈建国.新一代TSC2046触摸屏控制器[J].单片机与嵌入式系统应用,2005(10):51-53.

(编辑 李秀敏)(编辑 李秀敏)

The Embedded CNC Eontroller Hardware Platform Design Based on OMAPL138

ZUO Xu-hui,GAO Wei-qiang,ZHANG Wei-wen

(College of Mechanial and Electronic Engineering,Guangdong University of Technology,Guangzhou 510006,China)

In view of the shortcomings of traditional CNC based on PC and the card of dedicated motion controller,as well as ARM and DSP multi-processor in lack of communication.Proposed a embedded processing scheme based on multi-core heterogeneous OMAPL138 processor,and construction of a CNC controller hardware system,while taking advantage of the field programmale feature of FPGA to complete controller extension module design.The design solves the issues which PC lacks of dedicated resource and realtime control,and solves the defects of data loss,error-prone and difficult to maintain in multiprocessor communication,and implements the modern CNC system demand of high performance,modularity,flexibility and openness.

CNC controller;multi-core heterogeneous;OMAPL138;FPGA;hardware platform

TH165;TG65

A

1001-2265(2015)01-0075-04 DOI:10.13462/j.cnki.mmtamt.2015.01.021

2014-03-31

广东省教育部产学研结合项目(2012B0911000283);省部产学研结合项目重点项目(2011A090200026);广东省教育厅研究生示范基地项目(2013JDXM29);广东省数控一代项目(2012B011300046,2012B011300070)

左旭辉(1987—)男,合肥人,广东工业大学硕士研究生,研究方向为数控技术,(E-mail)victory.zxh@163.com。