基于PIC及FPGA的简易信号分析仪设计

白炳良,王灵芝

(闽南师范大学,福建 漳州 363000)

基于PIC及FPGA的简易信号分析仪设计

白炳良,王灵芝

(闽南师范大学,福建 漳州 363000)

高速数据采集与信号分析是信号分析仪的关键。设计以PIC16F877A单片机为核心,DA芯片MCP4922及可变增益放大器AD603构成程控放大电路;CCP模块实现频率测量;AD转换器AD9288及FPGA实现高速实时数据采集,并由LCD液晶显示被测数据及波形。由单片机读取FPGA中FIFO的缓存数据,实现对正弦波、三角波、方波等幅值、电压真有效值的测量及信号波形判断,实验效果实用良好。

高速数据采集;单片机;现场可编程门阵列;FIFO技术;高速模数转换器;程控放大电路

随着微电子技术和计算机技术的不断发展,信号的分析变得越来越重要,信号分析仪是一种可以用来观察、测量、记录各种瞬时电压,并能以波形方式显示其与时间关系的电子测量仪器。它能说明信号的许多特性参数:频率、幅度、真有效值等,并能对输入信号波形自动识别。

高速实时的数据采集经模数转换后,必须要求具有与之匹配的高速缓存器件,传统的数据采集方案已不能满足高速实时数据采集应用,因此需要设计高性能的数据采集与处理系统[1]。由于单片机指令周期及数据处理速度的问题,无法满足高速实时数据采集,FPGA具有高的时钟频率、运行速度快、功耗低、组成灵活等特点[2-3]。因此设计了利用单片机、高速AD、FPGA等构成信号分析仪:实现周期信号频率范围为20 Hz~250 KHz、输入电压范围为0.05 Vpp~10 Vpp的情况下,系统能完成对正弦波、三角波、方波三种输入信号相关参数的测量并显示波形。

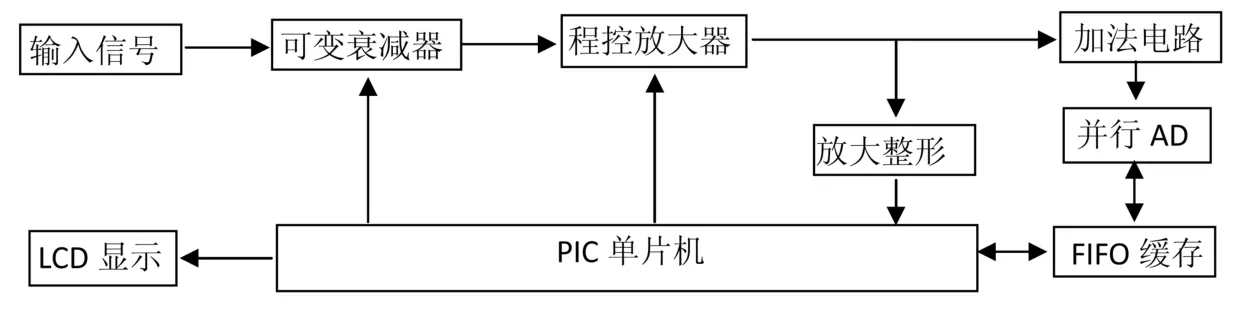

图1 系统框图

1 系统设计框图及工作原理

系统框图如图1所示。采用PIC16F877A单片机作为系统控制核心。可变衰减器由继电器、电阻网络及跟随器实现11或101信号变比;由12位DA转换器MCP4922、AD603组成的程控放大器;放大及整形电路将待测信号转换为矩形波,由单片机的CCP模块实现频率测量;程控放大器的输出信号与一直流分量由加法器实现叠加,使待分析的信号均处于y轴正半轴;由高速并行AD芯片AD9288、可编程逻辑器件FPGA中的FIFO模块实现对输入信号至少一个周期数据的存储,单片机根据需要实时读取FIFO中的数据,这样解决了慢速CPU与快速数据的读写问题;单片机对读取的数据进行处理,实现在LCD液晶屏上显示输入信号波形、峰峰值、频率、真有效值等。

2 硬件设计与分析

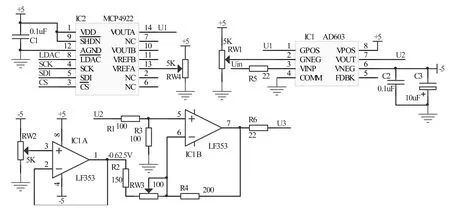

2.1 程控放大器

AD603是一个压控型的可变增益放大器,VINP为信号输入端,它的增益的调整与其1脚和2脚的电压差VG有关,当-0.5 V<VG<0.5 V时,增益(dB)与其电压差VG(V)之间满足线性关系: Gain(dB)=40 VG+G0,当5脚和7脚断开时,G0=30,所以,Gain(dB)=40 VG+30,即增益的范围为10~50dB[4]。图中MCP4922是个双通道12位的数模转换器,5 V电压由5K电位器调节A通道参考电压VREFA,MCP4922采用SPI总线方式与PIC通信,由VOUTA端可输出数控模拟电压U1。从而实现程控放大并由VOUT端输出U2,见图2。

图2 程控放大器

由IC1A与IC1B组成的加法器是使待分析的信号均处于y轴正半轴,其输出信号U3送AD转换。

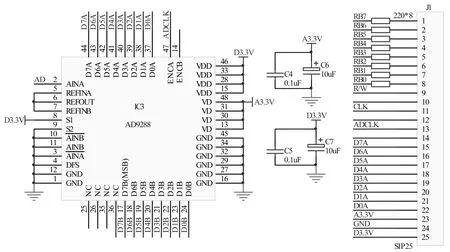

2.2 并行AD转换器AD9288及FPGA模块

由于待分析输入信号频率为20Hz~250KHz,对波形离散化采样及存储时,采样速度必须足够快才能采集到完整正确的信息,所以系统采用高速并行AD芯片AD9288对输入信号进行实时采样。

如图3所示,AD9288是一款100Msps采样速率的双通道8位高速模数转换器,内部由两个跟踪/保持放大器,两个A/D变换器,一个逻辑控制器,两个时钟模块,一个内部参考电压模块和两个数据输出模块组成。当S1、S2为低电平时,A、B通道处于STANDY,则A/D变换器不进行采样量化编码,当S1为高电平,S2为低电平时,AD9288在编码时钟的控制下进行工作。A通道的数据输出送cycloneⅡ系列芯片EP2C8Q208C8N中FIFO的数据线实现信息存储[5]。

FIFO为先进先出的存储器,速度高,存储方便。FIFO中的数据是队列结构,会出现溢出现象。当向一个满的FIFO中写入数据时,就会把最新进入的数据排挤出去,存入存储器中。在CPU设计、高速数据采样存储、显示缓存、高速通信缓存等方面有重要的应用[3]。系统根据不同频率的信号,选择不同的采样率将数据存储于FIFO;存满后等待PIC的读写信号和时钟信号,按照FIFO的先进先出的顺序读取FIFO存储的数据。

FIFO数据线经220Ω电阻后接到单片机RB0~RB7,经过读写信号R/W和时钟信号CLK与单片机进行相互通信。D0A~D7A AD9288的8位并行输出口,将其采样到的数据送入FIFO存储器中。同时,FIFO模块的输出时钟ADCLK控制AD采样率,使其保证采样到的数据至少有一个周期的信号波形。

图3 并行AD与FPGA及单片机接口

3 软件分析

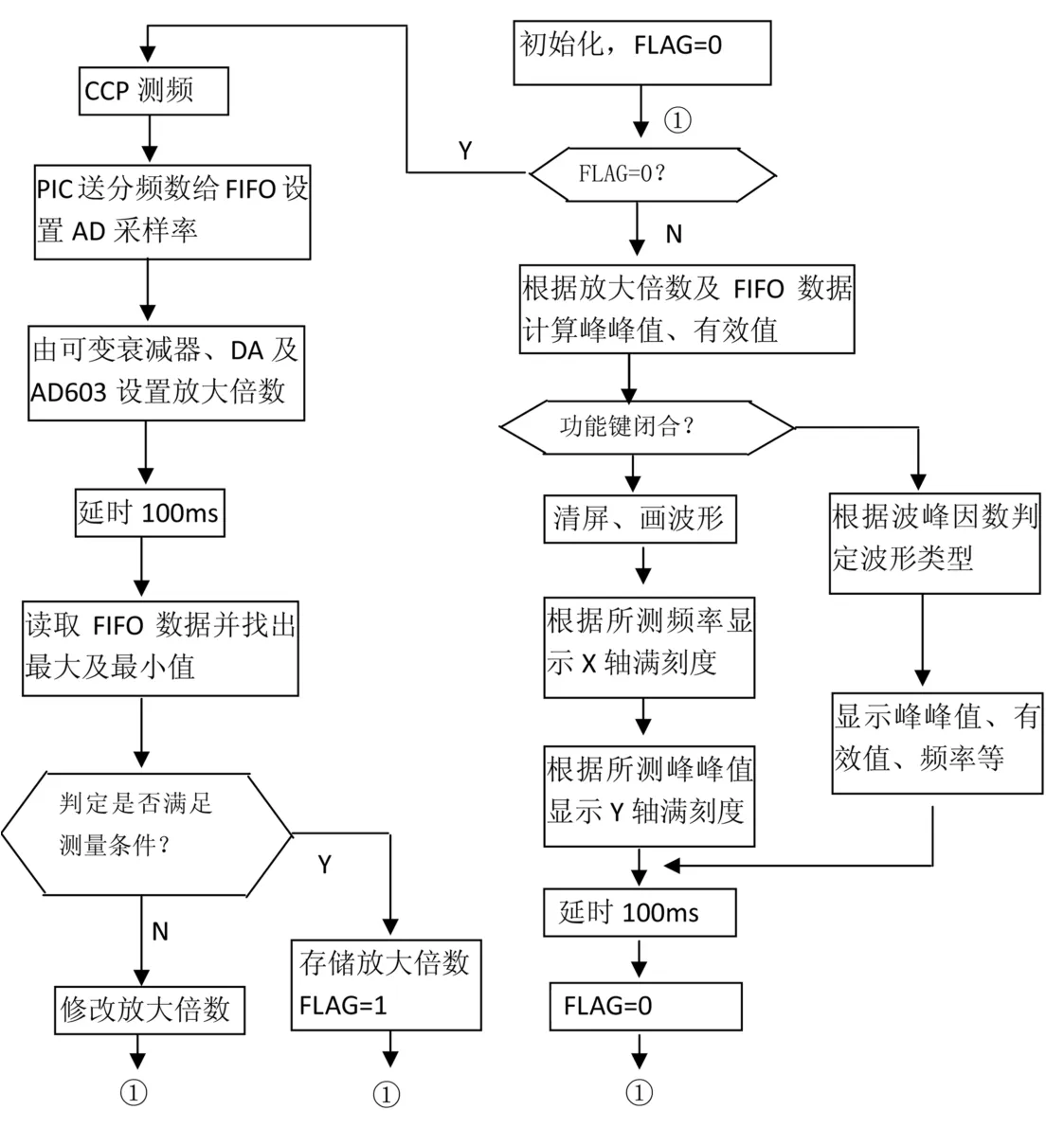

图4为系统主流程图。程序分为两个分支,一个是自动搜索合适的倍率,一个是信号参数计算和显示(参数显示与波形显示由功能键控制),两个分支自动切换。

图4 系统主流程图

自动搜索合适的倍率是通过判断采集的数据中最大值是否在所要求的范围内,如果太大,可通过降低MCP4922的输出电压,降低AD603的增益,反之,则增大其增益,然后再重新测量频率和采样信号数据,直到满足条件。

3.1 单片机与FIFO协议

单片机与FIFO数据存储器,通过一个读写位和八个并行数据位分时复用实现通信。当单片机需要向FIFO写数据时,是根据CCP模块测得的频率,分别由这八个数据位送分频系数、使能分频器、使能FIFO三组控制信号。当从FIFO读取数据时,单片机也是从这八个数据位读取。

3.2 真有效值测量方法

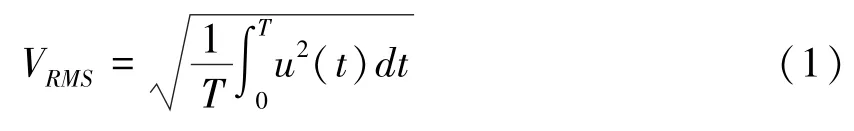

交流信号的有效值就是方均值,对于周期为T的信号u(t),其有效值为

将信号进行离散化(T=n×ΔT),可以得到:

由上式可计算出真有效值[6-7]。

3.3 波形判断

由波峰因数判断输入信号的波形。波峰因数=峰峰值/有效值,三角波的波峰因数为,正弦波的波峰因数为,方波的波峰因数为1。因此,根据AD采样的数据计算出信号峰峰值和有效值,从而判断出输入信号的波形[8-9]。

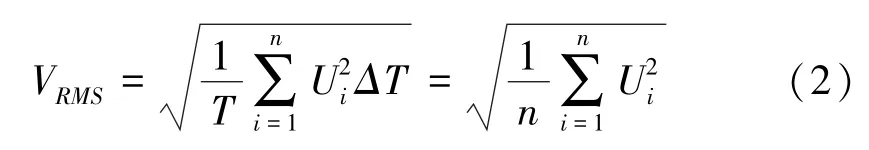

4 测量结果

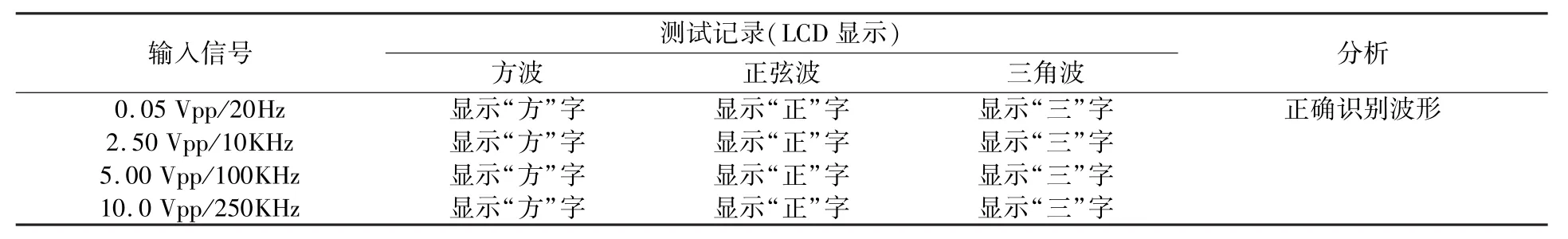

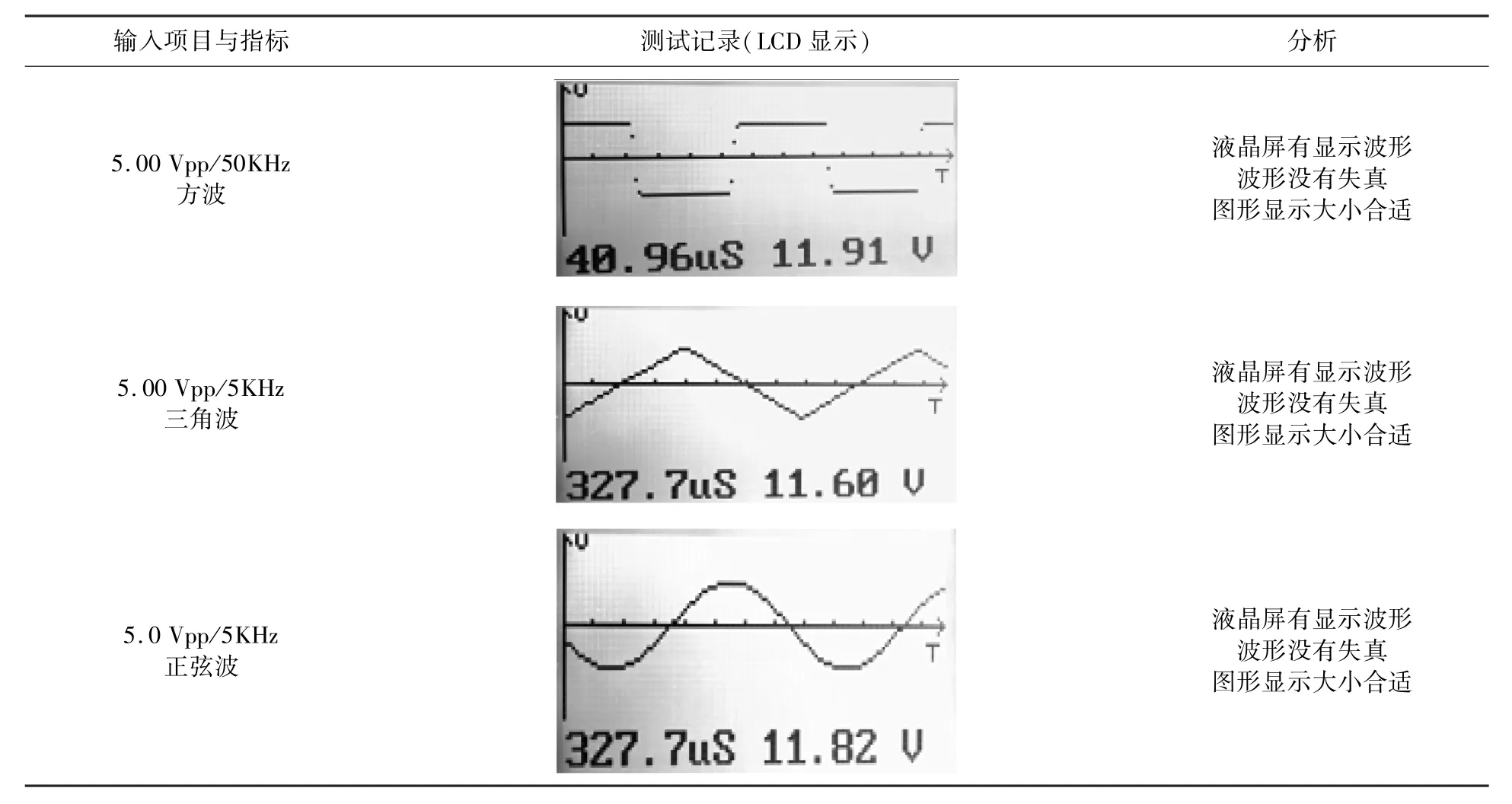

表1-3为不同条件下各输入信号的测试情况,效果理想。

表1 峰峰值和有效值测量记录表

表2 波形识别测试表

表3 信号波形测试表

5 结 论

系统可正确地测量输入信号的各项参数和显示波形,实验验证了该方案的可行性,实现高速AD数据采集、FIFO及PIC单片机三者的有机结合,该系统具有硬件设计简洁,处理速度快等优点,可为高速数据采样存储等提供借鉴,具有较强工程实践意义。

[1] 韩国荣,吴长瑞,张新胜.FPGA在高速实时信号采集系统中的应用[J].测控技术,2012,31(5): 60-67.

[2] 邵磊,倪明.基于FPGA的高速数据采集系统设计与实现[J].计算机工程,2011,37(19):221-223.

[3] 张秋云,王黎,高晓蓉,等.基于FPGA的高速实时数据采集系统设计[J].现代电子技术,2012,35(7): 70-76.

[4] 钟艳娥,黄顺,赵少武.放大器增益的智能控制[J].中山大学研究生学刊:自然科学、医学版,2012,33(1):106-112.

[5] 繆军同,鲁新平.模数转换器AD9288及其应用[J].山西电子技术,2006,(5):43-49.

[6] 邱玉春.一种采用单片机实现的基于离散积分的真有效值测量方法[J].工业控制计算机,2012,25(8):134-135.

[7] 冯乔春.真有效值的测量及应用[J].云南电力技术,2008,36(3):14-15.

[8] 杨幼桐.基于单片机与传感器的金属载胀系数测定[J].大学物理实验,2013(4):40-43.

[9] 白炳良,周锦荣.基于单片机的开关电源并联供电系统的设计[J].大学物理实验,2013(6):58-60.

Designed of the Simple Signal Analyzer Based on PIC and FPGA

BAI Bing-liang,WANG Ling-zhi

(Minnan Normal University,Fujian Zhangzhou 363000)

High-speed data acquisition and signal analysis is the key for signal analyzers.With PIC16F877A microprocessor as the core,DAC MCP4922 and variable gain amplifier AD603 as remote control amplifier,CCP module for frequency measuring,ADC AD9288 and FPGA chip to realize high-speed real-time data acquisition,and LCD displayer to display the measured data and waveforms.The practical result is fine for the signal analyzer.

high speed data acquisition;MCU;FPGA;FIFO;high-speed ADC;remote control amplifier

TN919

A

10.14139/j.cnki.cn22-1228.2015.01.005

1007-2934(2015)01-0014-05

2014-09-15

福建省教育厅科技项目(JK2013028)